基于ADSP-BF537的无线视频传输方案

嵌入式设计应用

描述

基于ADSP-BF537的无线视频传输方案

无线通信技术和视频压缩技术的迅速发展,使得无线视频传输成为人们研究的热点。无线视频传输具有数据量大,实时性要求高,无线信道资源有限的特点。新一代的视频压缩标准H.264结合专用视频DSF芯片可以满足信源编码的要求。而处理数据量大,速度快,运算结构相对简单的FPGA适用于信道编码。基于以上考虑,设计了一个无线视频传输系统,并以发射端ADSP-BF537作为控制器,配置FPGA和进行数据通信。

1 总体结构实现方案

系统硬件的实现方案如下:

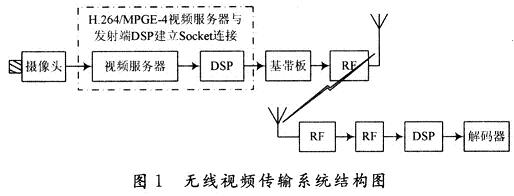

发送端由摄像机、专用视频编码芯片、控制模块、基带模块、射频模块(RF)等部分组成。接收端由射频接收模块、控制模块、基站模块、专用视频解码芯片等部分组成。系统结构如图1所示。

视频编码部分使用基于DM642的H.264视频编码器。该芯片通过网口传输数据,输出的视频流是H.264格式,输出图像的分辨率范围为176×144~702×576,而且可以根据具体需要修改码流和帧率。

控制模块使用ADI公司的ADSP-BF537作为主要芯片。其主要作用是完成FPGA的配置、接口控制、通信链路的建立(视频流数据的传输)。

基带模块以Xilinx公司Spartan3 400万门级芯片的FPGA作为主要芯片。FPGA完成整个基带信号处理,包括信道编码、OFDM调制、滤波等。

射频模块由发射单元、接收单元、频率合成单元、外置15 W功放等四部分组成,采用差分I,Q信号调制、解调,双向传输。发射单元将I,Q差分输入经调制芯片调制成340 MHz的射频信号,经功率控制、功放、隔离器送往环行器、天线;通过收发电平控制进行发送和接收的切换;接收单元对接收信号进行滤波、低噪声放大器后送I,Q解调芯片解调出差分的I,Q信号,并进行RSSI检测和AGC控制。工作模式采用半双工模式;频率合成单元为发射单元提供340 MHz本振信号,为接收单元提供680 MHz本振信号。

2 控制模块中DSP与FPGA数据通信

由于FPGA基于SRAM工艺,上电后数据会丢失。一般FPGA除了采用边界扫描方式JTAG下载外,更多采用与FPGA相对应PROM芯片静态配置,这种配置方式由于PROM容量小,价格昂贵,易于烧坏等缺点,在产品化之前一般不予采用,更可取的方法是采用控制器动态配置FPGA,比如单片机、DSP。同时,视频服务器通过网口发送视频数据,需要一个控制部分前向网口接收视频服务器的数据,后向配置FPGA,发送视频数据。基于以上考虑,整个系统中控制部分均由ADI公司的Blackfin系列DSP BF537完成,DSPBF537通过接口与视频服务器和FPGA通信。

2.1 硬件平台

ADSP是ADI(Analog Device Inc.)公司推出的一系列高性能低功耗DSP芯片,而基于Blackfin处理器的ADSP-BF537具有接口丰富,性能优良,价格低廉等特点,并具有强大的多媒体数据处理能力。Blackfin处理器集成了一个由ADI公司和Intel公司联合开发的基于MSA(Micro Signal Architecture)的16/32位嵌入式处理器,支持32位RISC指令集,采用10级流水线,集成了两个16位乘法加速器,内核主频最高可以达到600 MHz。ADSF-BF537总线有一个以DMA控制器为中心的高速自主数据通道。DMA总线可以在存储器之间、存储器和外部接口之间快速地传递数据,并且可以和内核并行操作。ADSP的集成开发环境Visual DSP++中嵌入了实时操作系统内核VDK,适合多任务多线程的嵌入式操作。ADI还提供了一个用于Blackfin系列嵌入式处理器的轻量级TCP/IP(LwIP)协议栈端口,可以快速将一个独立的嵌入式应用联网。

2.2 硬件系统架构

DSP与视频服务器采用轻量级TCP/IP(LwIP)交互数据,这里不过多介绍。主要介绍DSP与FPGA连接。由于FPGA基于SRAM工艺,掉电后数据会丢失。采用的方法是将作用于FPGA的通信基带算法文件存储在DSP的FLASH中。一般调试时,DSP及FPGA都需要从PC机通过JTAG口进行程序的下载。但当系统程序已经调试完毕,当需要到户外进行测试或作为产品使用时,针对系统调试的方便性,采用DSP自启动及配置FPGA部分。

ADI公司的ADSP-BF537上电后启动方式一共有7种。本设计中采用的DSP上电从16位FLASH启动,启动程序采用Analog公司提供的烧写启动FLASH的程序。第一次上电时,利用JTAG,结合ADSP自带工具“FLASH Programmer”将写好的DSP程序烧入FLASH中。并且将FPGA的配置文件(.bit格式)读到缓存,通过DSP烧写到FLASH的Bankl和Bank2中,把Bank0用来做DSP自启动。断电复位后,启动过程如下:

(1)BF537从FLASH引导启动,完成DSP板级初始化。

(2)FPGA的配置文件动态加载到FPGA中。

(3)用DSP的GPIO端口对FPGA的时钟和数据配置专用引脚进行模拟时序,即完成对FPGA的动态配置。

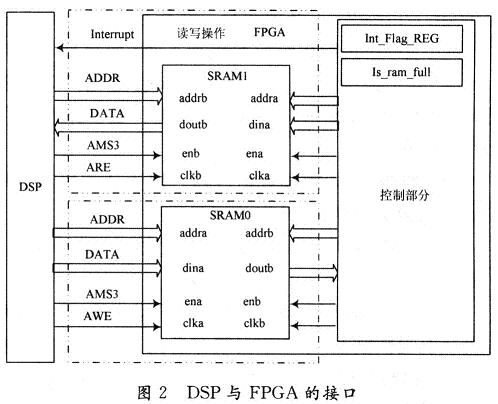

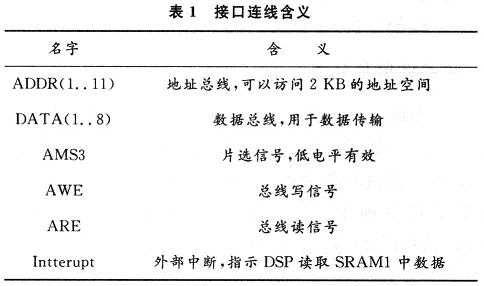

在启动过程完成后,DSP与视频服务器进行Sock-et连接,接收压缩的视频码流,并送到FPGA进行基带部分的处理。DSP与FPGA的接口部分如图2所示。

图2中DSP通过自身的外部总线与FPGA相连,FPGA内部实现了两个2 KB的异步存储器SRAM0,SRAM1,对存储器的访问满足DSP外部总线的时序要求。图2中接口连线含义如表1所示。

对DSP而言,DSP通过外部总线连接到SRAM0和SRAM1,这就相当于外扩了两个外部RAM,DSP可以自由地访问它们。图2中的SRAM0,SRAM1分别用于DSP发送数据和接收数据。SRAM0和SRAM1本身是双口RAM,可以供DSP和FPGA访问,就是通过这种共享存储器的方式完成数据交互。

2.3 软件系统结构

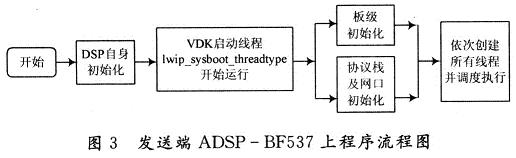

相关程序是用含有VDK(Visual DSP Kernel)的DSP软件开发工具Visual DSP开发的。VDK是一种带有API函数库的实时操作系统内核,它具有任务调度和任务管理功能,一共支持32个任务。VDK是整个软件的基础,所有其他的程序都运行在该Kernel上。程序流程图如图3所示。

上电或复位后,DSP自启动后VDK启动线程lwip_sysboot_threadtype开始运行。在线程lwip_sysboot_threadtype中进行板级初始化和Lwip协议栈和网口初始化,其中板级初始化包括FPGA初始化,EBIU初始化,MDMA初始化,FLAG初始化。接下来创建下面几个线程:

(1)数据传输:视频数据传输。用于从编码器获取编码后的视频数据流,并存储到缓冲区中。

(2)FPGA中断:视频数据发送中断;MDMA中断。

DSP首先通过Socket与视频服务器连接,从视频服务器获取视频数据,并将数据缓存后按照特定的格式打包,等待FPGA触发视频数据发送中断。中断触发后,DSP启动MDMA将一帧大小的数据发送给FPGA发送缓冲区。当MDMA操作完成后,触发MDMA中断,将帧头写入FPGA发送缓冲区的头两个字节。FPGA将接收的数据进行基带算法处理后再将数据发送给射频部分,之后FPGA再触发视频数据发送中断,告诉DSP可以下一帧的发送,于是又启动MDMA,如此循环。

3 实验结果和分析

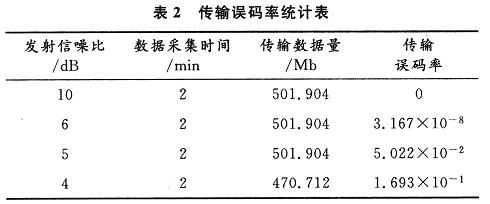

对系统在不同的信噪比的环境中传输的误码率进行了测试。测试方法如下:将发射机的输出端口通过数据排线与逻辑分析仪相连,逻辑分析仪将采集到的一帧发射信号送到PC中用Matlab软件对其加上噪声,得到信噪比固定的信号。将这个信号导人信号源中进行不间断循环发送给接收端的输入端口。接收机接收信号进行解调并将解调出的数据传给PC以统计误码率。测试结果如表2所示。

4 结 语

设计了一种无线视频传输系统的方案,并对其中发射部分的数据通信过程做了详细阐述。从硬件架构和软件设计两方面说明了数据在视频服务器、DSP和FP-GA之间的传递过程。其中ADSP-BF537作控制器,成功完成了动态配置FPGA和通过网口传送视频数据的功能。该方案很好地满足了大数据量,实时性的数据处理和结构灵活,模块化设计相结合的要求。同时DSP+FPGA的数字硬件系统开发周期较短,系统容易维护和扩展,适合实时信号处理,使方案有更广泛的应用。

- 相关推荐

- 热点推荐

- 视频传

-

EE-262:面向ADSP-BF533用户的ADSP-BF537 Blackfin亮点2025-01-06 395

-

ADSP-BF537黑线Processor硬件参考2021-06-17 708

-

求一种基于ADSP-BF537的SOC验证方案2021-06-03 1393

-

适用于ADSP-BF537 Blackfin处理器的EZ-KIT Lite2021-05-26 754

-

ADSP-BF537 Blackfin-SoP-SoP/SoP-Processor硬件参考2021-05-24 699

-

ADSP-BF537 EZ-KIT精简版入门<sup>®</sup>2021-05-21 773

-

ADSP-BF537 EZ-KIT Lite<sup>®</sup>评估系统手册2021-05-19 826

-

EE-262:ADSP-BF537 Blackfin®针对ADSP-BF533用户的亮点2021-04-26 953

-

ADSP-BF537 EZ-KIT Lite电路板设计数据库2021-04-13 820

-

ADSP-BF534/ADSP-BF536/ADSP-BF537:Blackfin嵌入式处理器数据手册2021-03-19 1016

-

评估ADSP-BF537 Blackfin处理器的ADZS-BF537-EZLITE,ADSP-BF537 EZ-KIT Lite评估系统2019-03-08 2140

-

ADSP-BF537 具备嵌入式网络连接能力的Blackfin处理器2019-02-22 1078

-

无线视频传输系统的方案设计与结果分析2017-12-12 2398

全部0条评论

快来发表一下你的评论吧 !