传统与创新设计的区别有多大?

电子说

描述

对新设计方法的需求

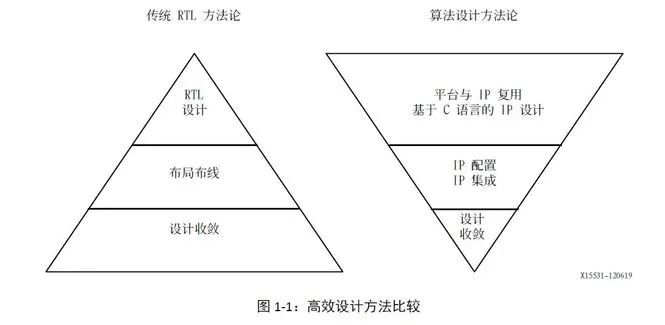

当今日益复杂的电子产品中所使用的先进设计正在不断对器件密度、性能和功耗的极限发起挑战,同时也对设计团队提出了挑战,要求他们在限定的预算内按时完成设计目标。 应对这些设计挑战的高效方法之一是将更多时间投入到更高的抽象层,这样即可最大程度缩短验证时间和提升工作效率。对新设计方法的需求在下图中得到了充分体现,其中每个区域的面积分别代表设计流程中每个阶段的开发工作量的比例。

对传统 RTL 方法而言,大部分工作主要耗费在实现的细节工作上。

在高效设计方法中,大部分工作主要集中于设计系统和验证构建的系统是否正确。

关于本指南

赛灵思可编程器件含有数百万个逻辑单元 (LC),并且集成的现代复杂电子系统也与日俱增。本高效设计方法指南提供了一整套最佳做法,旨在于较短的设计周期内完成此类复杂系统的创建。

本方法指南主要围绕下列概念展开:

使用并行开发流程来提供有价值的差分逻辑,使您的产品在市场中脱颖而出,并提供 shell 用于将此类差分逻辑与生态系统其余部分有机整合。

广泛使用基于 C 语言的 IP 开发流程实现差分逻辑,使仿真速度较 RTL 仿真成倍增长,并提供时序精确且经过最优化的 RTL。

使用现有预验证的块级和组件级 IP 来快速构建 shell,将差分逻辑封装到系统中。

使用脚本来实现从设计精确性验证到 FPGA 编程在内整个流程的高度自动化。

本指南中的建议是根据多年来广泛收集的专家级用户经验总结而成的。与传统 RTL 设计方法相比,这些建议持续不断实现了各方面提升,包括:

1) 设计开发时间加快 4 倍。

2) 衍生设计开发时间加快 10 倍。

3) 结果质量 (QoR) 提高 0.7 倍到 1.2 倍。

虽然本指南以大型复杂设计为重点,但其中论述的做法也同样适用于并已成功应用到下列各类设计中:

● 数字信号处理

● 图像处理

● 视频

● 雷达

● 汽车

● 处理器加速

● 无线

● 存储

● 控制系统

传统方法与高效设计方法的区别

传统设计方法

传统设计开发首先是由有经验的设计人员预估如何使用新技术来实现自己的设计、完成寄存器传输级(RTL) 的设计捕获、通过综合和布局布线执行一些尝试以确认自己的预估是否正确,然后继续开展设计其余部分的捕获工作。在此过程中通常需要逐一对每个块进行综合,以重复确认设计的实现细节是否可接受。 确认设计能否提供所需功能的主要方法是对 RTL 进行仿真。由于 RTL 可提供极为详细的位精度和周期精度描述,虽然这些描述精度极高,但此流程仍较为缓慢且易于出错。仅当在 RTL 中捕获设计中的所有块之后才能执行完整的系统验证,这往往会导致对 RTL 进行反复调整。在系统中的全部块验证完毕后,即可对其进行集中布局布线,此时才能完全确认先前预估的时序和面积的精确性,或者发现其中不精确的地方。这也往往会导致对 RTL 进行更改、重新启动系统验证以及重新进行实现。 设计人员现在通常需要在给定工程中实现数十万行 RTL 代码,把大部分设计时间都用在实现的细节工作上。如图 1-1 所示,设计人员把更多时间用在设计的实现上,而不是设计出使所有产品保持竞争力所需的新颖创新的解决方案。

无论是采用更新的技术以提升性能,还是采用更缓慢的技术以提供更具竞争力的定价,都意味着必须重写大部分 RTL,并且设计人员必须重新实现寄存器间的大量逻辑。

高效设计方法指南

高效设计方法沿袭了传统 RTL 方法的基本步骤,如图 1-1 所示。但是,它能够让设计人员把更多时间用来设计增值解决高效设计方法,该方法的主要特性包括:

提出了随差分逻辑并行开发并验证的 shell 概念。此 shell 包含差分逻辑,用于捕获独立设计工程中的 I/O 外设和接口。

使用基于 C 语言的 IP 仿真,使仿真时间相比于传统 RTL 仿真缩短多个数量级,为设计人员提供了设计理想解决方案的时间。

借助赛灵思 Vivado Design Suite 利用基于 C 语言的 IP 开发、IP 复用和标准接口,实现时序收敛的高度自动化。

使用 Vivado IP 目录轻松复用您自己的块级和组件级 IP,还能轻松获取赛灵思 IP,这些 IP 均已验证且已知在技术中能够有效。

高效设计方法中的所有步骤都能交互执行,也可使用命令行脚本来执行。所有人工交互的结果均可保存到脚本,实现从设计仿真直至 FPGA 编程的整个流程的完全自动化。根据您的设计和 RTL 系统级仿真的运行时间,该流程通常在任何 RTL 设计仿真完成之前即可在开发板上生成 FPGA 比特流并对设计进行测试。

创建衍生设计时,效率提升将更为明显。基于 C语言的 IP 能够与不同器件、技术和时钟速度轻松对应,就像更改工具选项一样简单。完全脚本化的流程与通过 C 语言综合实现的自动时序收敛意味着能够快速完成衍生设计的验证和组装。

责任编辑:lq

-

电源技术创新设计专辑2012-08-17 4914

-

工程师创新设计宝典-基础篇2012-08-20 2053

-

PCB制板和打样的区别有哪些2020-03-18 4947

-

步进电机和伺服电机的区别有哪些2021-09-30 1726

-

TCP协议和UDP协议的区别有哪些?2021-11-12 5180

-

SPI对比QSPI的读写速度差别有多大?2023-10-12 789

-

请问ARM与单片机的区别有什么?2023-10-25 718

-

集成显卡与独立显卡的区别有哪些?2010-01-25 2605

-

整屏边缘融合与传统拼墙的区别有哪些?2010-02-21 601

-

电线与电缆的区别有哪些?2010-03-12 1678

-

颜料墨水,染料墨水,颜料墨水和染料墨水的区别有哪些?2010-03-18 1264

-

固态硬盘与普通硬盘的区别有哪些2017-09-18 1121

-

一体化微气象传感器与传统气象仪区别有哪些?2021-10-08 1226

-

CPU和GPU的区别有哪些2022-01-06 33852

-

液晶拼接屏和led显示屏区别有哪些2023-04-13 3811

全部0条评论

快来发表一下你的评论吧 !