芯片的总成本

电子说

描述

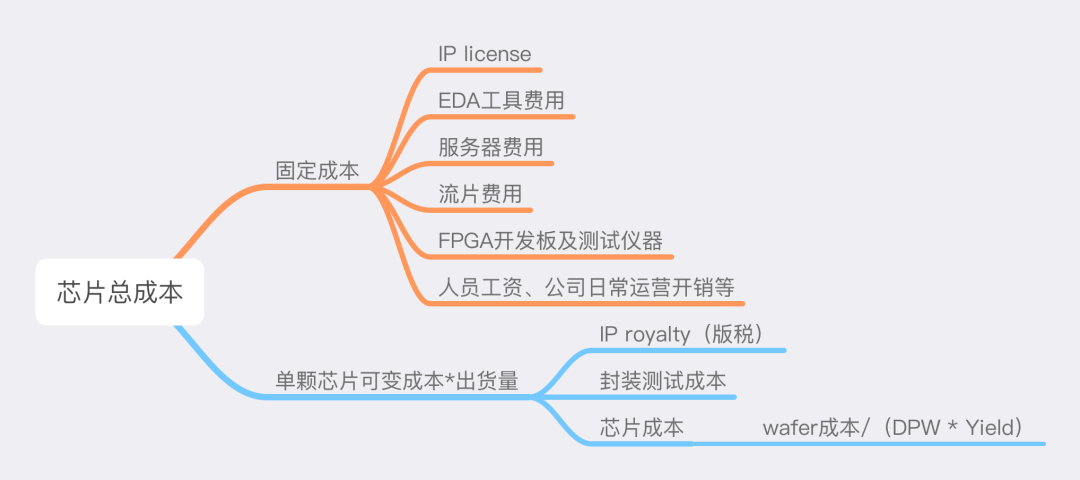

集成电路的成本一般分为两个部分,固定成本和可变成本。

总成本=固定成本 + 可变成本。

固定成本

固定成本包括,IP license费用,EDA工具的费用,服务器的费用,流片的MASK(掩膜版)的费用,FPGA开发板及测试仪器费用,封装测试费用,所有研发人员工资,市场、销售、房租、公司日常管理开销运营的等等费用。

固定成本与销售量也就是产品售出的数量无关,因为即使你产品最后生产出来了,但是卖不出去,你这部分钱已经花出去了,所以是固定要输出的成本。

可变成本

芯片的可变成本=单颗芯片可变成本 * 芯片出货量

单颗芯片的可变成本 = IP royalty (版税)+ 封装成本 + 测试成本 + 芯片成本

有些IP厂商收取专利费的模式,除了收取IP固定的授权费,而且等芯片出货后还按每个芯片收取费用,这就是IP royalty,按单芯片固定金额,更或者按芯片总价的百分比收取。

芯片成本

芯片成本 = wafer成本 / (DPW * Yield)

wafer就是晶圆,DPW(Die per wafer)每一个wafer上能够切割的die(芯片)的个数。理论上来说,每片wafer上芯片的个数可以用wafer的面积除以芯片面积,但是实际情况并不完全是这样,因为wafer是圆的嘛,芯片的是方的,你最边上的一圈边角料出来的芯片肯定是用不了的么。当然wafer的尺寸也是越来越大,所以每批生产可以得到更多的芯片。还与Yield良率有关,芯片从晶圆上切割下来,肯定有些是废片。合格的数量占晶圆上切割下来总数的百分比成为良率。

同一颗晶圆上出来的芯片,性能也不是完全一样的,我们都知道intel的芯片系列后缀都有很多标识,同样是i7,有些后缀性能就强,有些就弱,卖不同的价格。

经过粗略的计算,以上这些都加起来就构成了芯片的总成本。

几片石英玻璃=魔都一套房

其中最贵的部分就是流片了,流片就是试生产,先生产小批量的一部分,回片进行测试,保证功能没有大问题,小bug能用软件绕开就绕开,实在不行就做ECO,硅后ECO阶段会非常贵。然后就可以大规模的量产。

流片主要是贵在Mask,也就是掩模版,这个东西的原材料不值钱,但制造它的机器特别贵,所以到手的Mask十分贵,所以就产生了一种新模式来帮一些小公司或学术机构分摊成本,这个模式叫做MPW,全称为Muti Project Wafer意思是多项目晶圆,可以理解为拼多多的形式,大家一起拼单流片(不仅晶圆厂有专人负责这类业务,还有专业的中介公司,组织设计公司一起流片,当然前提是在同一种工艺下),而full mask是土豪公司独享的moment。Mask的贵,号称几片石英玻璃=魔都一套房,不是开玩笑的。

等芯片量产后,就可以根据出货量来分摊流片的成本,比如说,你mask的费用是1000万美金,但芯片的出货量有500万片,那么分摊到单个芯片的成本就是2美金。所以出货量越大,回本的速度就越快,甚至可以赚更多的钱。

点沙成金

也就是有一些说法,造芯片就像印钱,点沙成金嘛。当然这是理想的情况下。众所周知,芯片行业是一个竞争残酷而且薄利的行业,你的产品能晚竞争对手上市三个月,你可能就会丢掉非常多的市场份额,流片风险也非常大,如果失败,回来就是块砖头,所以我们说自己是搬砖的。再来一次,这就是要花成倍的钱。

真是顶着卖“白面”的风险,赚着卖白菜的钱。所以芯片行业的生存法则就是,行业老大吃肉,老二喝汤,剩下的只能喝西北风了。喝西北风居然还是个成语。

我们传统的芯片厂商引以为豪的就是first chip manufacture,可以理解为第一版量产,所以在IC设计工程上,通常是80%采用现有成熟的设计和IP方案,做20%的更新,万物基于”二八定律“么,除了第一版肯定是从无到有的全新。所以说芯片设计就是一种模式设计,从功能规则制定到最终流片及验证,若完全遵循一整套业内公认的设计方法学,芯片必然能够成功。

Designless-Fabless

半导体公司从传统的IDM走到Fabless模式,已经算是“轻资产”了,甚至现在还出现了很多芯片设计服务公司,简单来说,就是外包。这样的公司只需要承担人力成本,而不需要承担流片的风险。所以出现的这种新的模式,Designless-Fabless模式,由大厂或合作的方式定义芯片产品,然后由设计服务公司完成部分设计或验证,最后由大厂或合作公司自己承担流片成本。

结语

随着芯片公司也越来越多,再加上一些的互联网公司和系统厂商也进入半导体行业,对于我们普通的从业者来说,也算是好事,可能选择的机会会更多一点。

本文主要是从fabless设计的角度谈芯片成本,关于制造领域的了解并不多,希望多多交流,做芯片不易,情怀也可以谈,但同时也要保持冷静独立思考,我们的征途还是星辰大海。

责任编辑:lq

-

采用低功耗28nm降低系统总成本2012-07-31 0

-

采用低功耗28nm FPGA降低系统总成本2015-02-09 0

-

利用业界成本最低、功耗最低的FPGA降低系统总成本需要面对哪些挑战?2019-08-09 0

-

如何采用低功耗28nm FPGA降低系统总成本?2019-10-14 0

-

TPS54160DGQR芯片外围应用电路相关资料下载2021-11-17 0

-

Littelfuse入选Celestica 2012年“拥有总成本供应商奖计划”获奖名单2013-08-08 700

-

微电网运行总成本最低的规划方案分析2018-01-23 2325

-

降低芯片设计成本的方法有哪些?2018-10-05 6483

-

在PADS设计流程中使用DFM分析可降低成本2019-05-15 3918

-

提速降费不仅能够降低社会总成本还有利于推动电信企业加快转型升级2019-08-07 688

-

乐心手环 5中4颗主控芯片成本占总成本的42%2019-10-11 1500

-

芯片的总成本为什么那么贵?2020-10-21 4277

-

影响PCB总成本和可靠性的最大因素是什么2021-01-26 639

-

TPS54160DGQR芯片外围应用电路及成本2021-11-10 1075

全部0条评论

快来发表一下你的评论吧 !