AXI-Stream代码

描述

AXI-Stream代码详解

AXI4-Stream跟AXI4的区别在于AXI4-Stream没有ADDR接口,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时,允许无限制的数据突发传输规模。AXI4-Stream的核心思想在于流式处理数据。

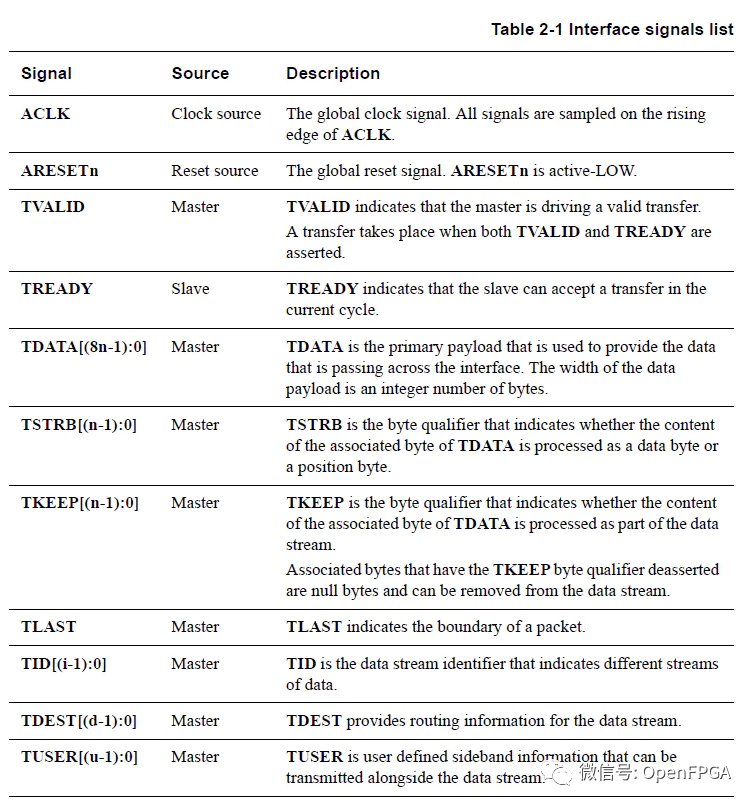

图 4‑58 AXI-Stream Interface

全局信号

1.ACLK 全局时钟信号,在上升沿时对信号采样。所有的输入信号都通过上升沿采集,所有的输出信号都在上升沿时变化。

2.ARESETn 全局复位信号,低电平有效。在复位期间,所有的xxVALID信号必须复位为低电平。其他的信号可以是任意值。

主机(master)控制的信号

3.TVALID 握手信号

4.TDATA 数据信号线

5.TSTRB TDATA的内容修饰符,用于指示是数据字节还是位置字节。初学者默认为1即可.

6.TKEEP TDATA的内容修饰符,用于指示是此字节是否为有效字节,和TSTRB配合使用。如下表。xilinx封装的ip中不使用此信号,所以默认为1。

| TSTRB | TKEEP | data type |

| high | high | 数据字节 |

| high | low | 位置字节 |

| low | low | 无效字节 |

| low | low | 保留 |

7.TLAST 置高表示本次流传输中的最后一个数据。

8.TID 表示不同数据流的数据流标识符。xilinx封装的ip中没有此信号。

9.TDEST 用于提供路由信息,xilinx封装的ip中没有此信号。

10.TUSER AXI4协议留给用户自定义的。xilinx封装的ip中没有此信号。

从机(slave)控制的信号

11.TREADY 握手信号

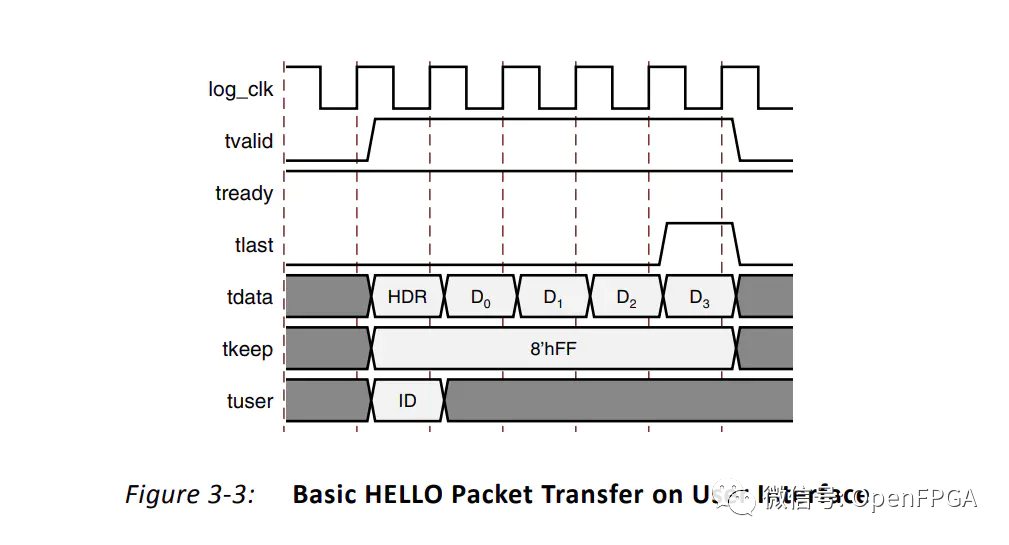

一个AXI-stream传输的时序图:

图4‑59 AXI-stream example

AXI4-stream主从交互仿真

lvivado创建工程,添加代码。

l编写仿真tb文件。

下图是AXI4-stream主从交互的时序图。

图4‑60 AXI4-stream主从交互的时序图

其中AXI-stream一般的数据传输过程如下:

1、首先slave将TREADY信号拉高,表示自己可以接收信号。

2、当master将TDATA,TKEEP,TUSER准备就绪之后,将TVALID拉高,传输开始。

3、其中TKEEP满足TKEEP[x] is associated with TDATA[(8x+7):8x],当其被拉高时表示这段数据必须传输到目的地。TSTRB表示该段信息是否有效。TUSER可以在传递时捎带用户信息。具体接口参照使用的AXI-stream接口器件,并非所有支持AXI-stream接口的器件都含有以上接口,其中的一些接口是可选的而不是必需的。

4、直到master将TLAST拉高,TVALID拉低,传输结束。

代码在这里:

链接:https://pan.baidu.com/s/1FprBYZ37FP-deT38pWzSwg

提取码:open

责任编辑:xj

原文标题:AXI-Stream代码详解

文章出处:【微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

-

Vivado HLS直通AXI Stream IP-Core如何分配2020-04-14 2326

-

请问可以使用AXI-Stream Broadcaster作为AXI开关吗?2020-05-07 2725

-

AXI-stream数据传输过程2021-01-08 2904

-

如何使用Xilinx AXI VIP对自己的设计搭建仿真验证环境的方法2022-10-09 5121

-

AXI4Stream总线的FPGA视频系统的开发研究2017-11-17 5513

-

自定义sobel滤波IP核,IP接口遵守AXI Stream协议2019-08-06 4784

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7541

-

Zynq中AXI4-Lite和AXI-Stream功能介绍2020-09-27 10077

-

ZYNQ中DMA与AXI4总线2020-11-02 5278

-

关于AXI4-Stream协议总结分享2022-06-23 3339

-

AXI4-Stream Video 协议和AXI_VDMA的IP核介绍2022-07-03 10918

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10919

-

AXI传输数据的过程2023-10-31 2348

-

一文详解Video In to AXI4-Stream IP核2025-04-03 3056

全部0条评论

快来发表一下你的评论吧 !