基于可编程逻辑器件实现多电平正交幅度调制系统的设计

可编程逻辑

描述

1 引 言

多电平正交幅度调制MQAM(Multilevel QuadratureAmplitude Modulation)是一种振幅和相位相结合的高阶调制方式,具有较高的频带利用率和较好的功率利用率。因为单独使甩振幅和相位携带信息时,不能最充分利用信号平面,这可由调制信号星座图中信号矢量端点的分布直观观察到。多进制振幅键控(MASK)调制时,矢量端点在一条轴上分布;多进制相位键控(MPSK)调制时,矢量点在一个圆上分布。随着进制数M的增大,这些矢量端点之间的最小距离也随之减少。而MQAM采用振幅和相位联合键控调制,他能充分利用整个信号平面,将矢量端点重新合理地分布,在不减小最小距离的情况下,增加信号的端点数;在相同信号端点数的情况下,矢量端点之间的最小距离增加。因此,MQAM是一种高效的调制方式,被广泛应用于中、大容量数字微波通信系统、有线电视网络高数据传输、卫星通信等领域。本文首先介绍了MQAM调制解调的基本原理,然后以64QAM为例,介绍了一种全数字实现的调制系统结构方案,并给出了解调器的具体FPGA实现方法及关键技术。

2 MQAM调制原理

所谓正交振幅调制,就是用两个独立的基带波形对两个相互正交的同频载波进行抑制载波的双边带调制,利用这种已调信号在同一带宽内频谱的正交性来实现两路并行的数字信息传输。MQAM信号的一般表达式为:

式(1)由两个相互正交的载波构成,每个载波被一组离散的振幅{Am),{Bm)所调制,故称这种调制方式为正交振幅 调制。式中T为码元宽度,m=1,2,…,L,L为Am和Bm的电平数。MQAM中Am和Bm振幅可以表示成:

式中:A是固定的振幅,dm,em由输入数据确定,dm,em决定了已调MQAM信号在信号空间中的坐标点。在调制过程中,载波的振幅与相位都发生了变化,因此,已调信号矢量星座图中每一个坐标点代表了一种编码组合,同时也代表了正交信号矢量合成后的不同的相位及电平,第i个信号可用数学描述为:

因此每一个坐标点也由Ai和φ i惟一确定。

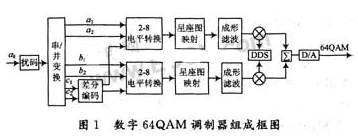

3 64QAM调制器系统设计

图1给出了全数字实现的64QAM调制器的电路原理结构。除D/A变换外,每个功能模块都用FPGA实现。扰码、串并转换和差分编码采用原理图的方法进行设计,电平转换及星座图映射采用查表法(LUT)进行设计。本设计的难点为成形滤波器和基于DDS的正交调制器实现,下面重点描述成形滤波器和基于DDS的正交调制器的实现方法。

3.1 成形滤波器的设计

为了让信号在带限的信道中传输,提高频谱利用率,通常在发送端把信号经过成形滤波器进行带限,由此就会引入码间干扰。为有效地减少码间干扰,按照最佳接收理论,收发基带滤波器应共轭匹配,设计时收发基带滤波器采用均方根升余弦滚降滤波器即能满足要求。

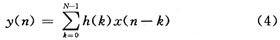

在实际电路设计中采用具有线性相位的FIR滤波器来实现均方根升余弦滚降特性的成形滤波器。一个N阶FIR滤波器的差分方程表达式为:

线性相位的FIR滤波器的系数是偶对称或奇对称的,利用系数的对称性可减少乘法器的数量,本系统采用N为偶数且系数偶对称的线性相位的FIR滤波器。滤波器系数是一个固定的值,根据均方根升余弦的冲击响应特性,利用Matlab软件可直接生成FIR数字滤波器系数hk(k=0,1,…,N-1)。所以滤波器的乘法都是固定系数的乘法。

本设计采用分布式算法(DA)原理,利用FPGA查找表代替乘法器来实现FIR滤波器,其基本思想如下:

假设输入信号数据位为B位,则滤波器在n时刻的第k个输入为:

从式(5)可以看出,FIR滤波器中乘加单元的运算是算法核心。如果建立一个查找表(Look Up Table,LUT),表中数据由所有固定系数(h0,h1,…,hN-1)的所有加的组合构成(和用sumb表示,6∈[0,B-1]),那么,用N位输入数据构成的N位地址去寻址LUT,如果N位都为1,则LUT的输出是N位系数的和,如果N位中有0,则其对应的系数将从和中去掉。这样乘加运算就变成了查表操作。整数乘以2b可以通过左移6位实现。

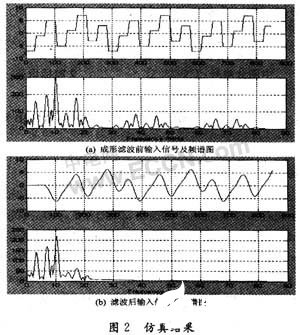

对于本系统,码元速率为25.92 Mbaud,滚降系数选取为0.5,抽头个数取N=16,抽头系数精度取10 b,输入数据为4 b,输出精度取9 b。仿真结果如图2所示。

从图2可以看出:码元速率为25.92 Mbaud的基带信号经成形滤波后,频谱被限制在20 MHz范围内。

3.2 正交调制器的设计

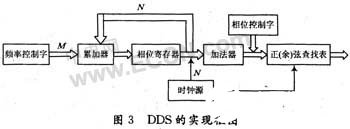

经成形滤波后的两路基带信号分别对DDS(DirectDigital Synthesizer)产生的两路正交的载波进行调制,然后进行矢量相加形成调制信号输出。DDS的FPGA实现框图如图3所示。

DDS的基本原理是利用采样定理,利用查找表法产生波形。相位累加器是DDS系统的核心部分,每来一个时钟脉冲,累加器将频率控制字M与相位寄存器输出的累加相位数据相加,把相加后的结果送至相位寄存器的数据输入端;相位寄存器将累加器在上一个时钟作用后所产生的新相位数据反馈到累加器的输入端,以使累加器在下一个时钟的作用下继续与频率控制数据相加。这样,相位累加器在参考时钟的作用下,进行线性相位累加,当累加器累加满量时就会产生一次溢出,完成一个周期性的动作,这个周期就是DDS合成信号的一个频率周期,累加器的溢出频率就是DDS输出的信号频率。

用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址,这样就可以把存储在波形存储器内的波形抽样值经查找表查出,完成相位到幅值转换。ROM设计的关键问题是进行初始化,就是将正弦波的二进制幅度码按一定的格式输入到存储器初始化(.mif)文件,此文件可以C语言或者Matlab语言程序生成。

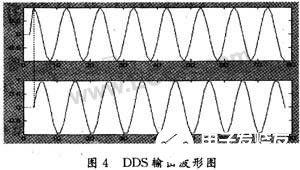

DDS系统输出信号的频率为f0=fclk×M/2N,频率分辨率为△f=fclk/2N,当M=2N-1时,DDS最高的基波合成频率为f0max=fclk/2。对于本系统,时钟频率fclk=155.520 MHz,N取12。仿真结果如图4所示。

由于两个正交本振的形成是通过Madab运算得到的查找表,所以由DDS得到的载频不存在幅度差异,理论上其正交性也完全可以得到保证,但由于存储精度的影响,存在量化误差。

4 系统设计与仿真

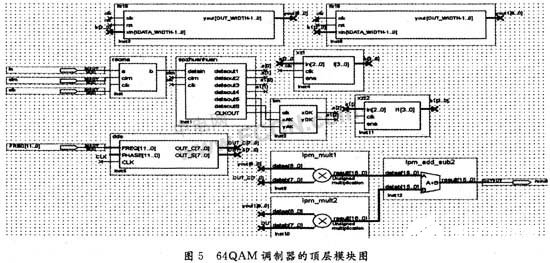

根据以上各模块单元的设计,构成64QAM调制器的顶层文件如图5所示。运用QuartusⅡ及Matlab软件实现64QAM调制器仿真,仿真结果如图6所示。

5 结 语

本文介绍了用FPGA实现全数字高阶QAM调制器的思想和方法,采用原理图和Verilog语言,用可编程芯片StratixⅡ系列中的EP2S30F484C3实现了整个设计,结果表明符合设计要求。为进一步的研究和设计全数字高阶QAM系统打下了良好的基础。

责任编辑:gt

-

可编程逻辑器件的特征及优势科普2024-02-26 2157

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4568

-

可编程逻辑器件测试2023-06-06 1301

-

可编程逻辑器件的结构2023-03-24 2127

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 2248

-

可编程逻辑器件(书皮)2022-07-10 784

-

PLD可编程逻辑器件2021-07-22 2319

-

怎么采用可编程逻辑器件设计数字系统?2021-04-29 1383

-

可编程逻辑器件的分类有哪些2020-06-10 31167

-

可编程逻辑器件2014-04-15 3675

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1162

-

可编程逻辑器件基础及应用实验指导书2010-03-24 784

-

什么是PLD(可编程逻辑器件)2009-06-20 30042

-

可编程逻辑器件设计2006-03-25 1179

全部0条评论

快来发表一下你的评论吧 !