台积电2nm工艺有望在2023年进行试产

电子说

1.4w人已加入

描述

这几年,天字一号代工厂台积电在新工艺进展上简直是开挂一般的存在,7nm工艺全面普及,5nm工艺一路领先,3nm工艺近在眼前,2nm工艺也进展神速。

根据最新报道,台积电已经在2nm工艺上取得一项重大的内部突破,虽未披露细节,但是据此乐观预计,2nm工艺有望在2023年下半年进行风险性试产,2024年就能步入量产阶段。

台积电还表示,2nm的突破将再次拉大与竞争对手的差距,同时延续摩尔定律,继续挺进1nm工艺的研发。

台积电预计,苹果、高通、NVIDIA、AMD等客户都有望率先采纳其2nm工艺。

2nm工艺上,台积电将放弃延续多年的FinFET(鳍式场效应晶体管),甚至不使用三星规划在3nm工艺上使用的GAAFET(环绕栅极场效应晶体管),也就是纳米线(nanowire),而是将其拓展成为“MBCFET”(多桥通道场效应晶体管),也就是纳米片(nanosheet)。

从GAAFET到MBCFET,从纳米线到纳米片,可以视为从二维到三维的跃进,能够大大改进电路控制,降低漏电率。

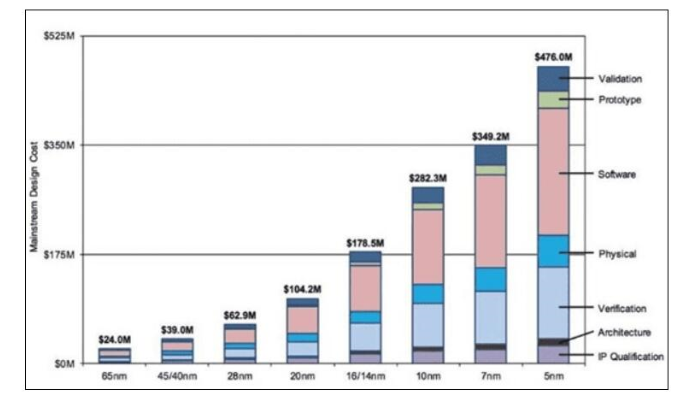

当然,新工艺的成本越发会成为天文数字,三星已经在5nm工艺研发上已经投入了大约4.8亿美元,3nmGAAFET上会大大超过5亿美元。

台积电很少披露具体工艺节点上的投入数字,但是大家可以放开去想象了。

责任编辑人:CC

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

台积电设立2nm试产线2025-01-02 1371

-

台积电2nm芯片试产良率达60%以上,有望明年量产2024-12-09 1539

-

台积电有望2025年量产2nm芯片2023-10-20 2191

-

2nm芯片有望成功吗 2nm芯片最新进展2022-07-07 4823

-

台积电2nm芯片最新信息 台积电计划2025年投产2nm芯片2022-07-01 2655

-

台积电2nm芯片用什么技术 台积电2nm芯片在哪里建厂2022-06-24 2570

-

中国台积电研发2nm芯片2022-06-22 2420

-

台积电将在2021年底建立2nm测试产线2021-06-04 5280

-

台积电2nm工艺重大突破:朝着1nm挺进2020-11-26 3371

-

台积电2nm工艺取得重大内部突破 有望2024年步入量产2020-11-17 2269

-

外媒:台积电2nm工艺的研发已取得重大进展2020-10-10 3008

-

台积电2nm GAA工艺研发进度提前,有望2024年正式量产2020-09-24 2532

-

台积电2nm工艺取得重大突破,2023下半年风险试产良率可达90%2020-09-23 2564

全部0条评论

快来发表一下你的评论吧 !