APB总线的应用框图及接口信号

接口/总线/驱动

描述

APB概述

APB(AdvancedPeripheralBus)是AMBA(AdvancedMicrocontrollerBusArcheticture)总线体系的一部分。相较于AMBA总线体系中的其他总线,APB总线具有低功耗,低复杂度的特征。APB总线主要应用于对性能要求不太高的低带宽外设接口。

APB应用框图

图1APB总线应用框图

图1为AMBA2.0协议中关于APB总线的应用框图。从图中可以看出APB总线一般通过APB桥下挂在更高性能的AHB总线下面。使用APB总线的常用外设有UART,Timer,键盘,PIO等低速外设。除协议中列举的应用外,我之前文章中提到的I2C,SPI,CAN总线控制器都也通常会在片内挂在APB总线下面。

APB总线有明确的主从划分。APB桥为APB总线中的唯一主设备,其他设备如UART,Timer,键盘,PIO等均为从设备。

APB接口信号

APB总线随着AMBA总线协议的演变也在不断加入新的内容。本文中将AMBA2.0中定义的APB总线称为APB2.0,AMBA3.0中定义的APB总线称为APB3.0,AMBA4.0中定义的APB总线称为APB4.0。其信号列表如表1所示。

表1APB接口信号

从表1可以看出,片内总线接口信号和之前介绍的数字接口系列(片外互连总线)有着明显的区别,就是片内总线信号线明显多。这主要是因为片内压缩信号线带来的成本收益与其增加的设计复杂度来讲是负收益。

下面以APB2.0为例简单介绍APB总线的两种基本的数据传输方式:读传输,写传输。APB3.0和APB4.0相对于APB2.0的差异本文末尾处再简述。

AMBA2.0协议中实际上没有单独对APB读写传输进行描述,而是在APB与AHB接口转换中顺便提起。下图中AHB相关总线接口不在本文讨论范围,直接忽略。

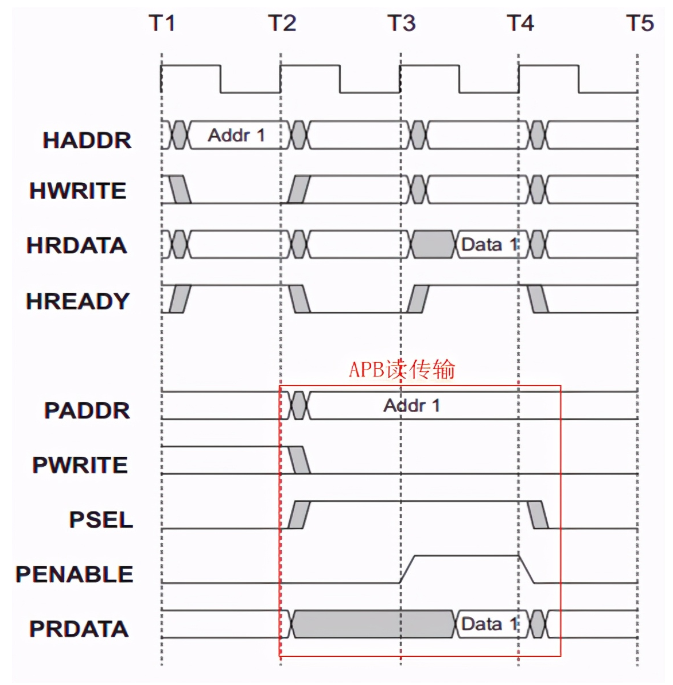

APB读传输

图2APB读传输

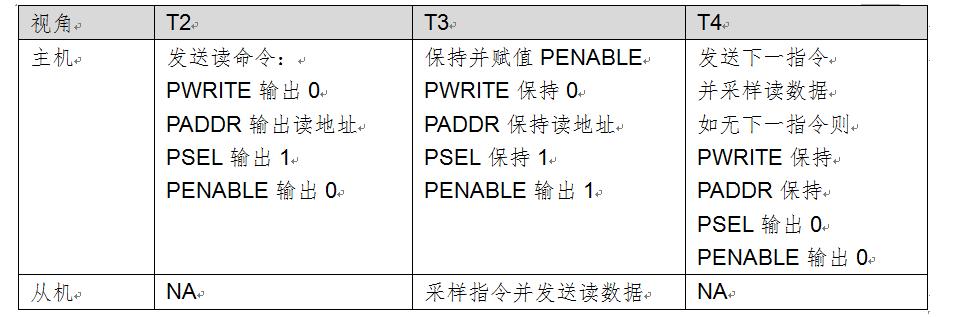

如图2所示。一次APB总线读传输分为两个时钟周期。表2分别从主机和从机两个视角详细介绍两个时钟周期(3个相关时钟上升沿)APB主机和从机的动作。

APB写传输

图3APB写传输

如图3所示。一次APB总线写传输也是分为两个时钟周期。表3分别从主机和从机两个视角详细介绍两个时钟周期,3个相关时钟上升沿中,APB主机和从机的动作。

表3APB读传输

后记

APB2.0协议对读写操作均定义了两个时钟周期。实际Verilog实现时,读操作一般在第一个时钟周期(PSEL为高,PENABLE为低)锁存读指令,第二个时钟周期输出读数据。而写操作直接在第二个时钟周期更新数据,实际上写操作一个周期即可完成。

APB3.0更新:在APB2.0基础上增加两个信号PREADY和PSLVERR。

PREADY,允许APB从设备通过在PENABLE有效时拉低PREADY信号扩展APB传输周期,引入了等待的概念。因此APB3.0/APB4.0协议的数据传输周期不再是固定2个周期。

PSLVERR,用于从设备反馈传输错误。

APB4.0更新:在APB3.0基础上增加了PPROT和PSTRB信号。

PPROT,指示当前读写传输的类型。PPROT[0]:1’b0,Normal访问,1’b1,Privileged访问。PPROT[1]:1’b0,安全访问,1’b1,非安全访问。PPROT[2]:1’b1,数据访问,1’b1,指令访问。PPROT的引入主要为了是配合AMBA4.0总线的安全特性。

PSTRB,允许APB总线基于字节进行写传输,PSTRB[n]代表PWDATA[(8n+7):8n]是否有效,当从机收到写传输时,检查PSTRB对应哪些bit为高,则从机接收对应字节的写传输。

当前APB3.0/2.0应用较为广泛。APB4.0主要应用在对安全较高的系统中,比如车载芯片,工业控制芯片等。

责任编辑人:CC

-

史上最全:主板上常见的接口信号定义与分类详解2016-11-01 25809

-

什么是APB协议/总线?APB总线入门2024-01-02 8160

-

什么是板间接口信号?2021-04-09 1258

-

AMBA AHB总线与APB总线资料合集2022-04-07 5220

-

SMC1602的封装尺寸及接口信号说明2008-11-01 5541

-

CAN总线接口信号隔离收发IC2016-11-18 1417

-

观察PCI Express HIP PIPE接口信号2018-06-22 4664

-

AHB总线的应用框图/接口信号/基础传输2020-12-10 5483

-

浅述AMBA-APB总线2021-07-23 3441

-

HDMI模块接口概念及接口信号定义介绍2022-04-12 1740

-

龙迅HDMI接口信号转换的应用案例2022-06-14 5904

-

聊聊AMBA总线-APB2023-05-04 1611

-

AMBA总线—apb简介2023-06-05 3863

-

顺源科技新产品:内置隔离电源的CAN总线通讯接口信号隔离模块2022-02-25 647

-

SOC设计中APB协议总线的工作原理2024-01-17 3819

全部0条评论

快来发表一下你的评论吧 !