采用功率SENSEFET实现V/I变换电路的设计

模拟技术

描述

作者:罗鹏,张树春,王慧,李庆委

引言

固定频率峰值电流模式PWM(Pulse WidthModulation) DC-DC变换器同传统的电压模式控制相比,具有瞬态响应好,输出精度高,带载能力强等优点,因而被广泛应用。作为重要的模拟单元,斜坡补偿电路和电流采样电路是电流模式PWM控制的根基,对电流模式控制中电流环路的稳定性起着重要作用。

1 电路结构

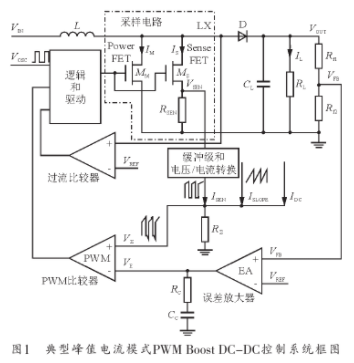

图1所示是典型峰值电流模式PWM Boost DC-DC控制系统的结构框图。当电压外环的电压反馈信号经过误差放大器放大得到的误差信号VE送至PWM比较器后,将与电流内环的一个变化的、其峰值代表输出电感电流峰值的三角波或梯形尖角状合成波信号VE比较,从而得到PWM脉冲关断阈值。即:

在(1)式中:第一项为斜坡补偿部分,用于保证电流环路的稳定;第二项反映了电感电流的大小,通常由电流采样电路产生;第三项用于产生一个固定的基础电平,以为PWM比较器输入端图1 典型峰值电流模式PWMBoostDC—DC控制系统框图提供一个合适的直流工作点。

因此,峰值电流模式控制不是用电压误差信号直接控制PWM脉冲宽度,而是通过控制峰值输出端的电感电流大小,然后来间接地控制PWM脉冲宽度。

但是,电流模式的结构决定了其应用时存在电流内环在占空比大于50%时的开环不稳定现象、亚谐波振荡、非理想的环路响应,以及容易受噪声影响等几个固有缺点。针对上述问题,在环路的补偿方式上,除了电压环路的RC串联补偿之外,还必须对电流环路进行补偿,以满足电流环路的稳定性要求。有效的解决方法是采用斜坡补偿技术,并在提高电流采样精度的同时降低采样损耗,以保证电流环路的稳定。

本文利用对振荡器充放电电容上的电压作V/I转换来得到稳定且斜率易于调节的补偿斜坡,同时采用功率SENSEFET作为采样器件,并结合设计简洁的V/I变换,使采样系数不受温度和工艺的影响,从而在得到较高精度采样值的同时,还减低了损耗。

2 电路原理分析

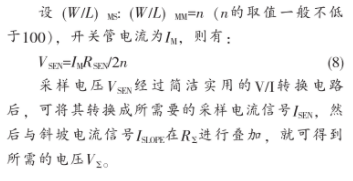

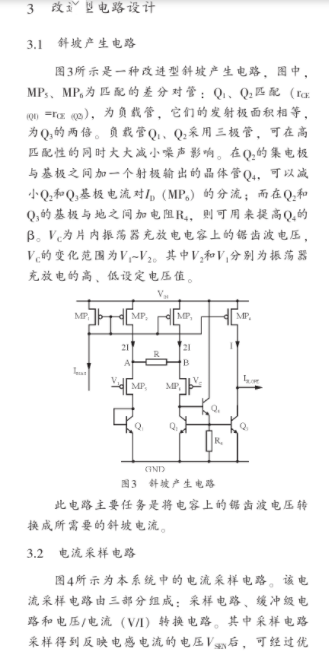

2.1 斜坡补偿

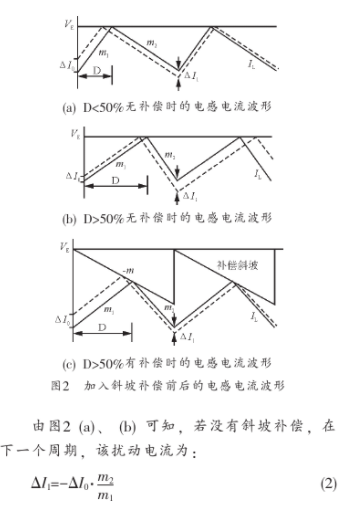

图2给出了在误差信号VE上叠加斜坡补偿电压的方法。VE为电压反馈回路的误差放大信号,实线波形为未加扰动的电感电流,虚线为叠加△I0扰动量的电感电流,D为占空比,m1、m2分别为采样得到的等效电感电流的上升和续流斜率。

而经过n个周期后,由△I0引起的电流误差△In为:

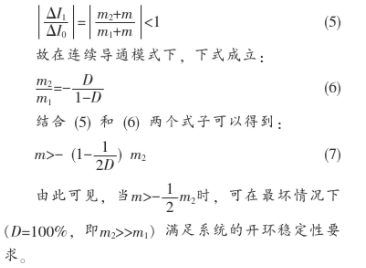

由式(3)可以看出,当m250%时,电流误差△In将逐渐放大,从而导致系统不稳定。

图2(c)是D》50%时,叠加补偿电压后的电感电流波形。对于该波形,有:

显然,要使环路稳定,必须使△I1》m1)满足系统的开环稳定性要求。

图1所示的电路同时给出了在电流反馈电压上叠加斜坡补偿电压的方法。通过比较分析可知,两种补偿方法在效果上是等效的,但是第二种方法中的电路实现相对更简单,因此较为常用。

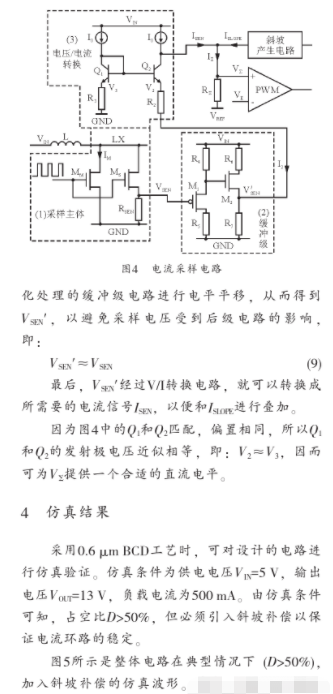

2.2 电流采样原理与方法

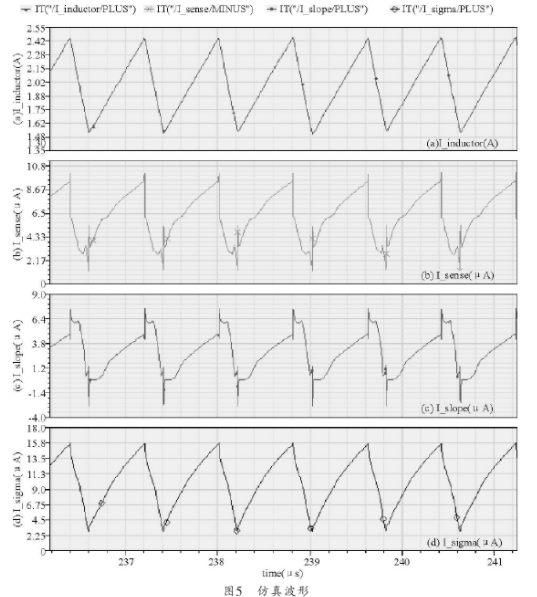

传统电流采样方法是在开关管的电流通路上串接检测电阻,这样不仅降低了DC-DC转换器的效率,而且对于传统工艺来说,制作这样的小电阻也很困难。为了弥补这些不足,本文在SENSEFET采样方法的基础上,加入了简洁的V/I变换电路,从而形成了一种结构简单且精度较高的采样电路,其电路主体如图l中的采样电路所示。其中MM为POWER FET,其宽长比设计的非常大,可以减小其导通阻抗(本电路的典型值为150 mΩ);Ms为SENSE FET;检测电阻RSEN可利用工作在线性区MOS管的导通阻抗特性,使其宽长比与Ms相同,因此,导通阻抗与Ms的相等,记为RSEN。为了减小采样损耗,一般必须使(W/L)MM50%),加入斜坡补偿的仿真波形。

其中,图5(a)是电感实际的电流波形。其电感电流峰值为Iinductor_PEAK=1.796 A;图5(b)是采样得到的电感电流波形,其采样电感电流峰值为Isensc_PEAK=10.505μA。

由于设计中的典型值R2=R3=10 kΩ,RDS(MM)=150 mΩ,RDS(MS)=15 Ω,n=100,故其电流采样系数α为:7.5x10-6,采样精度为77.9%。

图5(c)是斜坡补偿电路产生的斜坡电流波形,实测的补偿斜坡的斜率为5.487 A/s,时钟CLK为1.2 MHz,占空比为85.7%,T1=685.563 ns。由于本设计中的典型值为:

V1=0.4 V,V2=1 V,R=65 kΩ。

故可得其补偿斜坡的斜率为:m=6.732 A/s。

因此可知,本设计的补偿斜坡已经达到较高精度(81.5%),可以满足设计要求;

图5(d)是电感电流采样值与补偿斜坡的合成波形。可以看出,其斜坡补偿的加入有效的抑制了亚谐波振荡。

5 结束语

本文针对峰值电流模式DC-DC转换器固有的不稳定性,设计了斜坡补偿电路。采用固定斜率补偿技术,虽然在小占空比条件下会减弱电流模式PWM控制的优点,但其电路结构简单,容易调节,可降低设计难度,同时针对一般的便携式设备,完全可以满足应用要求;而电流采样电路使用SENSE FET,同时结合缓冲级和V/I转换电路,可在采样精度得到提高的同时减小损耗。因此,本设计中的两个V/I转换电路可以较好地移植到其它DC-DC变换器电路中。

目前,本电路已经应用在一款升压型DC-DC芯片中,并且已经完成了前期仿真。仿真结果达到了预期要求,证明了该电路的可行性。

责任编辑:gt

-

求助,采用运放复合方式实现的一个I/V转换电路的设计问题求解2024-08-27 0

-

电源变换电路2024-09-28 0

-

两线制V/I变换器 V/I 变换器2011-06-09 0

-

转换器接口的隔离方法和I/V变换2019-06-24 0

-

新型实用功率放大电路集锦2009-08-24 4487

-

采用功率运放构成的音频放大器电路2008-12-17 1806

-

常用功率放大电路芯片LM386的等效电路及封装形式2009-04-02 5110

-

V I变换电路图2009-07-06 1280

-

采用LM2579构成+15V-15V的DC DC变换器电路2009-11-14 1740

-

6v-12v/25w直流电压变换器电路2009-12-10 1516

-

功率变换电路2010-02-21 761

-

两线制V/I变换器设计2011-05-11 4896

-

NI Multisim 10经典教程分享--电压/电流(U/I)变换电路2023-01-04 3386

-

功率变换电路图讲解 简单的功率变换电路及原理说明2023-07-21 1749

全部0条评论

快来发表一下你的评论吧 !