基于DSP芯片TMS320C32PCMA50实现捷联惯性制导系统的设计

处理器/DSP

描述

1 引言

捷联惯性制导是随着计算机技术的发展而发展起来的惯性制导技术,由于它是用一个数学平台来代替平台式惯性制导系统中的陀螺稳定平台,因而具有成本低、结构简单、体积小、可靠性高等优点。但正是由于没有稳定平台,其惯性器件的测量值就不能直接用于导航计算,而必须先经过复杂的数学变换把其变为符合导航计算要求的值,这样捷联惯性制导在计算上十分复杂,同时对计算装置的性能也提出了很高的要求。

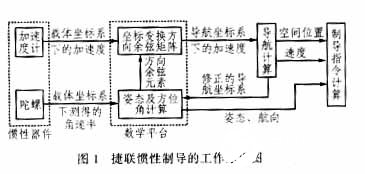

2捷联惯性制导的工作原理

由于去掉了稳定平台,捷联惯性制导将惯性器件直接固联于弹体上。这样,其惯性器件所测得的值便是沿弹体坐标系轴向的测量值。由于弹体坐标系是运动坐标系,而导航计算是以参考坐标系(导航坐标系)为参照来确定弹的位置、速度、姿态等运动参数的。因此,弹体坐标系下的测量值不能直接用于导航计算,而必须先对它们进行变换,以将其变换到导航坐标系,然后再进行导航计算。具体的变换会因所选的参考坐标系的不同而有所不同,其基本过程如下:

(1)计算机根据陀螺的输出计算出姿态角;

(2)根据姿态角参数,确定用来进行坐标变换的方向余弦矩阵;

(3)把弹体坐标系下的加速度用方向余弦矩阵变换到导航坐标系下;

(4)根据相应的力学编排方程算出弹体的即时速度、位置等制导参数。

图1所示是一个捷联惯性制导的工作原理示意图。该系统的坐标系变换过程需要进行大量的矩阵运算,而变换后的导航计算主要是积分运算。因此,从计算方面来看,捷联惯性制导在计算上是很复杂的,没有相当的硬件支持是无法实现的。但从其它方面来看,省掉稳定平台又使得捷联惯性制导系统具有结构简单,可靠性高,容易制造,体积小,重量轻,成本低等特点。所以,捷联惯性制导利用数学技术实现了系统结构的简化,并由此带来了工程技术上的优越性。因此,小型战术制导武器系统很适合采用这种技术。

3 捷联惯性制导系统的设计

3.1 DSP技术介绍

DSP(数字信号处理器)是一种特殊结构的微处理器,该类器件原本主要是用来对数字信号进行快速傅立叶变换(FFT)、离散余弦变换(DCT)、卡尔曼滤波等运算量极大且要求实时计算的系统进行处理的。为达到快速进行数字信号处理的目的,DSP芯片应有一些特殊硬件结构,具体表现如下:

(1)哈佛结构:哈佛结构是并行体系结构,主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个互相独立的存储器,每个存储器独立编址,独立访问。与两个存储器相对应的是系统中的程序总线和数据总线,这两条总线可使数据吞吐量提高一倍。

(2)流水线操作:该操作与哈佛结构相关,DSP芯片广泛采用流水线操作方式以减少指令执行时间,增强处理器的处理能力;

(3)专用的硬件乘法器:乘法可以在一个指令周期内完成;

(4)特殊的DSP指令:DSP芯片使用专门用于数字信号处理的特殊指令;

(5)快速的指令周期:由于采用哈佛结构、流水线操作、专用的硬件乘法器、特殊的DSP指令再加上集成电路的优化设计,因此,DSP芯片的指令周期可降到20ns以下,而快速的指令周期则可使DSP芯片能够实现很多实时计算的应用。

可以看出,DSP的高速实时计算能力很强。因此,捷联惯性制导需要进行的大量实时计算非常适合用DSP芯片来实现。

3.2 制导系统电路设计

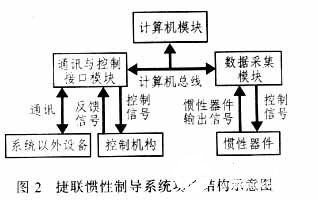

捷联惯性制导理论将整个系统电路按功能分成三大模块,即计算机模块、数据采集模块、通讯与控制接口模块。其中计算机模块负责全系统所有的计算和控制工作;数据采集模块负责从惯性器件采集数据;通讯与控制接口模块负责计算机模块与系统外其它设备的通讯工作和对弹体飞行控制机构的控制工作。三大模块之间通过总线进行互连。其系统功能结构示意图如图2所示。从图中可以看出,计算机模块是全系统的核心,是唯一有计算能力的部分,系统中所有软件功能均在此实现。所以,本模块设计的好坏对整个系统的性能影响很大,是系统全部电路设计的关键。下面重点介绍这部分电路的设计。

对于一个计算机电路来说,决定其性能的最重要部分当然是处理器。所以,本模块采用什么样的处理器也就成了这部分电路设计的重点。综合捷联惯性制导的特点和系统的设计要求,选用TI公司的TMS320C32PCMA50(简称C32)作处理器。C32是一种32位高性能浮点数字信号处理器(DSP),与一般的DSP芯片相比,C32允许数据存放在程序存储器中并被算术运算指令直接引用,从而增强了芯片的灵活性;另外,C32也可以将指令存储在高速缓冲器Cache中。这样,当执行此指令时,就不需要再从存储器中读取指令,从而节约了一个指令周期的时间。C32的运算速度高达60MFLOPS(每秒百万次浮点运算)和25MIPS(每秒百万次指令)。所以,不论从速度上,还是精度上,C32都完全可以满足捷联惯性制导系统的设计要求。

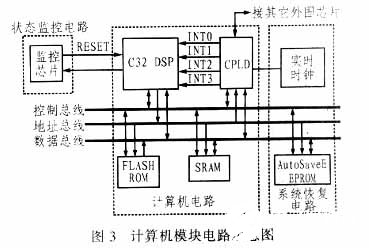

系统中的计算机模块电路一般由状态监控、系统恢复和计算机电路组成。本模块电路示意图见图3所示。该模块是全系统的核心,而C32 DSP更是核心中的核心。因此,有必要对其进行专门的监控,以保证其正常运行。设计时可通过状态监控电路来对C32 DSP和电源进行监控,以防因偶然情况出现死循环、程序偏离预定流程而导致系统失效。

惯性制导系统是历史信息敏感型系统,如果系统因故重启后没有历史信息,其后的导航计算就没什么意义。所以有必要对系统运行的一些重要信息进行保存,以便重启后能迅速接替以前的工作。为此,本系统采用了两条措施:第一是使用高速自动存储E2PROM对数据存储器中的重要数据进行自动备份;第二是使用一个具有备份电源的实时时钟芯片来记录从上一次导航数据保存时刻到重启后读取导航历史信息之间的时间长度。该实时时钟芯片在主电源掉电后能利用备份电源提供几十秒的电能。系统恢复电路就由上述两个芯片构成。

计算机电路是本模块的核心电路,它由C32 DSP、SRAM、FLASHROM和CPLD构成。为提高性能,该电路采用32位数据总线和24位地址总线。同时,由于C32被设置成了微机工作模式,因而具有自主引导功能。系统程序固化在FLASHROM中,SRAM则用作数据存储器。将CPLD作为C32和外围芯片的接口可实现很多逻辑电路功能。外围芯片与C32的连接需要有一个唯一的I/O地址,因此在CPLD中设计的I/O地址分配电路可为每个外围芯片分配一个I/O地址。另外,C32本身的外部中断源只有四级(个),而系统中需要通过中断来执行的程序又不止四个,故采用中断和查询相结合的办法来解决这个问题。由于同一级中断中包括好几个中断源,这样,在该级中断响应时再对具体的中断源进行查询即可确定需要具体响应哪个中断源。因此,在CPLD中设计了中断分配电路。对于启动和运行时间都很严格的中断源来说,可由各种频率的时钟信号来对其进行触发。所以,CPLD中还设计了时钟分频电路,即用系统的精确时钟来分频以产生所需的各种频率时钟。

对于I/O地址分配电路、中断分配电路和时钟分频电路,如果用标准逻辑器件(74系列或54系列)来实现,将需要很多芯片,这样一方面将使电路部分的体积和功耗增加;另一方面也会使电路的规模扩大、复杂性增加、可靠性下降。因此,这三个电路可用CPLD(复杂可编程器件)来实现。为了充分利用CPLD 的灵活性,系统中其它的一些逻辑电路也被放到这里。这样,在一片170mm×170mm的小芯片

中就可实现系统所需的大量逻辑功能。

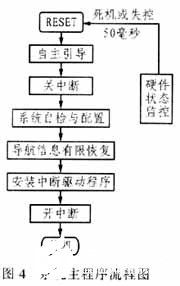

3.3 系统程序设计

导航、制导计算都属于实时计算。要实现这一要求,软件就必须结合硬件来进行设计,以充分发挥硬件的功能。本设计充分利用了系统的中断功能,并以中断为主来进行程序设计,以使系统中各个部分的具体功能都可通过中断程序来实现。其系统工作过程如下:

加电开机→FLASH中的程序调入内存→系统初始化、自检→导航信息恢复→安装中断程序→打开中断→待机。

该系统的软件包括主程序、子程序和各中断响应程序等部分。

其中主程序是系统程序的框架,重要的初始化参数主要在主程序中定义,主程序通过调用子程序来完成系统初始化、自检、导航信息恢复、系统配置、中断程序配置等功能。其中,系统自检程序主要检测CPU、SRAM以及各接口芯片的工作是否正常。引导程序主要根据系统硬件中存储的状态信息来确定导航计算的起点。主要状态信息有:系统是加电开机还是死机后重新启动,以及上一次保存数据与当前的时间间隔等。根据系统硬件中保存的状态信息和非易失存储器中保存的导航信息可确定当前导航计算的基准点。系统主程序流程如图4所示。

子程序主要用来完成一些特定的功能,包括导航子程序、控制子程序、通讯子程序和卡尔曼滤波子程序等。

中断程序由硬件中断触发,除完成现场保护和硬件信息处理外,还可根据需要调用导航子程序、控制子程序、通讯子程序、状态监控子程序、卡尔曼滤波程序等,同时在处理完成后恢复现场并向主程序返回数据。

4 结束语

捷联惯性制导是一种很有应用价值的惯性制导方法,随着计算机技术的发展,该技术将迅速应用于各种战术武器中。本文并不企图在理论上进行创新,而是在技术上谋求好的实现方法。实验证明:用DSP芯片对惯性器件的信息进行处理,并用可编程器件进行逻辑电路的实现,可简化系统电路,提高系统的运算性能以及可靠性和灵活性。

责任编辑:gt

-

捷联式惯性导航系统2016-08-17 3258

-

基于PCI和DSP的导弹景象匹配制导系统设计2019-07-26 1714

-

TMS320C54X DSP实现UART的技术2009-09-27 1317

-

TI推出16位DSP TMS320C5514与TMS320C2010-01-21 1786

-

基于DSP芯片TMS320C6418的成像制导仿真系统设计2010-09-01 1367

-

DSP芯片TMS320C6712的外部内存自引导功能的实现2010-09-14 1349

-

基于TMS320C64x+DSP的FFT实现2013-03-14 1075

-

DSP系统设计和BIOS编程及应用实例:基于TMS320C67x2016-04-26 1369

-

TMS320C2000系列DSP芯片原理与应用2016-05-06 1292

-

基于DSP_MCU的小型捷联惯性导航计算机系统2017-10-20 958

-

捷联惯性制导技术的应用分析2017-10-23 1610

-

使用双DSP和TMS320C6202B设计红外制导系统的应用说明2019-09-27 1184

-

基于TMS320C5410和ADuC834微处理器实现压电捷联惯导系统的设计2020-04-22 1961

-

如何使用TMS320C6711D和FPGA实现图像辅助末制导系统的设计与实现2021-01-26 874

-

TMS320VC5505、TMS320C5505和TMS320C5515 DSP上的FFT实现2024-10-12 734

全部0条评论

快来发表一下你的评论吧 !