大规模物联网连接数量增加三倍 物联网设备系统设计应考虑哪些因素?

物联网

786人已加入

描述

2020 年,大规模物联网技术 NB-IoT 和 Cat-M 继续在全球部署。到 2020 年底,大规模物联网应用的数量将达到约 1 亿。根据 Ericsson 预估,到 2025 年底,NB-IoT 和 Cat-M 将占所有蜂窝物联网连接的 52%。

物联网应用设计考虑因素为了在市场上获得更广泛采用,物联网应用必须满足各种设计考虑因素,例如低成本、低功耗和运算效率。尤其对于电池供电的设备(例如智能音箱和智能电表)而言,除了丰富的物联网功能和易于使用的人机接口,电池寿命也成为产品成功与否的关键,因此低功耗因素变得越来越重要。为了延长电池寿命,除了使用低功耗 MCU,还应考虑其他低功耗的周边组件。

图 1 移动设备系统架构图

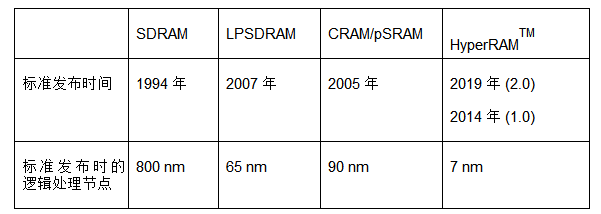

许多移动设备采用图 1 中的相似架构,如平板电脑或智能手表等。Wi-Fi/BT 和移动网络模块负责通信。传感器(如触摸面板)专用于收集外部信息,并将信息转发给应用处理器。NOR/NAND 负责存储程序代码/数据,而 DRAM 则用于暂时性的处理。目前,许多 MCU 供货商正在开发效能更高、功耗更低的新一代 MCU,以满足市场需求。但从整体系统设计的角度来看,与 MCU 搭配使用的 DRAM 也需要有新的选择,以提供比现有 SDRAM、低功耗 SDRAM 和 CRAM/PSRAM 更佳的优势。因为这些现有的 DRAM 标准定义过于陈旧,已无法跟上最新技术发展(详情请参照表1)。

表 1 DRAM 标准及其对应逻辑处理节点

支持 HyperBusTM 接口的 HyperRAMTM 是能满足市场需求的最新技术解决方案。HyperBusTM 技术由 Cypress 于 2014 年首次发布,并于 2015 年推出其首款 HyperRAMTM 产品。考虑到市场发展需要,华邦电子决定加入 HyperRAMTM 阵营,并推出 32Mb/64Mb/128Mb 容量的产品,进一步扩展其产品组合,以应对多样化的应用需求,使生态系统更趋完整。HyperRAMTM 使用优势

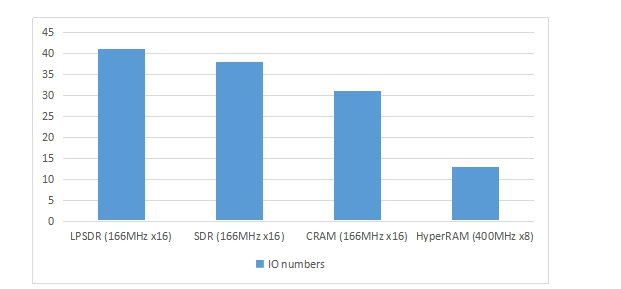

HyperRAMTM 仅具备 13 个信号 IO 脚位,可大大简化 PCB 的布局设计。这也意味着,在设计最终产品时,设计人员能将 MCU 的更多脚位用于其他目的,或减少 MCU 使用脚位以提升成本效益。如图 2 所示,与类似的 DRAM(如低功耗 DRAM、SDRAM 和 CRAM/PSRAM)相比,HyperRAMTM 只需最少的脚位数便能实现近似的处理量(333MB/s)。

图 2 IO 脚位比较

简化控制接口是 HyperRAMTM 的另一项技术特色,PSRAM 只有 9 个控制接口,而 LPSDRAM 有 18 个。控制接口越少,DRAM 控制器所需的复杂度就越低。详细区别可参阅图 3。HyperRAMTM 系以 PSRAM 架构为基础,是能够自刷新(Self Refresh)的 RAM。而且,它可以自动恢复为待机模式。因此,系统内存更易于使用,固件和驱动程序的开发也会更简单。

图 3 LPSDR 和 HyperRAMTM 的控制接口比较

由于 HyperRAMTM 是近几年才开发的,因此它可以采用最新型的半导体制程节点和封装技术,使其封装尺寸比其他 DRAM 都要小。图 4 为 JEDEC、PSRAM 和 HyperRAMTM 的封装尺寸比较。

图 4 封装尺寸比较

HyperRAMTM 满足新兴物联网设备需求

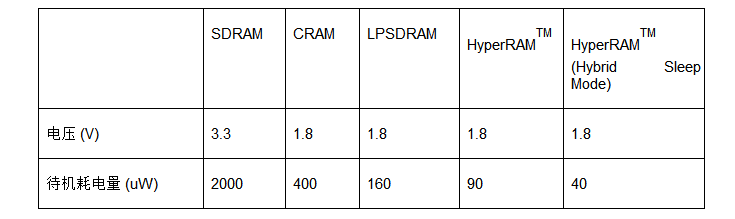

功耗对于物联网设备至关重要,因为设备大多由电池供电。降低功耗不仅可以节省用电,还可以减少设备充电和更换的成本。以华邦的 64Mb HyperRAMTM 为例,其待机耗电量为 90uW(1.8V 下),而相同容量的 SDRAM 的耗电量则是 2000uW(3.3V 下)。

更重要的是,HyperRAMTM 在混合休眠模式下的耗电量仅 45uW(1.8V 下),与 SDRAM 在待机模式下的耗电量有明显差异(表 2)。另一方面,即使采用低功耗的 SDRAM,其耗电量和外形尺寸仍较 HyperRAMTM 更大。

表 2 耗电量比较

传统的 SDRAM 和 PSRAM 发展日臻成熟,难以对新兴的物联网应用进行优化。有鉴于汽车和工业应用的长期供应需求,华邦 HyperRAMTM 的先进制程节点可以满足市场对长寿命产品生命周期的需求。从整个系统设计和产品寿命来看,HyperRAMTM 已成为新兴物联网设备的理想选择。包括 NXP、Renesas、ST 和 TI 等领先的 MCU 公司已开始提供支持 HyperBusTM 接口的 MCU,未来其新产品亦将继续支持 HyperBusTM 接口。

同时,HyperBusTM 控制接口开发平台已准备就绪。Cadence 和 Synopsys 也已开始提供 HyperRAMTM 存储器验证 IP,可加快 IC 厂商的设计周期。因此,与其他 Octal RAM 相比,HyperRAMTM 具有最成熟的应用环境。HyperRAMTM 已被纳入 JEDEC 标准,并成为与 JEDEC x SPI 兼容的技术。

目前,华邦 HyperRAMTM 产品系列的 32Mb、64Mb 和 128Mb 已进入量产,同时已开始提供 24BGA(汽车级)、49BGA、WLCSP 和 KGD 的产品。24BGA 的尺寸为 6x8 mm2,而 49BGA 的尺寸仅为 4x4 mm2,主要针对消费型可穿戴式设备市场。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

评论(0)

发评论

-

zbd951012

2020-12-04

0 回复 举报华为海思新一代PLC-IOT电力载波方案13632813280 收起回复

zbd951012

2020-12-04

0 回复 举报华为海思新一代PLC-IOT电力载波方案13632813280 收起回复

-

大规模物联网供电:考虑因素与微能量采集技术解决方案2025-09-22 477

-

在物联网应用中采用ZigBee IP需要考虑哪些因素?2021-05-24 1683

-

物联网市场规模扩大对无线模组的影响是什么2021-02-23 717

-

物联网市场规模扩大对无线模组有哪些影响2021-02-02 5072

-

如何选择合适的物联网模块?2020-09-08 1881

-

物联网卡,设备联网的好方法2020-09-07 2470

-

北京移动实现4倍“物超人”,物联网连接规模累计突破9200万部2020-06-18 2440

-

预计到2025年,全球物联网总连接数规模将达到246亿2020-03-23 8980

-

物联网的物定义2019-07-29 2166

-

物联网设备的5个关键考虑因素2018-12-20 3410

-

物联网引爆点:连接容量2018-08-22 2242

-

物联网将是一场激烈的专利战2017-06-14 2496

-

2020年物联网收入将达千亿元规模2016-06-30 3080

-

从“雾”到“云”:物联网设计需考虑哪些因素?2014-09-18 5507

全部0条评论

快来发表一下你的评论吧 !