从储能的角度来说明电容退耦原理

描述

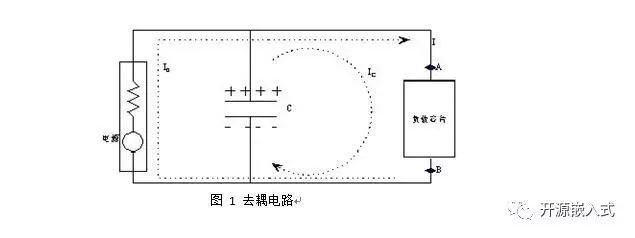

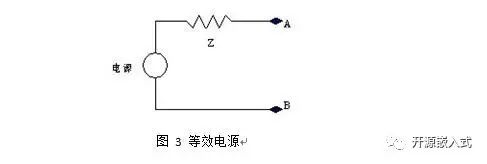

电容退耦原理采用电容退耦是解决电源噪声问题的主要方法。这种方法对提高瞬态电流的响应速度,降低电源分配系统的阻抗都非常有效。对于电容退耦,很多资料中都有涉及,但是阐述的角度不同。有些是从局部电荷存储(即储能)的角度来说明,有些是从电源分配系统的阻抗的角度来说明,还有些资料的说明更为混乱,一会提储能,一会提阻抗,因此很多人在看资料的时候感到有些迷惑。其实,这两种提法,本质上是相同的,只不过看待问题的视角不同而已。为了让大家有个清楚的认识,本文分别介绍一下这两种解释。从储能的角度来说明电容退耦原理。在制作电路板时,通常会在负载芯片周围放置很多电容,这些电容就起到电源退耦作用。其原理可用图1 说明。

当负载电流不变时,其电流由稳压电源部分提供,即图中的I0,方向如图所示。此时电容两端电压与负载两端电压一致,电流Ic 为0,电容两端存储相当数量的电荷,其电荷数量和电容量有关。当负载瞬态电流发生变化时,由于负载芯片内部晶体管电平转换速度极快,必须在极短的时间内为负载芯片提供足够的电流。但是稳压电源无法很快响应负载电流的变化,因此,电流I0 不会马上满足负载瞬态电流要求,因此负载芯片电压会降低。但是由于电容电压与负载电压相同,因此电容两端存在电压变化。对于电容来说电压变化必然产生电流,此时电容对负载放电,电流Ic 不再为0,为负载芯片提供电流。根据电容等式:

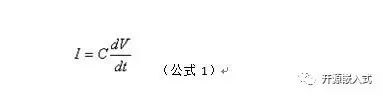

只要电容量C 足够大,只需很小的电压变化,电容就可以提供足够大的电流,满足负载瞬态电流的要求。这样就保证了负载芯片电压的变化在容许的范围内。这里,相当于电容预先存储了一部分电能,在负载需要的时候释放出来,即电容是储能元件。储能电容的存在使负载消耗的能量得到快速补充,因此保证了负载两端电压不至于有太大变化,此时电容担负的是局部电源的角色。从储能的角度来理解电源退耦,非常直观易懂,但是对电路设计帮助不大。从阻抗的角度理解电容退耦,能让我们设计电路时有章可循。实际上,在决定电源分配系统的去耦电容量的时候,用的就是阻抗的概念。从阻抗的角度来理解退耦原理。将图1 中的负载芯片拿掉,如图2 所示。从AB 两点向左看过去,稳压电源以及电容退耦系统一起,可以看成一个复合的电源系统。这个电源系统的特点是:不论AB 两点间负载瞬态电流如何变化,都能保证 AB 两点间的电压保持稳定,即 AB 两点间电压变化很小。

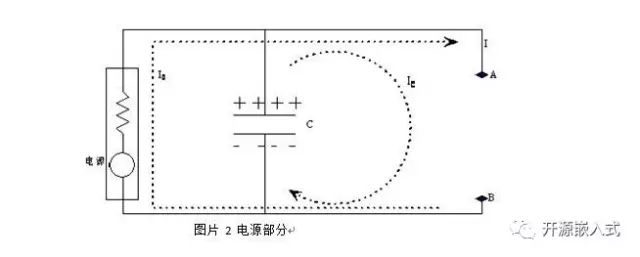

我们可以用一个等效电源模型表示上面这个复合的电源系统,如图3

对于这个电路可写出如下等式:

我们的最终设计目标是,不论AB 两点间负载瞬态电流如何变化,都要保持AB 两点间电压变化范围很小,根据公式2,这个要求等效于电源系统的阻抗 Z 要足够低。在图2 中,我们是通过去耦电容来达到这一要求的,因此从等效的角度出发,可以说去耦电容降低了电源系统的阻抗。另一方面,从电路原理的角度来说,可得到同样结论。电容对于交流信号呈现低阻抗特性,因此加入电容,实际上也确实降低了电源系统的交流阻抗。从阻抗的角度理解电容退耦,可以给我们设计电源分配系统带来极大的方便。实际上,电源分配系统设计的最根本的原则就是使阻抗最小。最有效的设计方法就是在这个原则指导下产生的。

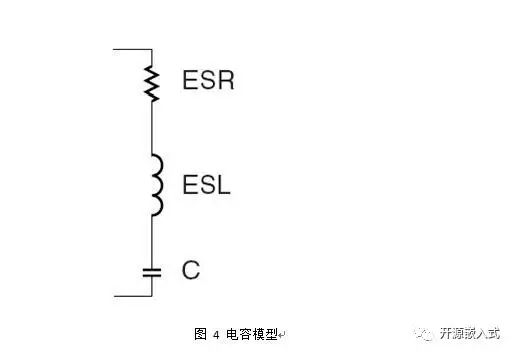

正确使用电容进行电源退耦,必须了解实际电容的频率特性。理想电容器在实际中是不存在的,这就是为什么经常听到“电容不仅仅是电容”的原因。实际的电容器总会存在一些寄生参数,这些寄生参数在低频时表现不明显,但是高频情况下,其重要性可能会超过容值本身。图4 是实际电容器的SPICE 模型,图中,ESR 代表等效串联电阻,ESL 代表等效串联电感或寄生电感,C 为理想电容。

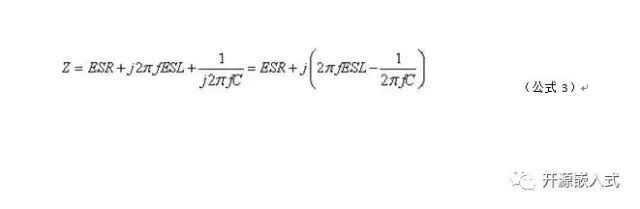

等效串联电感(寄生电感)无法消除,只要存在引线,就会有寄生电感。这从磁场能量变化的角度可以很容易理解,电流发生变化时,磁场能量发生变化,但是不可能发生能量跃变,表现出电感特性。寄生电感会延缓电容电流的变化,电感越大,电容充放电阻抗就越大,反应时间就越长。等效串联电阻也不可消除的,很简单,因为制作电容的材料不是超导体。讨论实际电容特性之前,首先介绍谐振的概念。对于图4 的电容模型,其复阻抗为:

当频率很低时,2πFELS远小于2πFC/1,整个电容器表现为电容性,当频率很高时,2πFELS大于2πFC/1,电容器此时表现为电感性,因此高频时电容不再是电容”,而呈现为电感。

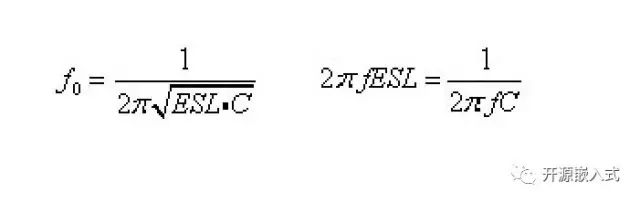

当以下公式满足时:

此时容性阻抗矢量与感性阻抗之差为0,电容的总阻抗最小,表现为纯电阻特性。该频率点就是电容的自谐振频率。自谐振频率点是区分电容是容性还是感性的分界点,高于谐振频率时,“电容不再是电容”,因此退耦作用将下降。因此,实际电容器都有一定的工作频率范围,只有在其工作频率范围内,电容才具有很好的退耦作用,使用电容进行电源退耦时要特别关注这一点。寄生电感(等效串联电感)是电容器在高于自谐振频率点之后退耦功能被消弱的根本原因。图5 显示了一个实际的0805 封装0.1uF 陶瓷电容,其阻抗随频率变化的曲线。

电容的等效串联电感和生产工艺和封装尺寸有关,同一个厂家的同种封装尺寸的电容,其等效串联电感基本相同。通常小封装的电容等效串联电感更低,宽体封装的电容比窄体封装的电容有更低的等效串联电感。既然电容可以看成RLC 串联电路,因此也会存在品质因数,即Q 值,这也是在使用电容时的一个重要参数。电路在谐振时容抗等于感抗,所以电容和电感上两端的电压有效必然相等,电容上的电压有效值UC=I*1/ωC=U/ωCR=QU,品质因数Q=1/ωCR,这里是电路的总电流。电感上的电压有效值UL=ωLI=ωL*U/R=QU,品质因数 Q=ωL/R。因为:UC=UL 所以Q=1/ωCR=ωL/R。电容上的电压与外加信号电压U 之比UC/U=(I*1/ωC)/RI=1/ωCR=Q。电感上的电压与外加信号电压U 之比UL/U=ωLI/RI=ωL/R=Q。从上面分析可见,电路的品质因数越高,电感或电容上的电压比外加电压越高。

Q 值影响电路的频率选择性。当电路处于谐振频率时,有最大的电流,偏离谐振频率时总电流减小。我们用I/I0 表示通过电容的电流与谐振电流的比值,即相对变化率。表示频率偏离谐振频率程度。图6 显示了I/I0 与ω/ω0关系曲线。这里有三条曲线,对应三个不同的Q 值,其中有Q1>Q2>Q3。从图中可看出当外加信号频率 ω 偏离电路的谐振频率ω0时,I/I0 均小于1。Q 值越高在一定的频偏下电流下降得越快,其谐振曲线越尖锐。也就是说电路的选择性是由电路的品质因素Q 所决定的,Q 值越高选择性越好。在电路板上会放置一些大的电容,通常是坦电容或电解电容。这类电容有很低的ESL,但是ESR 很高,因此Q 值很低,具有很宽的有效频率范围,非常适合板级电源滤波。

当电容安装到电路板上后,还会引入额外的寄生参数,从而引起谐振频率的偏移。充分理解电容的自谐振频率和安装谐振频率非常重要,在计算系统参数时,实际使用的是安装谐振频率,而不是自谐振频率,因为我们关注的是电容安装到电路板上之后的表现。电容在电路板上的安装通常包括一小段从焊盘拉出的引出线,两个或更多的过孔。我们知道,不论引线还是过孔都存在寄生电感。寄生电感是我们主要关注的重要参数,因为它对电容的特性影响最大。电容安装后,可以对其周围一小片区域有效去耦,这涉及到去耦半径问题,本文后面还要详细讲述。现在我们考察这样一种情况,电容要对距离它2 厘米处的一点去耦,这时寄生电感包括哪几部分。首先,电容自身存在寄生电感。从电容到达需要去耦区域的路径上包括焊盘、一小段引出线、过孔、2 厘米长的电源及地平面,这几个部分都存在寄生电感。相比较而言,过孔的寄生电感较大。可以用公式近似计算一个过孔的寄生电感有多大。公式为:

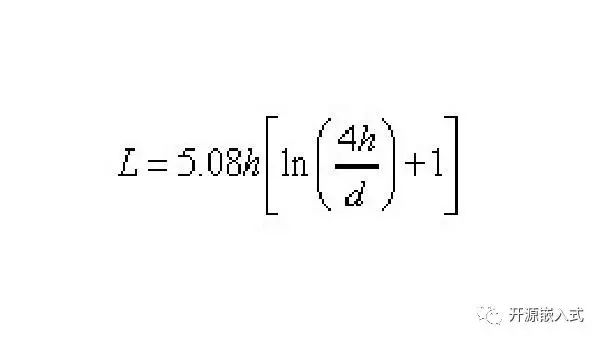

其中:L 是过孔的寄生电感,单位是nH。h 为过孔的长度,和板厚有关,单位是英寸。d为过孔的直径,单位是英寸。下面就计算一个常见的过孔的寄生电感,看看有多大,以便有一个感性认识。设过孔的长度为63mil(对应电路板的厚度 1.6 毫米,这一厚度的电路板很常见),过孔直径 8mil,根据上面公式得:

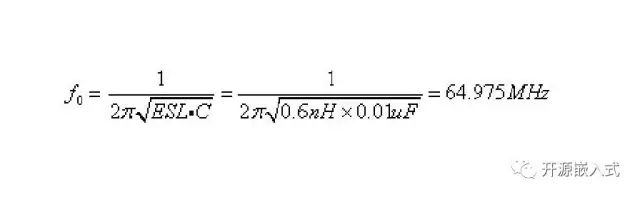

这一寄生电感比很多小封装电容自身的寄生电感要大,必须考虑它的影响。过孔的直径越大,寄生电感越小。过孔长度越长,电感越大。下面我们就以一个0805 封装0.01uF 电容为例,计算安装前后谐振频率的变化。参数如下:容值:C=0.01uF。电容自身等效串联电感:ESL=0.6 nH。安装后增加的寄生电感:Lmount=1.5nH。电容的自谐振频率:

安装后的总寄生电感:0.6+1.5=2.1nH。注意,实际上安装一个电容至少要两个过孔,寄生电感是串联的,如果只用两个过孔,则过孔引入的寄生电感就有3nH。但是在电容的每一端都并联几个过孔,可以有效减小总的寄生电感量,这和安装方法有关。安装后的谐振频率为:

可见,安装后电容的谐振频率发生了很大的偏移,使得小电容的高频去耦特性被消弱。在进行电路参数设计时,应以这个安装后的谐振频率计算,因为这才是电容在电路板上的实际表现。安装电感对电容的去耦特性产生很大影响,应尽量减小。实际上,如何最大程度的减小安装后的寄生电感,是一个非常重要的问题从电源系统的角度进行去耦设计先插一句题外话,很多人在看资料时会有这样的困惑,有的资料上说要对每个电源引脚加去耦电容,而另一些资料并不是按照每个电源引脚都加去偶电容来设计的,只是说在芯片周围放置多少电容,然后怎么放置,怎么打孔等等。那么到底哪种说法及做法正确呢?我在刚接触电路设计的时候也有这样的困惑。其实,两种方法都是正确的,只不过处理问题的角度不同。

责任编辑:lq

-

如何分清旁路电容与退耦电容?2023-10-16 2693

-

MCU退耦电容引发的EMC血案2021-11-05 834

-

从不同的角度来说明电容退耦原理2018-11-07 8877

-

电容去耦原理(解释十分透彻)2018-06-24 2145

-

电容退耦原理2018-01-26 1221

-

退耦电容的布置和布线2017-11-27 7558

-

去耦电容的作用和原理2017-11-12 14242

-

退耦电容2017-03-04 980

-

从储能、阻抗两种不同视角解析电容去耦原理2017-01-05 4474

-

滤波电容、去耦电容、旁路电容作用2013-03-08 8629

全部0条评论

快来发表一下你的评论吧 !