基于FPGA的DSP技术实现伺服控制器的应用方案与设计

处理器/DSP

描述

作者:晁智强,李华莹,陈强,苏力刚

引言

随着电液伺服控制理论的发展, 很多先进的控制策略被应用于电液伺服控制领域中。如: 文献[ 1 ]阐述了基本运算为不完全微分PID的滤波型二自由度控制算法, 针对飞行仿真转台用液压伺服系统的特点进行了仿真研究。文献[ 2 ] 研究了基于RBFNN 的PID控制在电液位置伺服系统中的应用。文献[ 3 ]对电液位置伺服系统采用滑模变结构控制, 用最优控制理论设计滑模平面, 均取得了良好效果。但大量文献均是理论与仿真研究, 大多的工业应用仍然以模拟电路实现PID控制算法为主, 主要原因是实现这些先进的控制算法的方法目前都是由负责控制的下位机用程序实现的, 而计算机易出现死机、掉电等情况, 这使液压系统可靠性和安全性都降低。

介绍了一种用基于FPGA的DSP技术来设计电液伺服系统控制器的方法。该方法克服了传统伺服控制器的一些不足, 可将许多复杂的实时控制算法硬件化实现, 并根据控制效果的优劣调整控制算法, 从而提高了控制器的控制效果、运算速度和可靠性。使用该方法, 设计者不必十分了解 FPGA (可编程逻辑门阵列) 和VHDL (硬件描述语言) , 在Matlab中便可设计出需要的伺服控制器。

1 现代DSP技术概述

近几年来, 应用数字信号处理技术设计的数字控制器被越来越多地应用到电液伺服系统中。在过去很长的一段时间里, 以美国TI公司 TMS320 系列为代表的DSP处理器几乎是数字信号处理应用系统的唯一选择。但面对当今迅速变化的DSP应用市场, 其硬件结构的不可变性, 早已显得力不从心。基于FPGA的现代DSP技术是用FPGA等可编程门阵列实现数字信号处理算法, 它是一种面向对象的DSP系统, 用户可根据需要来定制和配置自己的DSP系统。但是, 应用FPGA开发DSP系统专业性强, 使其应用受到很大限制。目前, 在利用FPGA进行DSP系统的开发应用上, 已有了全新的设计工具和设计流程, 世界两大FPGA生产厂商Xilinx公司和Altera公司都相继推出了自己的DSP解决方案。 DSP Builder就是Altera公司推出的一个面向DSP开发的系统级工具。MathsWork公司Matlab是功能强大的数学分析工具。 Simulink是Matlab的一个工具箱, 用于图形化建模仿真。DSP Builder作为Simulink中的一个工具箱,使得用FPGA设计 DSP系统可以通过Simulink的图形化界面进行。DSP Builder中的基本模块是以算法级的描述出现的, 易于用户从系统或者算法级进行理解, 甚至不需要十分了解FPGA 本身和硬件描述语言。这为传统控制系统领域的工程师开发基于FPGA的可靠控制系统芯片自顶向下的算法级设计提供了便利的条件。

2 电液位置伺服系统的数学模型

电液伺服系统是将电气和液压两种控制方式结合起来组成的系统。典型的电液系统方框图如图1 所示

控制元件可以是液压控制阀或液压伺服型变量泵等, 执行元件可以是液压缸或液压马达等。笔者结合文献[ 5 ] 带钢卷取电液伺服系统中电液伺服阀及液压缸的参数, 研究如何使用Matlab及DSP Builder来设计电液伺服系统控制器。

2.1 电液伺服阀

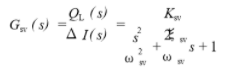

把电液伺服阀看作是一个二阶震荡环节, 其传递函数可以写成如下形式:

式中: Ksv为伺服阀的流量增益;

ωsv为伺服阀的固有频率;

ξsv为伺服阀的阻尼比。

采用TR2h7 /20EF型动圈双级滑阀式位置反馈式电液伺服阀, 其主要参数为: 额定电流ΔiR = 013A;供油压力 ps = 415MPa; 额定流量qR = 015 ×10- 3m3 / s;零位泄漏流量qc = 813 ×10 - 6m3 / s; 颤振电流幅值和频率分别为25mA 和50Hz。由实验可得出伺服阀固有频率ωsv = 112 rad / s, 阻尼比ξsv = 0.6。

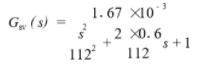

得到伺服阀的传递函数为:

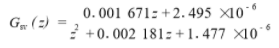

令控制系统采样周期为011 s, 可得伺服阀的脉冲传递函数为:

2.2 液压缸- 负载

负载为惯性负载, 则液压缸- 负载环节的传递函数可以写成如下形式:

式中: XP 为液压缸活塞位移;

QL 为负载流量;

AP 为液压缸有效工作面积;

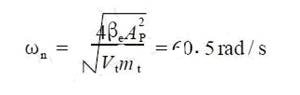

ωn 为液压缸的固有频率;

ξh为液压缸的阻尼比。

液压缸的技术参数为: 活塞直径D = 01125m, 活塞杆直径d = 0106m, 活塞行程H = ±01075m, 液压缸有效工作面积AP = 9145 ×10 - 3m2 , 系统总的压缩体积Vt = 2HAP +V管≈ 2148 ×10 - 3m3。

若液压油弹性模量βe = 7 ×108 Pa, 惯性负载质量mt = 2175 ×104 kg, 则液压缸- 负载环节的固有频率为:

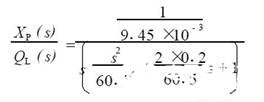

由于该环节的粘性阻尼系数和涉及到的伺服阀流量- 压力系数都较小, 取ξh = 012。则可得到液压缸- 负载环节的传递函数为:

令控制系统采样周期为011 s, 可得伺服阀的脉冲传递函数为:

3 基于DSP Builder的电液伺服系统PID控制器设计

3.1 控制系统结构设计

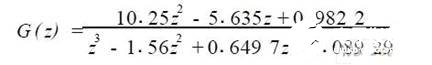

伺服控制器设计可以从与硬件完全无关的系统级开始, 首先利用Matlab强大的系统设计、分析能力和DSP Builder提供的模块完成控制系统的结构设计。本文控制器采用位置式PID控制器, 在Simulink搭建如图2所示的模型。

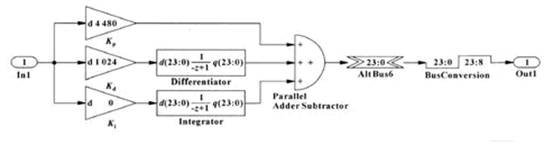

图2中, 顶层模型中PID Controllor为PID控制子系统, Input为控制输入端, Feedback 为反馈输入端,Function1与Function2 分别为伺服阀及液压缸- 负载的离散数学模型。值得注意的是PID 子系统中的Mask Type 必须设置为SubSystem AlteraBlockSet, 否则, 只能进行Simulink 仿真, 不能进行SingnalCom2p iler分析。PID控制子系统为实现PID算法部分, 其结构框图如图3所示。

图3 PID子系统结构框图

控制输入端及反馈输入端均采用了16 位精度。由于DSP Builder中尚不支持浮点数运算, 为了实现比例、积分、微分系数的精确可调, 在这里PID系数采用了位数转换的方法, 先将PID系数取成整型, 先放大数据值到24位, 而在并行加法器运算单元后用IO&Bus中的总线转换器单元对累加后的数据进行位数转换为16位, 可表示1 /256 = 01003 9整数倍的浮点数, 实现FPGA中的浮点数运算。

3.2 控制系统仿真

在本例中采用PD控制, 取比例系数为1715, 微分系数为4, 相应地设置Kp = 1715 ×256 = 4 480,Kd = 4 ×256 = 1 024, 得系统的闭环阶跃响应及正弦响应如图4、5所示。

3.3 控制器的FPGA实现

双击ServoSystem 模型中的SingnalComp iler模块,按照提示选择器件、综合及优化工具, 这里选择EP2C8型 FPGA, 综合工具选为QuartusⅡ, 优化方式选择Balanced, 综合考虑运算速度和耗费资源, 编译生成 ServoSystem1qpf。在QuartusⅡ中打开ServoSys2tem1qpf, 可以看到SingnalCompiler 为自动生成的 VHDL语言源代码。在QuartusⅡ中完成编译适配过程,生成的pof文件及sof文件可直接用于FPGA的编程配置。配置好的控制器, Input 端接计算机给定值, Feed2back端接位移反馈A /D芯片, Output端接D /A输出。

4 结论

以FPGA的系统级设计工具DSP Builder设计带钢卷取电液伺服系统控制器为例, 介绍了现代DSP技术在电液伺服系统中的应用。该方法可以解决复杂控制算法在电液伺服系统实际应用中, 分立元件的局限性, 软件实现的实时性、可靠性等方面的矛盾。由于有了像 DSP Builder这样的系统级设计工具,设计是从与硬件完全无关的Matlab系统级仿真开始,因此便于传统控制领域的工程师迅速地将算法级的构思应用于控制系统设计中, 从而可以将有限的精力专注于系统级算法的设计, 而避免陷入重复繁琐的电路设计中去。可以预见, 随着控制理论及电子技术的发展, 该方法在未来的电液伺服控制系统设计中将会得到广泛应用。

责任编辑:gt

-

一种基于FPGA的三轴伺服控制器的设计优化2023-09-04 1449

-

论述伺服驱动控制器的实现方法2022-09-20 3239

-

如何利用DSP与FPGA设计运动控制器?2019-08-06 3075

-

基于FPGA的三轴伺服控制器设计2019-07-16 2230

-

采用FPGA为控制核心实现优化三轴伺服控制器的设计2018-10-07 5631

-

基于DSP与FPGA的运动控制器的软硬件设计方案分析2017-10-25 1200

-

基于DSP_CPLD的四电动舵机伺服控制器设计2017-10-20 1159

-

基于DSP和FPGA的四轴伺服电机运动控制器2017-09-21 1292

-

基于矢量控制的高性能交流电机速度伺服控制器的FPGA实现2016-04-26 657

-

基于DSP与FPGA的运动控制器研究2012-10-26 1151

-

基于FPGA的机载三轴伺服控制器的设计优化2010-09-24 1504

-

DSP与FPGA设计的跟踪伺服运动控制技术2010-05-15 2004

-

基于DSP与FPGA的运动控制器设计2009-09-19 3795

全部0条评论

快来发表一下你的评论吧 !