基于可编程逻辑器件实现便携式数字正交锁相放大器的应用方案

可编程逻辑

描述

作者:谢桂辉,郑旭初,赵天明,刘子绪,赵 娟

引言

锁相放大器是一种用于测量动态信号的电子仪器,它的功能是从被噪声淹没的信号中测出某一频率的信号的相位和幅值。利用参考信号与被测信号的互相关特性,提取出与参考信号同频率和同相位的被测信号。相较于采用窄带滤波进行微弱信号检测,锁相放大器因采用相关检测技术,其Q值远高于模拟带通滤波器,且不存在中心频率不稳定的问题。由于参考信号与待测信号具有相关性,而与噪声不具有相关性,使通过相敏检测提取的信号中仅包含待测信号的幅度和相位信息,因而在微弱信号的高精度测量领域具有极大的应用价值。

数字锁相放大器因其具有动态范围大、测量误差小、不受运放温漂和直流偏置影响的优势,近年来逐渐取代了模拟锁相放大器,但常见的数字锁相放大器价格昂贵且不便于携带,不易于在特殊环境使用。

针对上述问题,本文研制了一款低成本的、可测试幅度最低达100 nV的便携式数字锁相放大器,适用于深海、野外等特殊环境的微弱信号检测。

1 系统方案论证

1.1 数字锁相放大器的原理论证

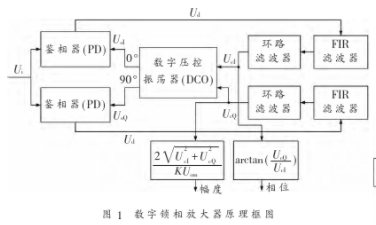

本款数字锁相放大器基于数字锁相环的原理,原理图如图1所示。

记待测信号为Ui(t),数字压控振荡器(Digital Control Oscillator,DCO)产生的一对正交信号分别为I路UoI(t)与Q路UoQ(t),如式(1)所示。

1.2 系统方案论证

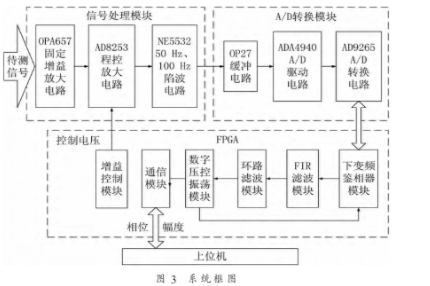

本系统以FPGA为核心,主要由信号处理模块、A/D转换模块和数字锁相放大模块构成。鉴于待测信号为纳伏级微弱信号,设计可变增益放大电路对待测信号进行放大,将待测信号处理为合适的幅度供ADC采样,由高速ADC采集后输入至FPGA测量,将测量得到的I/Q路数据通过串口通信传输到上位机,由上位机计算I/Q路数据,得到待测信号的实时频率和相位并进行显示。系统框图如图3所示。

2 系统硬件电路设计

2.1 信号处理模块

信号处理模块负责对待测信号进行处理以便于ADC采样。该模块由前级固定增益放大电路、中间级程控放大电路和末级工频滤波电路构成。

前级固定增益电路采用宽带低噪运算放大器OPA657。该芯片的带宽增益积达1.6 GHz,在90 MHz以下具有0.1 dB的增益平坦度,输入电压噪声4.8 nV/

。设计本级固定增益为60 dB,允许输入信号频率最大值为100 kHz、最大幅度为1 μV,实际需求的带宽增益积为:GBW=G×f=1 000×100 kHz=100 MHz,芯片满足设计要求。

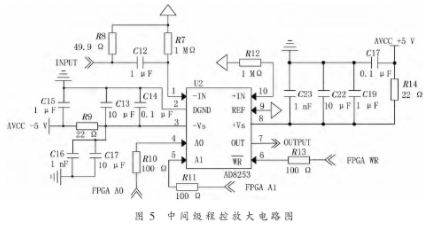

中间级程控放大电路采用数控增益仪表放大器AD8253。该芯片的增益分为4档,可根据2位增益控制字调节,在增益为40 dB时,-3 dB带宽为550 kHz,考虑到前级允许输入的信号最大频率为100 kHz,故设计芯片增益倍数最高为40 dB。设计本级允许输出信号最大幅度为1 V,所需压摆率为:SR=2πfV=2π×0.1 MHz×1 V≈0.628 V/μs,该芯片的压摆率为20 V/μs,满足设计要求。

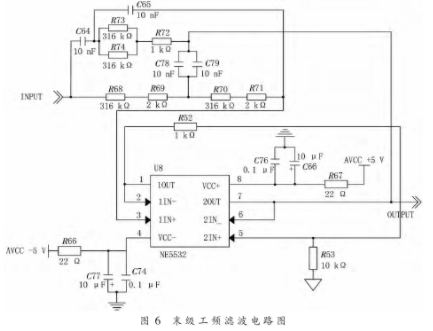

末级工频滤波电路采用低噪运算放大器NE5532。该芯片的输入电压噪声小于5 nV/

,压摆率为9 V/μs,本级允许的输入信号最大频率为100 kHz、最大幅度为1 V,所需压摆率为0.628 V/μs,满足系统对压摆率的要求。为避免工频干扰,本级设计两级带阻滤波器电路,分别将50 Hz与100 Hz作为中心频率,更好地滤除工频噪声。

本模块设计的增益范围为60/80/100 dB三档,输入电压噪声9 nV/

,上述电路如图4~图6所示。

2.2 模数转换模块

模数转换(以下简称A/D转换)模块负责将放大后的待测信号从模拟量转化为数字量,该模块由隔离电路、模数转换驱动电路(以下简称ADC驱动电路)和模数转换电路(以下简称ADC电路)构成。

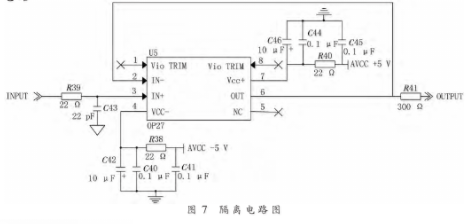

隔离电路采用低噪运算放大器OP27。考虑到将模拟量的待测信号不加缓冲的输入A/D转换模块,易引起数字信号对模拟信号的干扰,导致信号畸变,故设计该电路以隔离模拟信号与数字信号的影响。

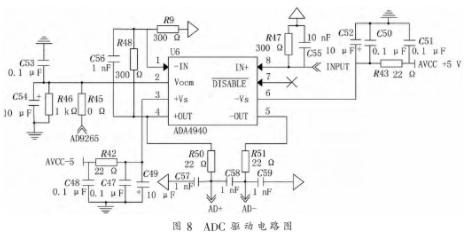

ADC驱动电路采用低功耗、低失真的差分ADC驱动器ADA4940。对于后级的差分输入ADC而言,差分输入的信号能够最大程度地发挥ADC的共模抑制性能,改善信噪比,因此设计该电路以将单端信号转化为差分信号。

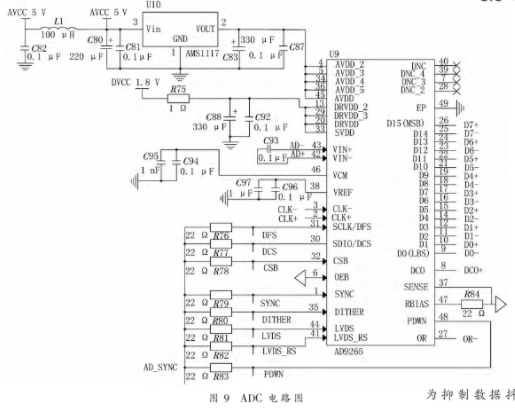

ADC电路采用高速模数转换器AD9265,该芯片具有16 bit的采样精度与125 MS/s的采样率,设计其对待测信号每个周期采样1 024个点,则芯片能够对小于122 kHz的信号进行采样,高于系统允许的最大待测信号频率。

本模块将模拟信号低失真的转化为数字信号并传输到FPGA以便于数字锁相放大,电路图如图7~图9所示。

3 系统软件设计

系统的软件部分包括下变频鉴相器模块、环路滤波模块、数字压控振荡模块、通信模块和上位机模块。其中,数字压控振荡模块产生正交的双路信号,与待测信号一同输入下变频鉴相器和环路滤波器进行处理,输出结果作为数字压控振荡器的控制信号调整其输出信号频率和相位,3个模块构成数字锁相环部分。通信模块完成FPGA与上位机的数据通信。上位机模块负责处理通信模块上传的数据,使测试结果更简洁直观,程序运行流畅,界面友好。

3.1 下变频鉴相模块

下变频鉴相器是用于比较输入信号与压控振荡器输出信号的相位,它的输出电压是对应于输入信号相位差的函数。

该模块将待测信号分别与一对正交信号进行混频,两路混频后的信号中都含有一对和频分量与差频分量,经过后级滤波器处理后得到所需差频分量,当数字锁相环进入相位锁定状态时,该信号用于计算,以得到待测信号的幅度与相位信息。

3.2 FIR滤波模块

FIR滤波模块采用一阶滞后滤波算法,一阶滞后滤波的结果受本次采样值与上次滤波输出值影响,使输出对输入有反馈作用,其公式见式(7):

本次采样值和上次滤波输出值对本次输出采样值的影响程度由滤波系数决定,滤波系数越小,滤波平稳度越高;滤波系数越大,滤波灵敏度越高。

为使算法在数据变化较快时具有较高的灵敏度,在数据变化较慢时具有较高的平稳度,增加滤波系数自适应算法:判断本次数据变化与上次数据变化是否同向,若为反向,认为采样数据出现抖动,将滤波系数还原为初始值;若为同向,判断数据变化量是否超过设定值,若没有超过设定值,认为数据变化较慢,滤波系数调整步长选择低档,反之,认为数据变化较快,滤波系数调整步长选择高档。

3.3 数字压控振荡模块

当没有控制信号输入时,数字压控振荡器的输出信号为设定的初始振荡信号和它的正交信号。以初始震荡信号为例,该信号与待测信号经鉴相器与环路滤波器处理后得到数字压控振荡器的频率控制信号,振荡信号的频率与频率控制信号的幅度正相关,随着振荡信号频率的调整,振荡信号与待测信号的差频将趋于0,使频率控制信号趋于直流信号,振荡信号的频率和相位随之稳定,使锁相环进入相位锁定状态。

3.4 上位机模块

本系统选择LabVIEW作为上位机的开发环境。上位机的主要功能包括放大器增益设置、输出信号模式设置、解调频率设置、内外参考设置、测量结果显示等。

为抑制数据抖动和可能出现的部分极值对测量结果产生的影响,兼顾数据处理的实时性,采用了如下算法:对最近的M个测量数据取平均作为实际测量值显示。在此基础上,增加对异常数据的检测,若异常数据非连续出现,则剔除异常数据,当连续出现N个异常数据时,认为输入信号已被更新,重新计算均值作为新的信号测量结果。M值影响数据更新的速度和数据的稳定性,N值影响数据更新的灵敏度,使其能在输入信号改变后及时响应,不再依赖上一个信号的平均值,L值影响极值的有效识别。本系统选择M值为10,N值为3,L值为当前平均值的25%。

上位机具有一键复制功能,可以将接收的数据按序复制,便于用于其他处理。并且可以对波形的局部进行缩放操作,易于观察波形细节。上位机整体界面友好,显示直观,便于使用者操作,上位机界面如图10所示。

4 测试数据及分析

4.1 系统整体噪声测试

测试条件:使用傅里叶频谱分析仪SR760进行测试。

测试方法:在不接入待测信号的条件下将系统输出噪声进行2 000倍放大并测试。

测试结果:实际系统噪声峰值Vtop约为17.8 μVrms/

,如图11所示。

4.2 系统锁相精度测试

测试条件:使用160 MHz的RIGOL数字信号源、100 MHz的Tektronix数字存储示波器和自制100 dB衰减网络。

测试方法:将经100 dB衰减网络处理后的信号源信号作为待测信号,分级测量系统对于小信号和大信号的测量能力。

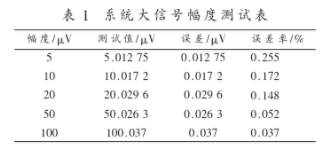

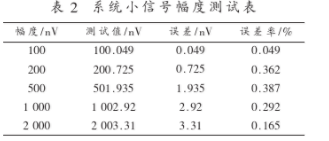

测试结果:测试结果以图与表的形式体现,表1为系统的大信号测试结果,表2为系统的小信号测试结果,图12为上位机程序显示的500次测量的稳定度曲线。

结果分析:图12中的曲线表明系统在数百次测试中仅有误差允许范围内的围绕中心值的抖动,这种测量抖动是易于剔除的,对测试精度的影响较小,多次测量中没有出现偏离抖动范围的极端值,系统的测量稳定度较高。由表1和表2的误差率统计也可以看出,系统在可测量范围内误差率小于0.4%,在部分区段误差率小于0.1%,测量精度较高。

5 结论

本系统设计并实现了一个便携式数字正交锁相放大器,该放大器仪具有100 nV~100 μV的幅度测量范围、60 dB的动态范围,幅度精度高于0.4%,相位精度达0.001°。采用便携化设计,适用于野外、深海等恶劣环境。系统采用模块化设计思路,可扩展性强,性能稳定,易于维护,具有很好的应用价值。

责任编辑:gt

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4590

-

可编程逻辑器件测试2023-06-06 1314

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 2260

-

可编程逻辑器件(书皮)2022-07-10 796

-

PLD可编程逻辑器件2021-07-22 2326

-

数字电子技术-- 可编程逻辑器件2017-03-05 2957

-

数字电子技术--可编程逻辑器件2016-12-12 1208

-

可编程逻辑器件2014-04-15 3679

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1167

-

可编程逻辑器件基础及应用实验指导书2010-03-24 788

-

基于可编程逻辑器件的数字电路设计2009-11-16 1944

-

什么是PLD(可编程逻辑器件)2009-06-20 30060

-

可编程逻辑器件设计2006-03-25 1185

全部0条评论

快来发表一下你的评论吧 !