基于EP2C8Q208C7和AD9858实现雷达信号源的应用方案

可编程逻辑

描述

1 引言

一般的雷达信号源实现主要有三种方式:第一种方式是采用DDS和MCU控制器件结合的方式;第二种是DDS、MCU控制器件和FPGA等可编程器件结合的方式:第三种是由FPGA等可编程器件实现DDS的方式。第一种方式利用专用DDS器件可以产生具有较好的杂散抑制和谐波抑制性能的雷达波形。控制简单。但不易于实现复杂波形的控制时序,灵活性差:第二种方式不仅可以产生有较好杂散抑制性能的雷达波形。还易于产生各种复杂的雷达信号,但附加了控制器和时序生成器,增大了电路的复杂性:第三种方式适用于产生特定要求的信号,但开发周期长,杂散抑制和谐波抑制指标难以达到专用DDS的水平。

随着FPGA工艺的不断发展,设计人员在FPGA上嵌入软核处理器成为可能,即所谓的SoPC(System on a Programmable Chip)解决方案,它是指在FPGA内部嵌入包括CPU在内的各种IP,组成一个完整系统.在单片FPGA内部实现一个完整系统功能。本文采用Altera公司提供的SoPC Builder工具将Nios II CPU软核嵌入到Cyclone II系列FPGA内部以控制高性能DDS器件AD9858,并采用该片FPGA产生其他控制时序。这样既充分利用了专用DDS的良好特性和完备功能,同时又大大减少处理器外围扩展元件数目,提高系统集成度,降低外围电路布局走线的复杂度,提高系统的抗干扰能力,便于今后升级扩展。

2 器件简介

2.1 CycloneⅡ系列FPGA及NiosⅡ简介

Cyclone II系列FPGA采用TSMC 90 nm低k绝缘工艺,具有完备的性能和极低的功耗,而价格与ASIC相当。它具有多达68 416个逻辑单元(LE)和1.1 Mbit嵌入式存储器,具备很多优化的特性,包括多达150个嵌入18×18乘法器、专用外部存储器接口电路、4 Kbit嵌入存储块、锁相环(PLL)和高速差分I/O能力。其差分I/O信号可提供更好的噪声容限,产生更低的电子干扰(EMI),并降低了功耗。其增强型锁相环(PLL)能提供先进的时钟管理能力。它还支持:Nios II系列32位RISC嵌入式处理器。

Nios II是Altera公司推出的第二代IP软核处理器,具有超过200 DMIP的性能,并与其他IP核构成SOPC系统的主要部分。用户可以通过自定义逻辑的方法在SoPC设计中添加自己开发的IP核,充分体现了SoPC设计灵活和高效的优越性。Nios II系列嵌入式处理器包括三种CPU内核:高性能内核(Nios II/f,快速)、低成本内核(Nios II/e,经济)和性价比均衡内核(Nios II/s,标准)。采用Quartus II设计软件集成的SoPC Builder工具,可以在系统中轻松嵌入Nios II处理器。本系统设计采用该系列EP2C8Q208C7。

2.2 AD9858简介

AD9858是ADI公司推出的直接数字频率合成器(DDS),其10-bit DAC具有高达1 GS/s模拟输出,频率高达400 MHz。它具有快速调频和精细调谐分辨率的特性,可快速产生单频脉冲、线性调频及相位编码信号。AD9858的杂散抑制性能和谐波抑制性能也非常突出,当输出40 MHz信号时,±1 MHz带宽内的数模转换SFDR为一87 dBc;输出180 MHz信号时。±1 MHz带宽内的数/模转换SFDR为-84 dBc,能满足高性能雷达低杂散、低相位噪声的要求。AD9858内部集成有电荷泵(CP)、相频检测器(PFD)和模拟混频器,可以将高速DDS和锁相环(PLL)及混频器结合使用。AD9858具有对输入时钟二分频功能,外部时钟高达2 GHz。对AD9858进行配置也非常容易,只需把控制字通过并行或串行方式写入片上的控制寄存器即可。AD9858比先前的解决方案速度提高了3倍,功耗却没有增加,还具有可编程的全睡眠模式,因而适应用于无线设备以及军事系统的设计。

AD9858的优势在于其具有四套频率调谐寄存器(FTW)及四个相位调整寄存器(POW),这使得它可以方便快速产生线性调频信号以及相位编码信号,而且这四个控制寄存器的选择是由外部选择信号PS1、PS0实现的,可大大减少了子码间的转换时间。

3 系统设计方案

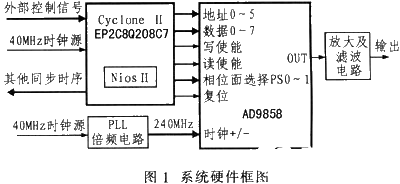

3.1 硬件结构

本系统硬件框图如图1所示。FPGA和AD9858的并行数据/地址总线相连,提供读/写信号、复位信号和PS0、PS1信号。AD9858的输入时钟由外部时钟源电路提供,采用差分电平标准。AD9858的输出首先经过放大电路,使其满足功率要求,然后再经过滤波电路。FPGA接收主机的波形选择控制信号,产生各种同步时序,并为内嵌Nios II CPU提供中断信号。Nios II CPU响应不同的中断,通过并行方式为AD9858提供各种控制字和初始化,从而产生不同的雷达波形。

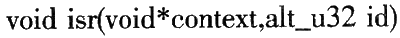

其中Nios II CPU是由Quartus II设计软件集成的SoPC Builder工具生成。用户可以通过SoPCBuilder的图形用户界面从Ahera公司提供的IP元件库中选取一些组件,如Nios II、DMA、SRAM、Flash等等,并根据实际需要设置这些IP的配置参数。用户还可以自行编写HDL代码模块作为用户自定义逻辑添加到SoPC Builder中。由于本系统功能相对简单,所以采用Cyclone II片内的嵌入式RAM构成Nios II的数据和程序存储区。对于其他功能复杂、控制程序较大的设计,应扩展片外SRAM和Flash作为Nios II的数据和程序存储区。

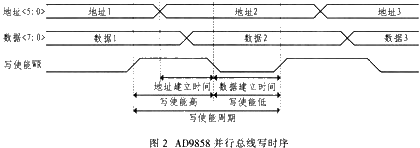

对AD9858的控制实质就是通过其并行数据和地址总线传送控制字,可通过在SoPC Builder中为AD9858生成一个用户自定义逻辑接口实现。但考虑到AD9858的读写时序比较简单,也可以直接采用Nios II现有IP元件库里的PIO来生成所需要的读写时序。PIO (Parallel Input/Output)是SoPCBuilder中最常用的IP之一,它有输入、输出以及双向口三种类型。另外,它还支持中断检测,不过中断检测及处理只在其作为输入设备时可用。AD9858并行总线的写时序如图2所示。

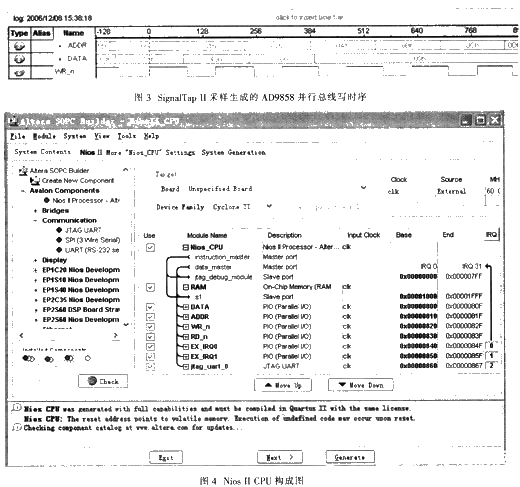

需要注意的是,写使能信号(低有效)的最小周期为9 ns,为低电平的时间最少是3 ns,为高电平的时间最少是6 ns,而地址和数据信号的建立时间分别为3 ns和3.5 ns。图3为用嵌入式逻辑分析仪SignalTap II采样的一段用PIO生成的AD9858并行总线写时序。完全满足设计要求。

最终生成的Nios II系统如图4所示。其中,jtag_uart_0是为了调试时便于Nios II和主机通信而编写的,也可以省去。外部中断EX_IRQ0和EX_IRQ1也是用PIO实现。

DDS输出信号的质量取决于为AD9858提供工作时钟的外部时钟源,本系统采用40 MHz高性能晶体振荡器,然后通过PLL倍频电路获得240 MHz参考时钟。同时将时钟转换成符合AD9858要求的差分信号,以降低共模干扰。输出信号的滤波器设计好坏也直接影响到最终输出信号的质量。若采用单一的带通滤波器抑制DDS输出杂散,对频率合成器带内杂散性能并没有提高。采用滤波器组则会带来电路复杂、增大体积以及延长频率切换时间等问题。目前,一般是通过DDS输出驱动倍频器链,达到提高输出频谱和拓展频谱带宽的要求,但同时也会导致DDS输出带内频谱纯度恶化。印制板设计要满足高速数模混合电路电磁兼容方面的设计原则,以使系统性能更佳。

3.2 软件设计

本系统的软件设计采用Altera公司提供的E-DA设计工具Quartus II,主要包括两个部分:首先是由Ouartus II集成的SoPC Builder工具生成Nios IICPU并进行相应的设置,用原理图和HDL语言设计。FPGA的其他时序控制程序;其次是用Quarus II集成的Nios II IDE综合开发环境为Nios II CPU编写控制AD9858的程序,采用C/C++语言编写,分为主程序模块和中断响应程序模块。

因为本设计只采用片内RAM作为Nios II(CPU的程序和数据存储区,所以在Nios II IDE综合开发环境下前先对项目进行一些编译设置,以使编译器编译出效率更高、占用空间更小的代码。在用户工程属性对话框内将Optimization Level设为“Opti-mize size(-Os)”,在系统库工程属性对话框内也做同样的设置,同时将Max file descriptors设为4,清除“Clean exit(flush buffers)”和“Link with profiling li-brary”前的选中框,选中“Reduced device drivers”和“Small C Library”。

AD9858有两种工作模式:单频模式和扫频模式。单频模式的配置比较简单,只需将控制寄存器(CFR)、频率调谐字(FTW)配置完毕,即可打开该功能。频率扫描模式需要配置的寄存器有控制寄存器(CFR)、频率调谐字(Frw)、增量频率调谐字(DFTW)、增量频率斜率控制字(DFRRW)和相位偏移字(POW)。其中,控制寄存器一共有4个字节,地址分别为0x00、0x01、0x02和0x03。在本设计中,未用到PLL功能.故与PLL有关的控制字均置为无效。0x01的Bit7为扫频使能位,将其置1打开扫频功能。上电复位以后,Nios II CPU处于等待中断状态,它根据FPGA的时序控制程序发出的中断信号执行相应的中断响应程序,通过对各种寄存器赋值可产生线性调频或相位编码信号。

关于采用AD9858产生线性调频信号还需进一步说明,其工作原理是:指定频率起始点和步进频率,频率以系统时钟的1/8或其整数倍累加,但是在没有指定上限频率的情况下,会一直扫到1/2参考时钟频率处,即奈奎斯特频率,所以需要外部定时器控制何时停止频率累加。通过FPGA的时序控制程序可以灵活地设定定时器,实现对上限频率精确控制。

Nios II的中断程序编程需要调用API函数alt_irq_register()向系统。ISR注册用户ISR。其原形为:

其中,id代表被服务的中断向量号;context是运行参数指针,作为第一个参数传给用户。ISR;isr是函数指针。指向用户。ISR入口。如果注册成功,函数返回0,并允许全局中断及被服务中断;如果不成功则返回非0值。

用户定义的用户ISR程序要符合统一的原形定义,即:

其中,入口参数与返回值要严格按标准形式定义。否则系统ISR,将不能正确对其调用。

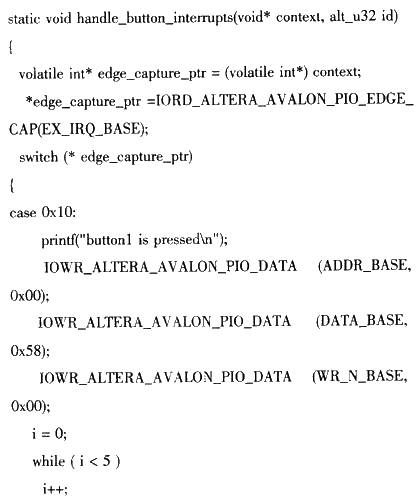

中断程序的部分代码如下:

4 结束语

系统通过一片FPGA实现内嵌CPU软核控制外围DDS,同时形成各种系统所需的同步控制时序。实验证明其调频性能和稳定精度等各项指标均达到设计要求。SoPC是目前嵌入式系统设计的一个新趋势,由于FPGA的可编程特性,可以在不改变任何外围电路的情况下灵活地对系统进行重新配置,软硬件升级。此外,还可以实现对Nios II CPU的RTOS操作系统的移植,以实现更丰富的功能和产生更为复杂的雷达波形,从而简化雷达信号源的设计,提高系统的集成度。

责任编辑:gt

-

AD9858实现雷达宽带调频源设计2011-10-08 3183

-

采用AD9858和AD4360_2实现UHF波段频率合成系统的设计2018-12-18 5755

-

基于EP2C8Q208C和AD9858芯片实现雷达信号源的应用设计2020-07-27 4952

-

用DDS器件AD9858实现复杂雷达信号源 (图)2008-09-22 3743

-

各位大神,求AD9858的外围电路,DAC输出,急。。2015-03-28 3400

-

AD9858 无信号输出2015-08-14 9158

-

请问AD9858参考信号REFCLK是采用的何种方式提供的2018-11-16 1814

-

采用AD9858实现雷达信号源的应用设计2020-11-24 1583

-

回收EP2C8Q208C8N,收购EP2C8Q208C8N2020-12-07 600

-

DDS工作原理是?用DDS芯片AD9858宽带雷达信号源要设计最佳?2021-04-06 2814

-

如何利用AD9858设计雷达宽带调频源?2021-04-07 1292

-

AD9858具有哪些性能特点及应用?2021-04-08 1458

-

基于AD9858宽带雷达信号源的设计及应用2010-07-21 941

-

DDS器件AD9858实现复杂雷达信号源2011-08-24 3421

-

可编程模拟雷达信号源的设计2011-10-19 836

全部0条评论

快来发表一下你的评论吧 !