基于ADSP-BF561实现LCD显示界面控制系统的设计

处理器/DSP

描述

某控制信号处理系统中,选用ADSP-BF561作为主控机,外接键盘,LCD显示屏,标准RS232接口,实时时钟等,通过DSP编程来实现对各个功能模块控制,同时产生多路数字IO信号。该控制系统还包括电源、时钟、CPLD、FLASH,JTAG调试器、复位电路等基本组成部分,系统框图如图1所示。

图1 基于ADSP-BF561控制信号处理系统框图

系统电源模块选用TPS54350来实现,外围电路不同RC值,可以构成不同输出电压,这里需要产生是5V、3.3V、1.25V三种电压。时钟电路由48MHz晶振电路来实现,其输出作为DSP外围时钟和CPLD时钟。FLASH用于存储用户应用程序,JTAG调试口在DSP电路设计中也是必不可少。后面对各个部分一一介绍,特别是对复位电路,数字IO信号产生,以及RS232接口进行详细介绍。

1.键盘

键盘选用是4×4扫描键盘,如图1所示,由BlackfinGPIO接口PF5~PF12来实现。其中,KEY_GP3~KEY_GP0为行线输入端,初始化为带上拉电阻输入口,中断使能(下降沿触发);KEY_GP7~KEY_GP4为列线输出端,初始化为输出低电平。键盘扫描方法同常规扫描键盘方法相同。

图 1 扫描键盘结构图

2. LCD显示屏

LCD显示屏采用320x240LCD液晶模块。320x240液晶模块配用sed1335驱动接口板,sed1335驱动接口板上配用32KRAM。LCD除了读写信号线由Blackfin读写信号来控制以外, 8位数据线由Blackfin低8位数据线锁存输出,以及其使能信号由BlackfinAMS3控制,LCD地址分配为0x2C000000。电路连接如图2所示。在对LCD进行控制时,除了要建立在LCD上显示汉字和英文字库以外,还要编写对sed1335底层驱动程序。这可以在LCD自带驱动程序基础上,进行代码移植,把它改写成适合BF561DSP程序。

图 2 LCD连接示意图

3.实时时钟

控制系统实时时钟选用了芯片DS1337来实现。DS1337是一个低功耗串行实时时钟芯片,它有24h/12h制两种模式,它可以输出年、月、日、分、时、秒形式。它采用I2C协议,BlackfinPF0和PF1作为I2CCLK和DATA,而PF3作为实时时钟中断FLAG,其电路连接示意图如图3所示。

图3 实时时钟电路连接示意图

4.复位电路

为了保证DSP在上电或按下复位键时能可靠复位,一般加一个复位延时电路,选用MAX708S来完成,如图4所示。

图4 复位电路

在上电过程中,RESET信号会在VCC达到稳定电压后一段时间内(约200ms)保持为高,然后再变低。 信号为RESET“NOT”,即 会相对VCC延时一段时间后再变高,如图5所示。这样,在DSP各电源电压已稳定情况下,DSP复位信号仍为低有效,就可以保证DSP正常复位。

图5 上电过程中 信号

在上电以后,如果手动按下开关,使得MR上信号由高→低→高,产生一个低脉冲,这时, 管脚上也会输出一个低脉冲,只是其低电平持续时间比MR上低电平持续时间长200ms左右,以保证DSP复位可靠完成,如图6所示。

图6 手动复位时 信号

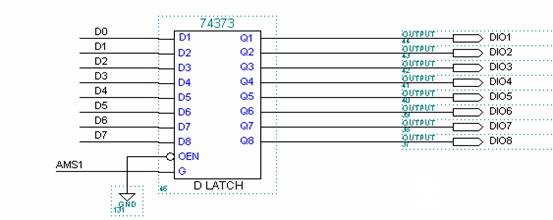

5. 数字IO信号产生

在该控制系统中,要求产生8路数字IO信号。如果把这8路数字IO信号看成一个8bit数,则需产生一个有限长度非方波编码信号,如下图所示。在T0时刻需要产生数字IO信号为STAT0,比如说10010101;在在T1时刻需要产生STAT1,…,在Tn时刻需要产生STATn,而且T0可能不等于T1或Tn,STAT状态也各不相同。

图7数字IO信号状态

这里选用BF561看门狗定时器(Watchdog Timer)来实现。在看门狗定时器操作中,先将计数值写入寄存器WDOG_CNT中,然后看门狗定时器自动将WDOG_CNT值写入寄存器WDOG_STAT。接着通过寄存器WDOG_CTL使能Watchdog Timer,看门狗定时器开始计数,逐次减小WDOG_STAT值,直至为0,这时预先编写程序事件就会发生。要想输出一个8bit数据,只需往某地址单元写数,对应数据线就会写出该数据。为了把该数据保持一段时间(Tx长度),还需使用锁存器将该数据锁住。所以在BF561DSP程序中先定义了数字IO信号对应中断事件,且中断优先级较高,这是为了保证定时精确度,防止别事件干扰。

register_handler(ik_ivg9, DIO_WDOGA_ISR);

然后在中断事件里,把当前要写入数据写到某地址单元上,然后使能Watchdog Timer,再将定时器值写入WDOG_CNT中。定时器计数是以sclk为基准,程序代码如下:

*pDIO_Data_Port = codes;

*pWDOGA_CTL =DISABLE_WDOG;

*pWDOGA_CTL |=WDOG_EXPIRED_BIT;

*pWDOGA_CNT =times;

*pWDOGA_CTL = ENABLE_GPI;

codes和times就是当前要产生数字IO编码和长度。由于是一系列编码,可以用数组索引形式,将当前值写入。而我们事先定义DIO_Data_Port地址为0x24000000,这对应BF561AMS1地址空间,所以用AMS1作为锁存器使能信号,将数据线上数据通过锁存器以后再输出,如下图所示

图8 数字IO锁存器

6.标准RS232接口

为了让控制系统与计算机之间可以进行数据相互传递,系统采用MAX3232芯片来实现,如图9所示:

图9 BF561与计算机之间串口通信框图

BF561UART遵循异步串行通信协议,包括:5-8个数据位;1、11/2、2个停止位;有/无奇偶检验。而波特率满足

其中,SCLK是DSP系统时钟频率,Divisor值介于1~65536,可以由timer寄存器相应值得到,满足关系式

在BF561初始化设置中,将UART设为8bit数据模式,同时将Timer2设置为WDTH_CAP模式,用Timer2去捕获串口数据变化率,而Timer2位于TMRS8寄存器里,程序初始化代码如下:

*pUART_LCR = WLS(8);

*pUART_MCR = LOOP_ENA;

*pTMRS8_DISABLE = TIMDIS2;

*pTMRS8_STATUS = TRUN2 | TOVL_ERR2 | TIMIL2;

*pTIMER2_CONFIG = TIN_SEL | IRQ_ENA | PERIOD_CNT | WDTH_CAP;

*pTMRS8_ENABLE = TIMEN2;

*pUART_GCTL = UCEN;

在程序一开始,就会按照初始化设置进行自动波特率检测。当有字符输入时,timer会测量连续2次下降沿宽度,并返回到timer所对应period寄存器里。比如说,如果发送”@”(0x40h)作为自动波特率检测,发送时包括起始位,总共为8bit,如图10所示。

图10 自动波特率检测字符”@”(0x40h)

此处period大小如上图所示,捕获UART bits为8位,所以得到

再根据波特率公式,就可以求得波特率大小。此段程序代码如下:

Period = *pTIMER2_PERIOD; //返回period值

Divisor = Period 》》 7; //右移7bit就相当于除以16×8

BaudRate = SYSCLK/16/divisor; //得到波特率

结论

整个控制系统是以LCD显示界面为基础,按提示进行相应键盘操作。经过测试,该系统各部分工作正常,无相互干扰现象。实时时钟定时精确,可以达到秒级。数字IO输出波形编码无乱码,定时精度可达毫秒级。RS232接口传输数据时,以高达115200bit/s波特率传输,误码率小于5%。该控制系统已成功应用于某雷达系统控制子系统。

责任编辑:gt

-

EE-256:使用ADSP-BF561 Blackfin处理器作为TFT-LCD控制器2025-01-07 573

-

AN-813: ADSP-BF533/ADSP-BF561 Blackfin处理器与高速并行ADC接口2025-01-06 401

-

使用ADSP-BF561 Blackfin®处理器作为TFT-LCD控制器的EE-2562021-06-17 998

-

怎么实现基于ADSP-BF561的H.264编码器设计?2021-06-07 1329

-

ADSP-BF561 EZ-KIT Lite<sup>®</sup>评估系统手册2021-05-18 873

-

ADSP-BF561黑体-欧美/SUV-Processor硬件参考2021-05-13 1185

-

ADSP-BF561 Blackfin版本0.3、0.5异常列表2021-05-12 965

-

EE-256:使用ADSP-BF561 Blackfin®处理器作为TFT-LCD控制器2021-04-13 1098

-

AN-813: ADSP-BF533/ADSP-BF561 Blackn®处理器与高速并行ADC接口2021-03-21 970

-

ADSP-BF561 Blackfin对称多处理器,用于消费类多媒体2019-02-22 848

-

ADSP-BF561原装开发板的PCB图2018-11-20 1287

-

请问ADSP-BF561中文资料为什么无法下载 ?2018-09-29 1852

-

基于ADSP-BF561的嵌入式键盘设计与实现2010-01-07 874

-

基于ADSP-BF561 的数字摄像系统设计2008-10-16 1772

全部0条评论

快来发表一下你的评论吧 !