基于CMOS工艺实现器件级噪声优化方法的研究

描述

1 引 言

利用高速线扫描摄像机进行监控,具有在线监控、高精度和高速度的特点,一般常见的线扫描摄像机,感光器上的每个像素在进行动态扫描时,每次仅对移动中的物体做一次曝光,而时间延迟积分(TDI)电路具备较多且有效的积分时间,从而增强信号的输出强度。目前,TDI技术的研究多局限于CCD工艺。CCD器件是实现TDI的理想器件,它能够实现无噪声的电荷累加,但传统CCD图像传感器技术存在驱动电路和信号处理电路难与CCD成像阵列单片集成,需要较高的工作电压,不能与深亚微米超大规模集成电路工艺兼容,图像信息不能随机读取等欠缺。随着CMOS集成电路工艺和开关电容电路设计技术的发展,CMOS图像传感的光电转换、读出和A/D转换等功能已实现单芯片,但目前有关利用CMOS工艺实现线阵TDI的技术鲜有报道,其主要技术难点为如何实现低噪声的信号累加。本文在研究CMOS电路噪声的基础上提出了基于CMOS工艺采用开关电容电路实现TDI功能的电路结构,详细分析了电路的噪声,提出了器件级噪声优化方法,采用SMIC 0.35 μm CMOS工艺进行了仿真,仿真结果表明,该电路能够实现TDI功能,并且具有低噪声的特性。

2 TDI工作原理

TDI是指对同一移动中的物体进行多次曝光并将其积累。由于感光器积累多次的入射光,图像信号及整体亮度也相应大幅提升。在对入射信号累加的同时,对噪声信号也进行了累加,因此低噪声的电路设计成了设计中的重点。CMOS-TDI结构如图1所示,它类似于普通面阵CMOS图像传感器,n级的TDI由n行像素单元、积分阵列组和列并行ADC组成。其中,m为像素单元的个数,n为级数。本设计中,n=32。

3 电路设计

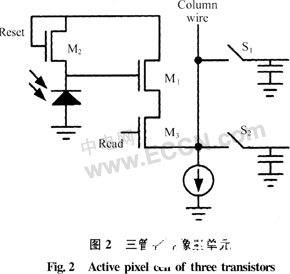

3.1 光敏单元的设计

像素单元的物理结构包括光电二极管、行选信号、电源、地信号和源跟随晶体管等。由于有源像素相对于无源像素有低读出噪声、可集成到更大规模阵列和高速读出等优势,采用三管有源像素结构。该结构的填充系数相对较高,而且寻址方式简单。其电路结构如图2所示。

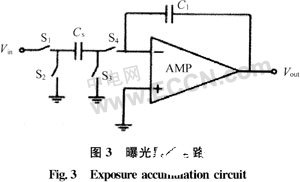

3.2 积分电路的设计

采用的积分器如图3所示,包括采样电容、积分电容和两相不交迭时钟。工作过程为:在采样模式下,S1和S3闭合,S2和S4断开,采样电容CS两端的电压追踪输入信号,积分电容C1保持初始值不变。在向积分模式的转换过程中,S1和S3断开,S2和S4闭合,存储在Cs上的电荷通过虚地点传到CI上。采用适当的时序,使S3和S1之前断开,可以避免与输入有关的电荷注入。

3.3 开关电容电路噪声

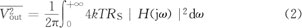

3.3.1 采样相噪声

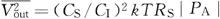

首先分析积分器采样相噪声。采样网络及采样噪声的电路模型如图4所示,此时积分器可等同于RC网络。值得注意的是,若采样时间远大于RC网络的时间常数,即有充分的时间使之建立,开关上的压降在采样相结束时近似为0。同时,开关的动作过程使开关的Si和氧化物界面状态复位,从而阻止低频1/f噪声的积累。所以1/f噪声在采样阶段可以忽略。

用作开关作用的MOS管,其热噪声谱密度可表示为

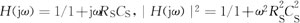

其中:Rs为MOS管的等效电阻;γ=1。VOUT端噪声功率可表示为

其中,

对式(2)积分得到

观察式(3)可以发现,Rs并不出现在表达式中,但Rs对噪声的谱密度有带限作用。

3.3.2 积分相噪声

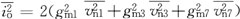

采样阶段获得的电荷在积分阶段传输至积分电容。开关引入多余的热噪声,引入的噪声被运放和开关的开启阻抗以及电容形成的时间常数所带限,如图5所示。

由小信号等效电路推导传输函数可得

其中:PA=gm/CS,Ps=-1/RsCS,gm为输入MOS管跨导,而且│ Ps│≥│PA│。在频域内积分推出

因为│Ps│》│ PA│,式(5)可简化为

,通过合理选择积分电容和采样电容的比值,可以优化噪声特性。综合考虑噪声、面积等综合因素,选择CS=CI=2pF。

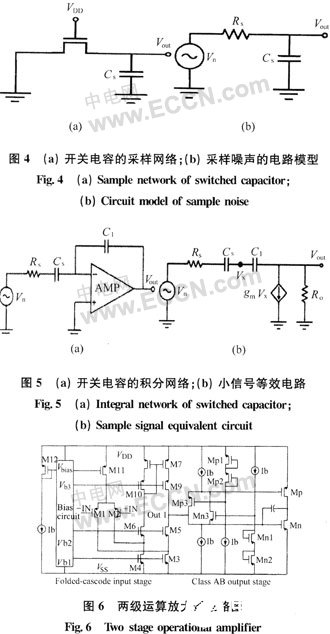

3.4 低噪声运算放大器的设计

积分器中,运算放大器采用folded cascode结构的两级运放,如图6所示。其中folded Cascode共源、共栅结构能够提高电路的增益,从而减小积分器的泄漏因子,而class AB类的输出级提高了非线性的转换速度。分析可知,运放第2级器件产生的噪声在等效到输入端时要除以第1级的增益,而通常情况下,第1级为高增益级,因此第2级器件对噪声贡献很小。在本文讨论中,将第2级器件产生的噪声忽略不计。具体分析为:将MOS管的器件噪声等效为与栅极串连的电压源,则该电路的第1级输出OUT1端的总噪声电流可以表示为

假设I3=I11=2I1=2I7,并考虑其对称性,有

其中,Gm表示有效跨导,

,凶为gmγd》1,因此级联顺件M5、M6、M9和M10产生的噪声可以忽略。输出噪声电流可表示为

,将其等效到运放输入端,得到等效输入噪声电压为

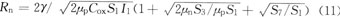

3.4.1 热噪声分析

MOS器件等效到栅极的热噪声谱密度可表示为

式中:对于工作在饱和区的长沟道MOS晶体管,可由推导得到γ=2/3,而对于亚微米MOS晶体管,γ可能需要更大的值来代替,在某种程度上γ还随漏源电压而改变[8];k=1.38×10-23J/K,是玻尔兹曼常数。将式(9)代入式(8)得到图6所示运放的等效输入热噪声的谱密度

其中

式中:S=W/L即器件宽长比;μn、μp分别为电子和空穴的迁移率。由上述推导可知,增大S1和I1即增大输入器件的宽长比和输入级的尾电流可减小热噪声。在设计中,还应考虑工艺参数与器件宽长比的关系等因素。

3.4.2 1/f噪声分析

MOS器件等效到栅极的1/f噪声谱密度可表示为

其中,K是与工艺有关的常数,数量级为10-25V2F。将式(12)代入式(8)可得到图6所示运放的等效输入1/f噪声的谱密度

将式(13)对Ll求导,

,得到

从上式可以看出,合理选择b、L7的尺寸,存在最优的Ll尺寸,使得1/f噪声最小。并注意到,增大b、L,的尺寸会减小1/f噪声。综合考虑工艺参数及电路面积等凶素,可进一步优化噪声特性。

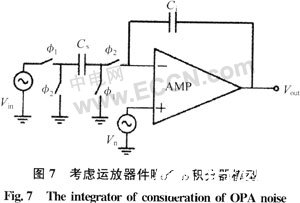

3.5 运放噪声在积分器输出端引入的噪声

运放器件噪声可以等效成在运放同相端的噪声源,如图7所示。

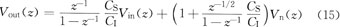

积分器的输出可以表示成输入信号和运放器件噪声的函数

可以看出,运放的器件噪声可直接传输至积分器输出端,并经过1/2时钟周期延时放大Cs/a倍后再叠加到输出端。

4 信噪比

积分器输出信噪比可以表示为

图26 其中Vsig为积分器输出信号

,Vnopa、Vnsc和Vnpixel分别为运放、开关电容电路和像素单元在积分器输出端的等效噪声。假设像素单元每次读m的信号是相等的,读出的噪声也是相等的,如果忽略运放和开关电容电路引入的噪声,则

即经n级TDI后输出信噪比为单级时的

倍,其中n为积分器的级数。对于CMOS电路,器件噪声是不可避免的,因此低噪声的电路设计是提高该电路信噪比的关键。

5 仿真结果

5.1 积分器仿真结果

在标准CMOS工艺下,通过合理的时序关系,TPI电路可由积分阵列来实现。图8为-32级TDl电路的仿真结果,积分阵列对32行的像素信号进行积分累加,实现了TDI功能。

5.2 运算放大器仿真结果

采用SMIC O.35μm CMOS工艺,本文设计的运放可以达到大约80 dH的直流增益,40 MHz的单位增益带宽,65°的相位裕度。图9为spectra仿真的运放频率特性区线。

5.3 积分器输出端噪声汇总

表1列出了单级积分器各部分产生的等效输出噪声,其中,VnTi、Vnfi为运算放大器等效输入的热噪声和1/f噪声。在带宽范围内对运放输入噪声谱密度进行积分,得到运放等效输入噪声,本设计运放带宽为40 MHz,积分得到运放等效输入噪声为36.1μV,乘以增益即得到运放器件噪声在积分器输出端的等效噪声,其余各部分噪声可以根据所选取的采样电容和积分电容值计算得到。

6 结 论

提出了在标准CMOS工艺下TDI电路的实现方法,并详细分析了电路的噪声,给出了器件级噪声的优化方法。采用SMIC 0.35μm工艺对电路进行了仿真验证,仿真结果表明,该电路能够实现TDI功能,并且具有低噪声特性。

责任编辑:gt

-

Bi-CMOS工艺解析2025-03-21 3206

-

基于OCDMA的无源光网络中信道噪声优化方法研究2023-10-09 419

-

基于500MHz带宽的TPS563209输出电压噪声优化和测试2022-11-01 579

-

CMOS技术及接收器拓扑结构2021-07-29 5676

-

DCDC变换器输出电压噪声优化和测试2021-07-02 7309

-

运算放大器噪声优化手册2021-05-31 2022

-

纯电动汽车电机啸叫噪声优化2021-01-22 1712

-

怎么采用标准CMOS工艺设计RF集成电路?2019-08-22 3002

-

运算放大器噪声优化手册PDF电子书免费下载2019-07-23 5306

-

运算放大器噪声优化手册详细中文电子教材免费下载2018-07-02 2005

-

采用CMOS工艺的射频设计研究2017-11-25 5787

-

低功耗低噪声CMOS放大器设计与优化2010-07-05 921

-

3GHz CMOS低噪声放大器优化设计2010-04-13 2031

-

Sic mesfet工艺技术研究与器件研究2009-10-06 6770

全部0条评论

快来发表一下你的评论吧 !