基于ADmC812微转换芯片和DSP芯片TMS320F206实现数据采集系统设计

处理器/DSP

描述

ADmC812是ADI公司的以8051(8052)内核为控制核心的新型微转换器。由于ADmC812内部集成了大量的外围设备。它本身就是一个完全可编程、自校准、高精度的数据采集系统,可以取代传统的MCU+A/D+ROM+RAM高成本、大体积产品,尤其是它的高精度和高速度A/D模块,特别适应于智能传感、瞬时获取、数据采集和各种通信系统。但是,对于需要采集数据量大、运算复杂、实时性又要求较高的场合,由于在结构和速度上的限制,往往是无法满足要求的。本文针对这种情况,提出了基于ADmC812和DSP的数据采集系统。在这个系统中,ADmC812作为主机,完成ADC、DAC、显示、键盘等功能,而DSP作从机,专注于复杂的数据运算,两者通过通用的SRAM实现数据的交换和通信。

ADmC812和TMS320F206简介

ADmC812微转换芯片

ADmC812是具有16位计数/定时和32条可编程I/O接口的8051/8052微控制器,内置一个8通道、5ms转换时间、精度自校正、12位逐次逼近的ADC;2个12位DAC,10.5KB的闪存EEPROM,256字节的SRAM。还包括一些重要功能模块,如看门狗定时器和电源监控器,ADC与数据存储器之间的DMA方式,存储保护功能,一个通用异步串行收发器(UART)、SPI和I2C总线接口。

ADmC812内丰富的外设,使它不需要外部总线扩展就可以组成一个完整数据采集系统,有很高的性价比。更值得注意的是在ADmC812内集成了8路12位高精度、自校准4ppm/℃的ADC电路。而且,当工作条件(如时钟频率、模拟输入范围、基准电压或电源电压)发生变化时,为了得到高精度的ADC结果,可以用软件对ADmC812内4个用于校正的特殊功能的寄存器设置,达到进一步校正ADC的目的。ADmC812通过设置ADCON1“3 三个特殊功能寄存器,可以使ADC工作于3种不同的模式,实现单次转换、连续转换和DMA模式的A/D转换,可以根据具体的需要选择,在DMA模式下,允许ADC在每次设置寄存器ADCCON1”3后连续采样,并将结果写入外部RAM中。这种自动捕获功能大大地方便了主从处理器之间的数据交换。

数字信号处理器TMS320F206

TMS320F206(以下简称F206)是TI公司生产的TMS320C2000系列DSP之一。是继C2X和C5X之后推出的低价格高性能的16位定点DSP,由于它采用了改进的哈佛结构,具有分离的程序总线和数据总线,采用四级流水线作业,其运行速度可达40MIPS,具有高速运行的特点。同时提供丰富的指令集,增强的模块化结构设计,使它通用化得以提高,应用领域不断拓宽,现已成为高档单片机的理想替代品。F206片内有32K的闪速存储器,用户通过F206自带的、符合IEEE标准1149.1的JTAG接口,可以对程序进行仿真与调试,并将程序代码烧录到片内,极大地方便了用户的系统设计与程序调试。

TMS320F206提供直接存储器访问(DMA)功能,通过使用HOLD操作允许对外部程序、数据以及I/O空间进行直接存储器访问。该过程是由、两个信号控制。外部设备可以把引脚驱动到低电平,从而请求对外部总线的控制。如果中断线被允许,那么将触发中断。F206在相应中断时,软件逻辑可以使处理器发出应答信号,表示它将放弃对外部总线的控制。根据,外部地址信号(A15“A0)、数据信号(D15”D0)以及存储器控制信号(、、、、、、)被置为高阻状态,实现DMA功能。

系统硬件设计

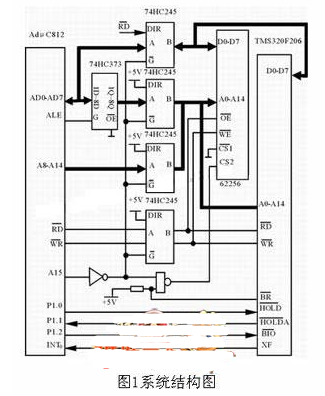

系统的硬件结构如图1所示,存贮器62256作为DSP的全局数据存储器,同时又是ADmC812的外部存储器,两控制器分别通过总线和数据存储器62256相连,实现存储器共享。为了保证两控制器能分别独立地工作。在ADmC812和62256之间插入了4片74HC245进行总线隔离。这样,在ADmC812的控制下,每一时刻只有一个控制器访问62256。图中62256作为ADmC812的外部存储器,A15为片选信号,地址范围为8000H“FFFFH;作为F206的全局数据存储器,用作片选线,使用高端32K字地址范围(8000H”FFFFH)。两片选信号经一与非门和62256的片选线CS2相连,实现片选信号的隔离。

ADmC812通过P1.0、P3.2(INT0)分别和DSP的、XF脚相连,由P1.0向DSP申请总线控制,在DSP响应ADmC812的请求后,DSP的CPU被挂起,并出让外部总线。ADmC812通过A15打开总线驱动器,并经与非门后选中62256,获得62256的控制权,实现对62256的读写操作。而F206也可以通过向ADmC812请求中断,ADmC812在响应中断INT0后,进行相关事务的处理。另一方面,ADmC812通过读引脚的电平,可以确认F206是否被挂起;而通过对脚的控制,实现F206程序的分支转移,增加系统的灵活性。

整个系统分为事务性模块和数据处理模块,ADmC812控制事务模块,进行数据的采集、LED显示、开关量的输入输出,模拟量的输出及串行通信等功能。F206控制数据处理模块,主要进行数据的处理,完成复杂的算法。另外,也可以根据数据处理结果直接处理一些重要的出口控制功能,以弥补ADmC812 I/O端口的不足,加快系统的反应速度。两个相对独立的功能模块通过62256进行数据交换。

系统软件设计

由于系统的两个模块在功能上相对独立,相应的软件也包括两个主要模块,ADmC812在程序加载完成后,就进入程序正常运行。系统初始化后,首先通过P1.0向F206请求DMA操作,且得到响应后,ADmC812获得62256控制权。这时,通过配置3个特殊功能寄存器ADCCON1“3,可以使ADmC812工作在不同的模式下。其中在DMA模式下,ADC可以连续转换,并把采样值捕获到外部RAM空间而不需要来自微处理器的任何干预,由中断位ADCCON2.7表示DMA转换结束。在A/D转换结束且采样点达到预定的数量后,ADmC812就通过ADC中断,放弃对62256的控制并通知DSP进行数据处理。而后ADmC812进入显示、键功能、I/O操作、串口通信等事务性的工作。

F206在接收到ADmC812的DMA请求后,进入到等待状态,并放弃对外部总线的控制权。62256通过ADmC812获得采样数据,当采样结束后,DSP从等待状态返回到正常运行状态并获得总线的控制权,进行数据处理,将运算结果放回62256。F206的DMA操作过程是:F206引脚/上获得一个有效的下降沿,当CPU转移到0002H地址单元,CPU从0002H地址单元提取中断矢量并进入中断服务程序,在对MODE=0进行成功的测试后,该中断服务程序就执行一个IDLE指令,使F206进入到等待状态。当检测到/脚上的一个上升沿后,CPU退出IDLE状态,并使外部总线返回其正常状态,执行数据处理程序。

软件使用C语言设计,分别在两个开发系统上进行程序设计和调试。利用ADI公司提供的软件开发工具,能够快速高效地完成ADmC812应用程序的设计,并通过ADmC812的通用串行口在线调试和代码下载。F206用闻亭公司提供的TDS-510开发工具进行软件设计。最后将ADmC812和F206进行联机调试,完成整个软件的开发。

结语

以上设计方案,适合于采集数据量大、算法复杂、有一定实时要求的应用领域。由于双CPU系统无需额外的附加双口RAM、FIFO及复杂的控制电路,降低了成本,简化了电路,也扩展了ADmC812的应用范围。

责任编辑:gt

-

求TMS320F206 DSP结构、原理及应用这本书2008-12-08 4421

-

TMS320F206的性能特点和外围电路典型设计2018-08-27 2292

-

DSP芯片TMS320F206异步串行口的应用2009-04-23 803

-

TMS320F206 使用中的一些问题2009-05-13 651

-

TMS320F206 DSP的以太网接口设计2009-09-09 607

-

基于TMS320F206的电网数据处理板设计2006-03-11 7133

-

DSP芯片外围电路典型设计(数字信号处理器芯片TMS320F2007-08-15 5137

-

TMS320F206复位方式的讨论2009-01-02 1902

-

TMS320F206与CPU卡通信协议的优化2009-11-26 1446

-

采用TMS320F206控制的同步调制解调器2009-12-08 1411

-

TMS320F206外围电路典型设计2009-12-24 1808

-

基于TMS320F206 DSP的图象采集卡设计2011-02-28 940

-

TMS320F206的仿真调试方案解析2017-10-27 2240

-

浅析TMS320F206 DSP的图像采集卡设计2021-05-05 2805

-

基于TMS320F206和RC56D芯片实现同步通信终端的设计2021-05-21 2997

全部0条评论

快来发表一下你的评论吧 !