带间隧穿结的若干种架构及其应用的详细讲解

今日头条

描述

隧穿结是半导体器件中的重要组成部分,根据载流子的输运原理可分为带内隧穿结(intraband tunnel junction)和带间隧穿结(interband tunnel junction)。

带内隧穿结在半导体电子器件和光电子器件中较为常见,如在欧姆接触架构中,电子在n型半导体材料与金属之间的输运方式即是通过带内隧穿完成;影响载流子带内隧穿效率的关键因素是隧穿结区的宽度,因此为了减小隧穿结区的宽度,需要采用重掺杂的半导体层。

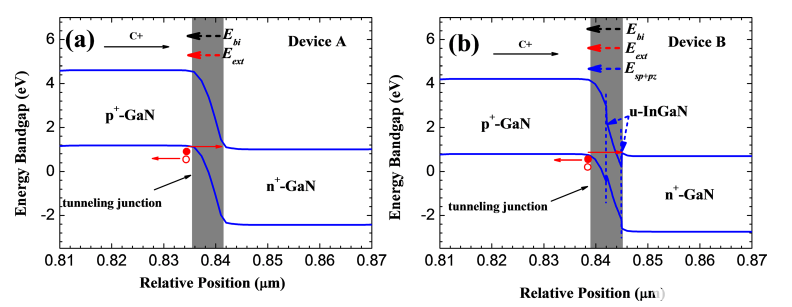

带间隧穿即电子从p型半导体层的价带,途径禁带,最终到达n-型半导体层的导带;于此同时,p型半导体层中伴随着空穴的产生,并在价带中进行输运;影响带间隧穿几率的关键因素包括两侧半导体层的掺杂浓度、隧穿结区中的电场强度、隧穿结区的禁带宽度、载流子的有效质量。目前较为常见的有同质隧穿结(如p+-GaN/n+-GaN,图1a);为了有效增强载流子的隧穿几率,研究人员提出了极化隧穿结(如p+-GaN/InGaN/n+-GaN,图1b),即利用InGaN层中极化电场的方向与内建电场方向相同的原理,实现隧穿结区中电场强度的增强,此外InGaN隧穿结的引入可有效减小隧穿结区的禁带宽度,实现载流子的高效率输运;此外介电调控隧穿结也是一种可有效提高载流子隧穿效率的重要器件架构(如p+-GaN/SiO2/ITO,图2),即利用SiO2材料较低的介电常数,实现隧穿结区中电场强度的增加。介电调控隧穿结亦可采用p+-GaN/AlGaN/ n+-GaN架构[Phys. Status A 214(6), 1600937(2017),Materials 10, 1221 (2017);注,AlGaN材料的介电常数小于GaN材料]。

图1 (a) 同质隧穿结 (b)极化隧穿结 [Appl. Phys. Lett. 102, 193508 (2013)]

图2 p+-GaN/SiO2/ITO介电调控隧穿结 [Appl. Phys. Lett. 108, 133502 (2016)]

带间隧穿结由于具有良好的载流子输运效率及电导调制效应,因此广泛应用于GaN基发光二极管中,以缓和电流拥挤效应,提高外量子效率。

fqj

全部0条评论

快来发表一下你的评论吧 !