ASIC设计的“四大神器”

描述

ASIC设计的“四大神器”,折叠(Fold ),展开(Expand),重定时(Retiming),资源共享(Resource Sharing) 。

折叠&展开

Fold & Expand,折叠和展开

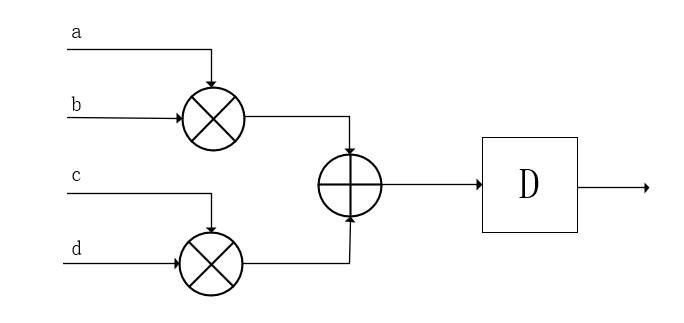

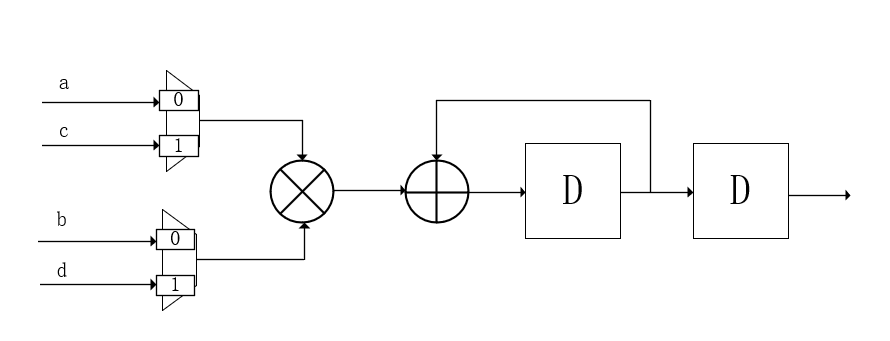

一拍得出结果,使用了两个乘法器,面积大,速度快。

两拍得出结果,使用了1个乘法器,面积小,速度慢。

这个过程就叫做折叠,展开可以看作是折叠的逆操作,在实际工程中,我们根据需求适当的使用这个两个技术,实现设计最优化。

提高速度和降低面积是两个矛盾的目标,所以在具体的设计中要折中(Trade-off),一个好的设计追求的极致是让乘法器等占用面积大的逻辑尽量不要空闲。高度复用。

重定时

笔试题中常有问,什么是Retiming技术?

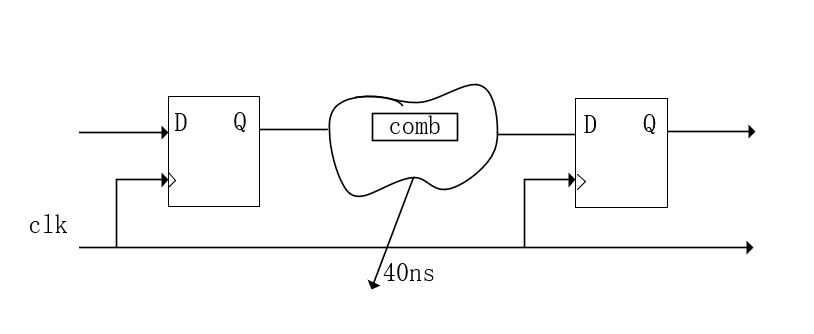

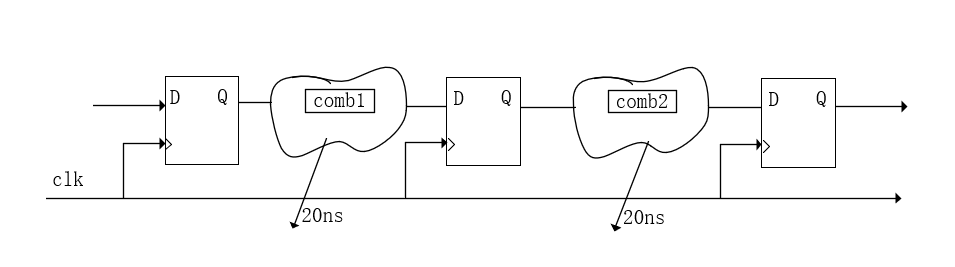

Retiming就是重新调整时序,例如电路中遇到复杂的组合逻辑,延迟过大,电路时序不满足,这个时候采用流水线技术,在组合逻辑中插入寄存器加流水线,进行操作,面积换速度思想。

我们知道任何的数字电路都可以等效成组合逻辑加D触发器打拍,两个D触发器之间的组合逻辑路径决定了,系统的工作频率,决定芯片的性能。所以为了提高芯片的工作频率,使用流水线技术在组合逻辑中插入寄存器。

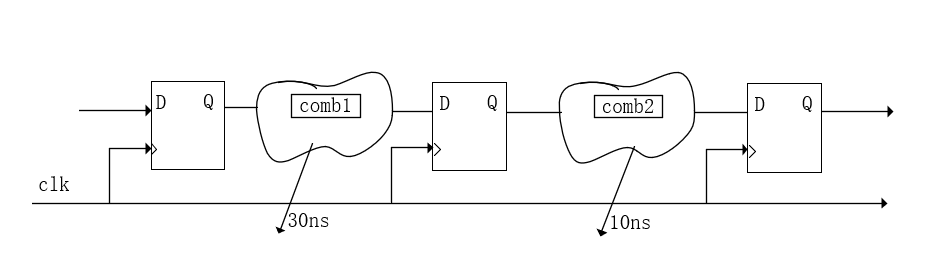

插入寄存器的位置需要慎重选择,不同的位置数据的打拍所消耗的寄存器的数量也不同,比方说你在位置a消耗25bit寄存器,位置b消耗20bit寄存器,能省则省。

前面插入寄存器的位置使得comb1的延迟为30ns,comb2的延迟为10ns,系统的最高工作频率是由最长路径决定的。也就是说你这个系统最高工作频率的周期,不小于30ns,前面是插入pipeline,这个时候我们不改变时序,采用重定时技术,使得各个组合逻辑之间的延迟相当。

资源共享

从设计的角度来说,最常见的就是计数器,能用一个计数器实现的,就别用俩,底层模块之间相同的逻辑尽量使用一块电路,减少重复的设计。

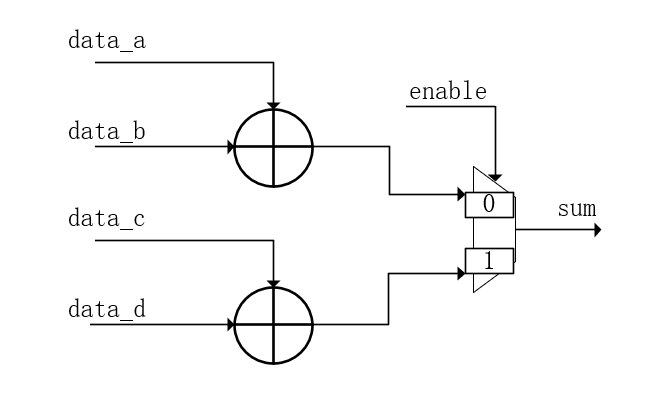

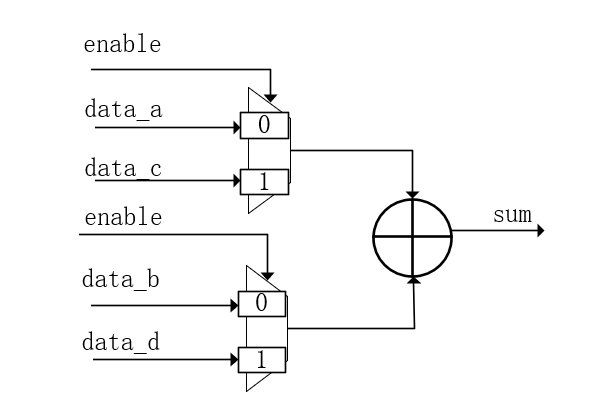

基本逻辑单元的共享举例,面积:加法器 > 比较器 > 选择器。俗称加比选。

乘法器本质上也是全加器。

所以就有先选后比,先选后加,先选后乘。

画个图意思一下。

最基本的层次共享是基于基本元器件的共享,综合工具能做较多的自动优化,在布局布线时还能进一步提高资源利用率,通常情况下是在同一模块内进行优化,但如果你的工具足够强大,则可以打破模块边界进行优化。像很多模块被打散揉在一起布线是可能的,从后端看也看不到模块边界。工具的布线优化人工都很难干预。

最后

以上是从基本电路设计的角度上和数据通路上进行归类,控制逻辑的话,简单来说一个字,状态机大法好。这个问题我们下次再聊。

责任编辑:lq

-

MES实施的四大疑惑2024-03-01 483

-

电机型号的四大组成部分2021-01-21 3369

-

图像无损放大神器PhotoZoom Pro v7.2应用程序免费下载2020-03-03 729

-

排查EMI问题的四大实用性技巧精选2019-09-16 1459

-

什么是PCB射频电路四大基础?2019-08-21 2539

-

机器视觉的四大基本功能2019-08-09 16436

-

四轴电机伺服控制ASIC芯片_刘亚静2017-01-07 963

-

视频图像处理的四大技术2016-07-23 8208

-

北斗在列 中国八大神器震惊全球2016-07-11 3321

-

Android的四大组件2015-10-30 589

-

对于cadence PCB/SCH/SI/PI四大功能的学习,求实例2014-11-22 4031

-

求大神给个抄板神器软件2014-08-29 3734

-

烤机哥WCG现场奇遇:四大“金刚”VS四大C girl2012-11-07 7827

-

EMC 四大设计技巧2012-08-17 5640

全部0条评论

快来发表一下你的评论吧 !