RGMII应用框图/接口信号/帧格式

接口/总线/驱动

描述

RGMII概述

RGMII接口,是ReducedGigabitMediaIndependentInterface的缩写。IEEE802.3Clause35在RS子层和PCS子层之间定义了一组接口GMII,该接口作为MAC和PHY数据交互接口。然而该接口在实际应用中面临最大的问题就是,如果MAC和PHY为分为两个不同芯片时,GMII管脚多(24PIN)导致封装成本增加,因此12PIN的RGMII就诞生了。

RGMII应用框图

图1RGMII应用框图

图1为RGMII应用框图,RGMII应用很简单就是作为MAC和PHY之间的数据通信接口。

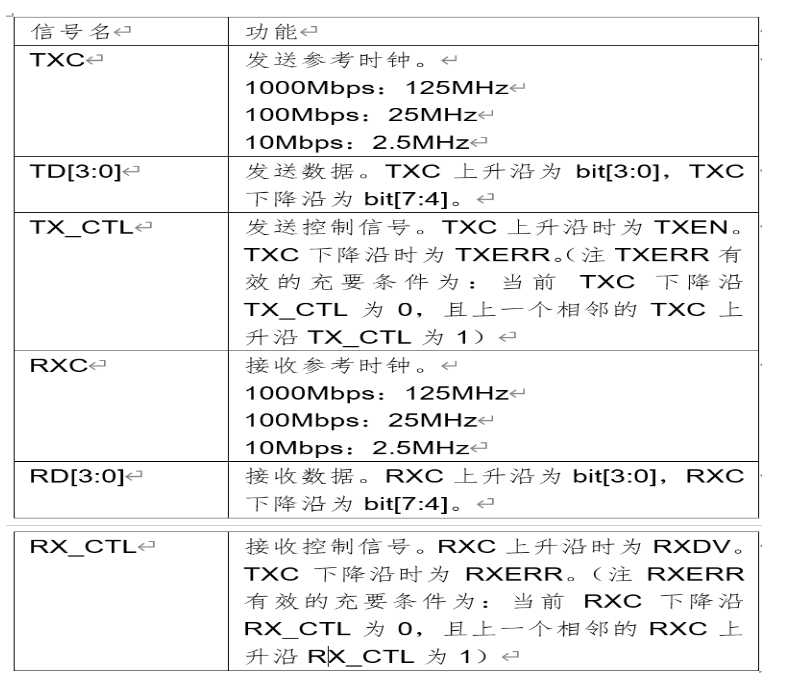

RGMII接口信号

表1RGMII接口信号

从RGMII接口信号就可以看出,所谓的ReducedGMII,就是将原来GMII125MHz单沿收发各8bit数据总线(TXD[7:0],RXD[7:0])),精简成125MHz双沿收发各4bit数据总线。同时将数据有效信号(TX_EN,RX_DV)和错误指示信号(TX_ER,RX_ER),精简为1bit控制信号线。

当RGMII工作在100M,10M模式时,仍工作在单沿模式。随路时钟(TXC/RXC)下降沿时数据保持不变。

RGMII接口帧格式

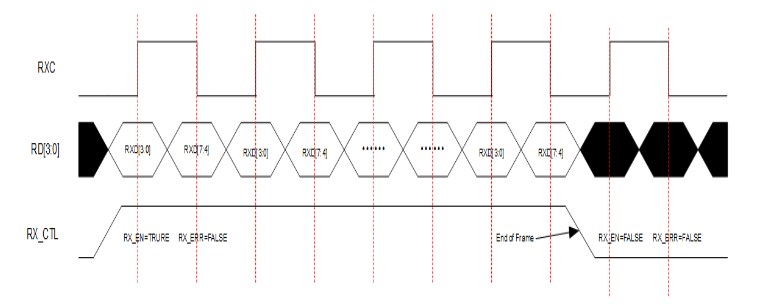

图2RGMII有效帧

图2为一个有效数据帧的传输。在有效帧传输过程中,RX_CTL在RXC双沿时均为高电平,代表RX_EN=1,RX_ERR=0。当帧传输完后在下一个RXC上升沿,RX_CTL拉低,之后RX_CTL一直为低。注意在帧间隙时,RXC下降沿RX_CTL为0,但是其相邻的RXC上升沿时RX_CTL也是0,因此不会被识别为RX_ERR。从图中可以看出,对于一个有效帧,RX_CTL总是在RXC上升沿时拉低。

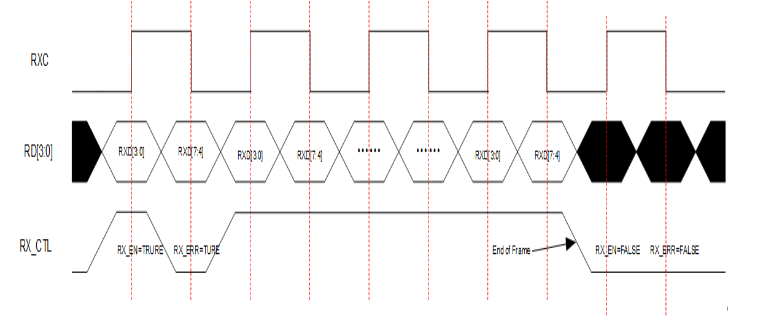

图3RGMII无效帧

图3为一个无效帧的传输。在传输第一字节数据时,RX_CTL在RXC上升沿为1在相邻的RXC下降沿为0,因此被识别为RX_ERR。该数据帧,整帧会被丢弃。RX_ERR可以出现在一帧数据传输过程中的任何位置,当RX_ERR被识别后,整帧会被丢弃。

RGMII接口从降低封装成本上来讲,做出了不可磨灭的贡献。然而由于其采用的双沿采样导致其实际工作频率已达到250MHz,这么高的速率对于一般的数字IO来说已经临近极限。RGMII有两个致命缺陷:1,由于双沿采样,每bit仅4ns有效时间,使得时序收敛时并不友好。因此RGMII接口实现时,通常TXC/RXC都会做90°、180°、270°、360°相位的粗调,方便采样时序调整。甚至还有芯片利用DLL在90度粗调基础上做更加精细的微调。2,不管有无有效数据,TXC/RXC都在持续以125MHz翻转,这种周期性翻转噪声,很容易引起噪声干扰,影响临近模拟IP的工作。还会带来辐射,导致EMC测试不过。为了解决RGMII这俩缺陷,基于SerDes接口的SGMII应运而生,SGMII接口不但解决了RGMII的缺陷,而且进一步的降低的管脚数。当前市面上的千兆PHY,RGMII/SGMII这两种接口均支持。

后记

写RGMII接口其实有点犹豫,因为从之前有一篇关于MDIO文章表现来看,以太网俨然已经是日落西山了,感兴趣的人很少。但是,作者对以太网有特殊感情,因为走出校门后读的一篇协议就是几千页的IEEE802.3,那些激情燃烧的日子至今回想起来依旧心潮澎湃,完全抑制不住想和同学们侃侃的心情。

RGMII实际上还有一个很冷门的功能就是RTBI,就是将TBI精简,因为应用较少本文就没有提及。

责任编辑人:CC

-

Centronics标准接口信号说明2009-03-10 3107

-

什么是板间接口信号?2021-04-09 1272

-

GMII和RGMII主要的接口2021-07-29 2256

-

无线接口信令协议2009-06-19 675

-

基于串行接口信号调制/解调的通信方案研究2009-09-05 856

-

SMC1602的封装尺寸及接口信号说明2008-11-01 5559

-

SWAP/空中接口信令是什么意思2010-04-09 1599

-

观察PCI Express HIP PIPE接口信号2018-06-22 4702

-

串口数据转CAN帧格式详解2019-02-02 16487

-

RGMII接口信号和帧格式_RGMII接口应用框图2020-09-30 33528

-

SMBus接口信号/应用框图/帧格式2020-12-11 15048

-

HDMI模块接口概念及接口信号定义介绍2022-04-12 1773

-

龙迅HDMI接口信号转换的应用案例2022-06-14 6005

-

浅谈CAN错误帧格式2022-09-29 1689

-

IC设计接口信号描述规范2022-12-26 865

全部0条评论

快来发表一下你的评论吧 !