硅基调频连续波雷达信号源技术综述

描述

1.

硅基调频连续波雷达信号源技术综述

调频连续波毫米波雷达能够具有全天候、探测距离远以及可同时测量目标距离和相对速度等特点,是无人驾驶汽车应用的最关键传感器之一。随着半导体技术的快速发展,硅基工艺在成本和集成度方面的巨大优势使硅基调频连续雷达吸引了来自学术界和工业界的大量研究。做为系统的核心组件,调频连续波雷达信号源技术的发展水平直接决定了调频连续波雷达所能实现的功能和性能。

清华大学微纳电子系池保勇、邓伟和贾海昆课题组对硅基调频连续波雷达信号源技术的研究现状和发展趋势进行了综述。在今后的发展趋势中,大扫频带宽、快速扫频和低频率误差调频连续波雷达信号源技术值得重点关注。

图. 清华大学课题组研发的2发3收77GHz CMOS毫米波雷达芯片和样机。

Silicon-based FMCW signal generators: A review

Wei Deng, Haikun Jia, Baoyong Chi

J. Semicond. 2020, 41(11): 111401

doi: 10.1088/1674-4926/41/11/111401

Full Text

2.

模拟与混合信号CMOS集成锁相环芯片设计技术综述

CMOS全集成锁相环(Phase-Locked Loop, PLL)是现代片上系统(System-on-Chip, SoC)集成电路芯片中必不可少的重要组成部分,其广泛用于SoC中数字电路系统时钟生成,高速有线通信数据调制时钟生成,以及无线通信载波信号生成。近年来,随着CMOS技术的不断发展,集成电路工艺节点的持续推进,全数字锁相环(All-Digital PLL, ADPLL)开始变得流行起来。其主要原因为数字电路在先进CMOS工艺条件下具有比模拟电路更灵活的可扩展性、更好的跨工艺设计可移植性和更小的面积等优势。

但是,相较于广泛应用的模拟与混合信号锁相环(Analog and Mixed-Signal PLL, AMS-PLL)而言,ADPLL由于存在量化噪声,且对电源噪声更加敏感,因此,ADPLL通常具有比AMS-PLL更高的输出信号抖动(jitter)。该问题限制了ADPLL在需要生产极低时钟抖动的应用场景中的应用,包括高性能处理器、5G无线通信、高速有线通信(比如56/112Gbps高速通信)以及下一代以太网通信等应用。因此,即使目前工艺节点尺寸已经到10nm以下,AMS-PLL依然是目前多数应用中的优先选择。

中国科学院半导体研究所张钊研究员等对AMS-PLL的基本电路结构和基本原理、主要研究问题、目前研究进展做了全面介绍,让有关科研及工程技术人员能够全面了解AMS-PLL的基础、电路设计的常见问题以及主流解决办法。同时,在全面介绍AMS-PLL的基础上,根据不同应用场景,对不同结构的AMS-PLL作了优缺点分析与对比,为有关芯片设计人员根据自身所需指标需求合理进行AMS-PLL结构选型提供参考与指导。

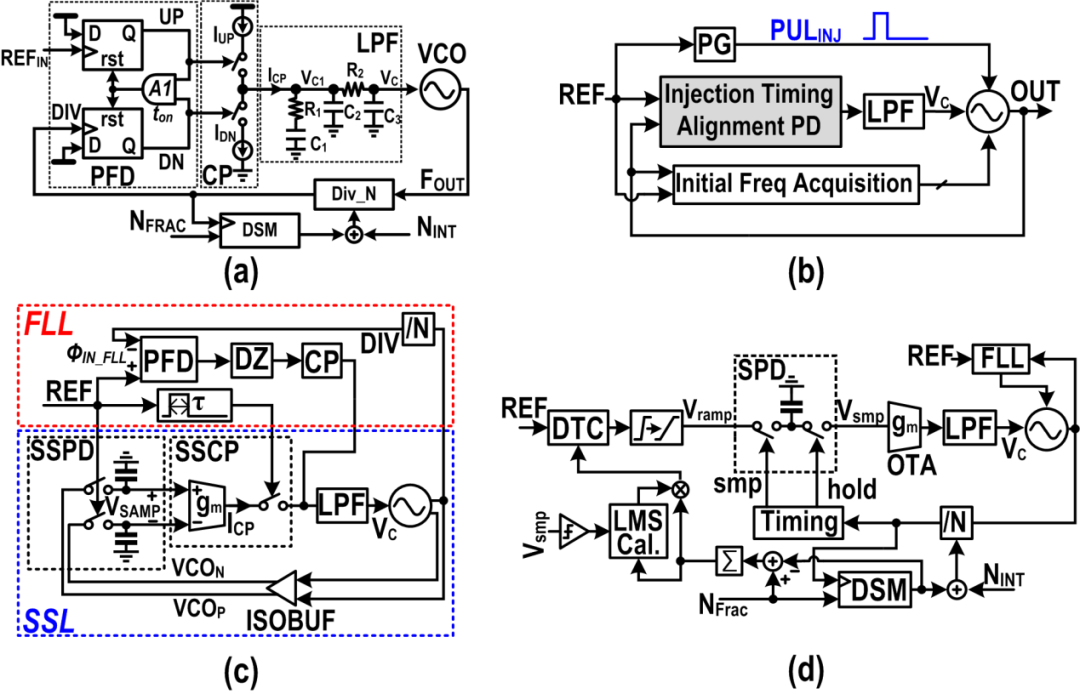

本综述论文主要包括以下内容:1、简要回顾AMS-PLL中最常用的电荷泵型锁相环(Charge-Pump based PLL, CPPLL)的基本原理;2、总结基本型CPPLL中存在的技术问题;3、系统回顾现有提升CPPLL性能的技术;4、简要介绍近年来开始成为研究热点的新型结构极低抖动AMS-PLL,包括注入锁定锁相环(Injection-Locked PLL, ILPLL)、亚采样锁相环(Sub-Sampling PLL, SSPLL)和采样锁相环(Sampling PLL, SPLL);5、分析与对比前面介绍的4种AMS-PLL结构,并据此讨论在不同应用背景下进行AMS-PLL结构选型的考虑,为有关芯片设计人员根据自身所需指标需求合理进行AMS-PLL结构选型提供参考与指导。

图1. 四种AMS-PLL电路结构框图:(a)CPPLL, (b) ILPLL, (c), SSPLL, (d)SPLL。

CMOS analog and mixed-signal phase-locked loops: An overview

Zhao Zhang

J. Semicond. 2020, 41(11): 111402

doi: 10.1088/1674-4926/41/11/111402

Full Text

3.

高能效高精度SAR ADC中的误差抑制技术

作为现实模拟世界与数字世界之间的接口,模数转换器(ADC)在众多电子系统中有着广泛而关键的应用。近年来蓬勃发展的物联网技术对低成本、高能效、高精度ADC提出了巨大的需求。逐次逼近型(SAR)ADC因为其结构简单、功耗低、对先进工艺兼容性好等优势,成为近年来该领域一个非常热门的架构。然而,传统SAR难以实现高精度,这主要受限于以下几个关键的误差来源:

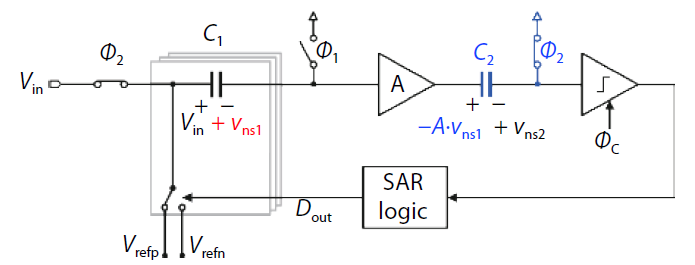

(1)采样噪声。长期以来,学术界公认的ADC采样噪声极限是kT/C,要想降低采样噪声,唯一的办法就是增加采样电容,然而大采样电容会给ADC的输入驱动电路和基准缓冲电路带来很大的功耗和设计复杂度。

(2)比较器噪声。比较器噪声是限制SAR ADC信噪比的最主要因素之一。降低6dB的比较器噪声,需要将比较器的功耗增大四倍,这将严重影响ADC整体的能效。

(3)数模转换器(DAC)失配。DAC会给ADC带来非线性失真的问题,限制了ADC的精度;而且,随着集成电路工艺的演进,器件尺寸越小越小,DAC失配的问题将更加严重。

近年来,清华大学电子系孙楠教授课题组提出了一系列新型ADC架构和电路技术,致力于降低SAR ADC中的这些关键误差因素,实现高能效高精度的SAR ADC。

针对采样噪声的问题,孙教授课题组提出了连续时间SAR架构、kT/C噪声抵消技术、噪声频谱密度和带宽解耦技术,打破了kT/C噪声极限,使得ADC的采样电容尺寸可以大幅降低而不会带来巨大的噪声代价,进而有效缓解了输入驱动电路和基准缓冲电路的负担。

图1. 可抵消kT/C噪声的SAR ADC。

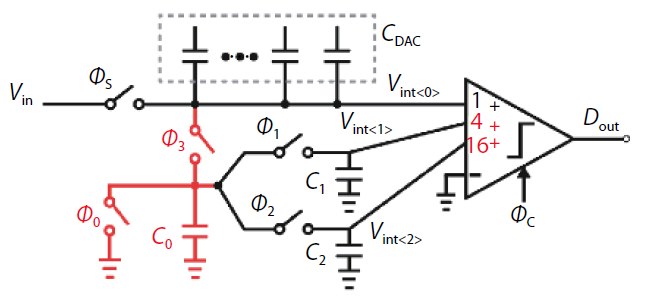

针对比较器噪声的问题,孙教授课题组提出了多种新颖的噪声整形SAR ADC技术,包括无源噪声整形、无源增益产生以及闭环动态放大器等。这些技术不依赖于传统的静态放大器就可以实现优异的噪声整形特性,具有低功耗、高PVT稳定性等特性。

图2. 无源噪声整形SAR ADC。

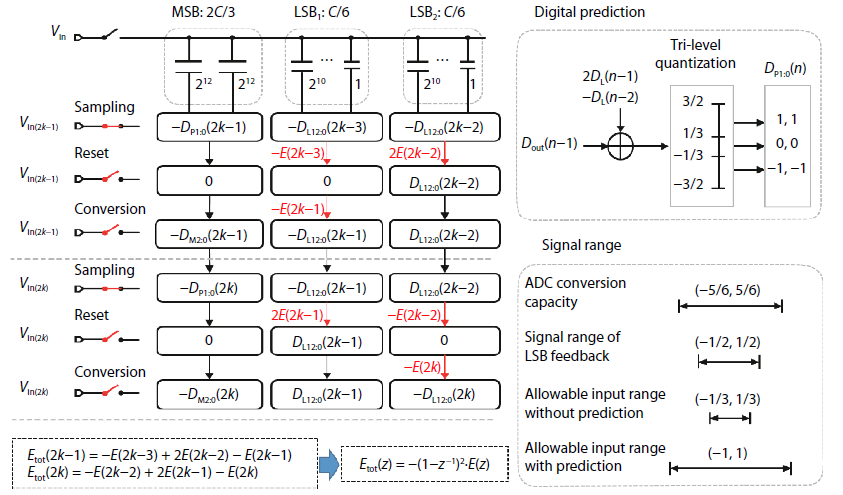

针对DAC失配的问题,孙教授课题组提出了高阶DAC失配误差整形技术,其硬件复杂度低、整形能力强,并可广泛应用于低通、高通、带通ADC中。同时,课题组还提出了用数字预测的方法来解决适配误差整形技术带来的动态范围损失的问题。

图3. 二阶DAC失配误差整形技术。

本文提出的一系列技术可有效提高SAR ADC的精度,同时保证其高能效的特性,在无线通信、物联网、生物医疗电子等领域有着广阔的应用前景。随着研究者们对该领域的持续深入研究,作者相信在将来的高精度ADC设计中,SAR将成为ΔΣ以外的一个极具吸引力的可选架构。

Error suppression techniques for energy-efficient high-resolution SAR ADCs

Jiaxin Liu, Xiyuan Tang, Linxiao Shen, Shaolan Li, Zhelu Li, Wenjuan Guo, Nan Sun

J. Semicond. 2020, 41(11): 111403

doi: 10.1088/1674-4926/41/11/111403

Full Text

4.

高速高精度电流舵型DAC综述

数模转换器用于将数字信号转换成模拟信号,作为连接数字世界和模拟世界的重要桥梁,其应用十分广泛,在有线及无线通信、数字信号处理、仪表测控、医疗及军工等领域发挥着重要作用。随着5G等现代通信技术的快速发展,系统对数据传输速率、带宽及精度均提出了更高的要求,所以对DAC采样速率与分辨率的高要求经常成为系统性能提升的瓶颈。

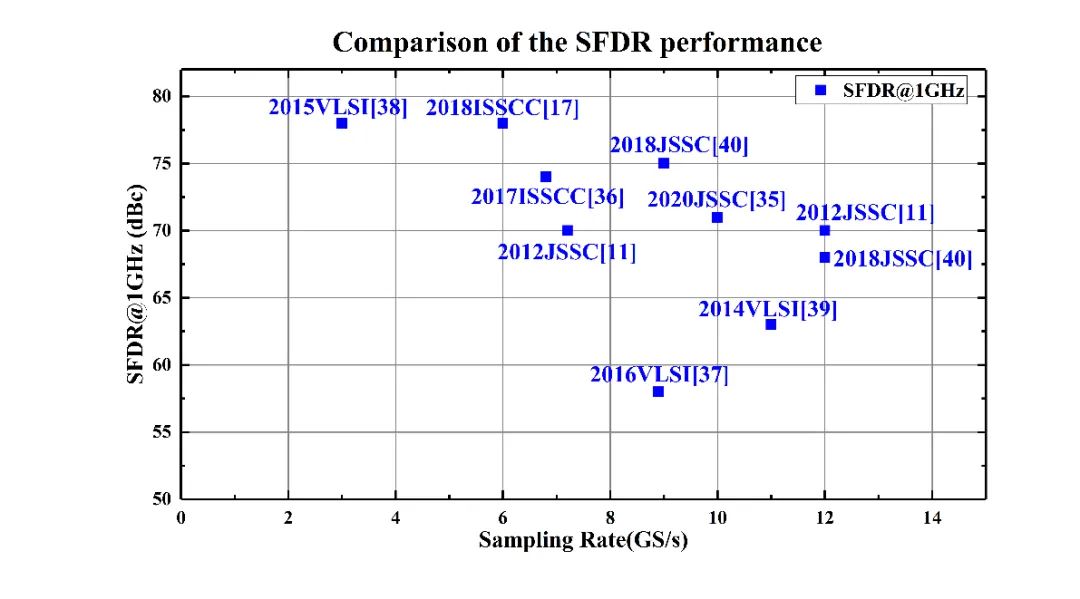

中国科学院微电子所周磊研究员等回顾了近年来国内外报道的关于高速高精度DAC的优秀成果,从电流舵型DAC的结构入手,介绍了各部分典型的电路实现与改良技术。对其中最具代表性/性能最佳的部分成果以图表的形式进行了更详细和深入的汇总与比较。

本文比较全面和详实地介绍了国内外关于高速高精度DAC的优秀成果与代表性技术,对读者了解电流舵型DAC的架构以及最新研究进展有一定帮助。

A survey of high-speed high-resolution current steering DACs

Xing Li, Lei Zhou

J. Semicond. 2020, 41(11): 111404

doi: 10.1088/1674-4926/41/11/111404

Full Text

5.

数字低压差稳压器技术的回顾和展望

在高能效的片上系统(SoC)中,资源的高度动态分配,对电源管理的粒度提出了要求。细粒度电源管理要求每个电源域都用单独的电压稳压器供电,这要求稳压器具有全集成、低压差、中等电源抑制等特点。

传统的模拟低压差稳压器(LDO)只能工作在较高输入电压和压差的情况下,难以使用于高能效系统中。相反的,数字LDO完美的克服了上述缺点。但是,数字LDO自身离散采样的特性,使得其响应速度较慢,电源抑制性能远逊模拟LDO。

澳门大学黄沫教授课题组长期进行数字LDO技术的研究,并发表了相关成果。本文中,作者首先对数字LDO研究背景进行了介绍。其次,在低电压工作和工艺伸缩性、功耗-速度折中、稳定性、电源抑制等方面,对模拟和数字LDO进行了比较。然后,作者对数字LDO中的量化器设计技术,PID控制技术,电源抑制比提升技术等方面进行了文献回顾和分析。最后,作者展望了数字LDO的未来发展方向。

随着细粒度电源管理需求的深化,数字LDO技术必将继续发展。其中,将数字控制算法、包括深度学习等技术应用其中,将是后续发展的潜在方向;另外,可全面综合的数字LDO也将是一个有趣的方向。

A comparative study of digital low dropout regulators

Mo Huang, Yan Lu, Rui P. Martins

J. Semicond. 2020, 41(11): 111405

doi: 10.1088/1674-4926/41/11/111405

Full Text

6.

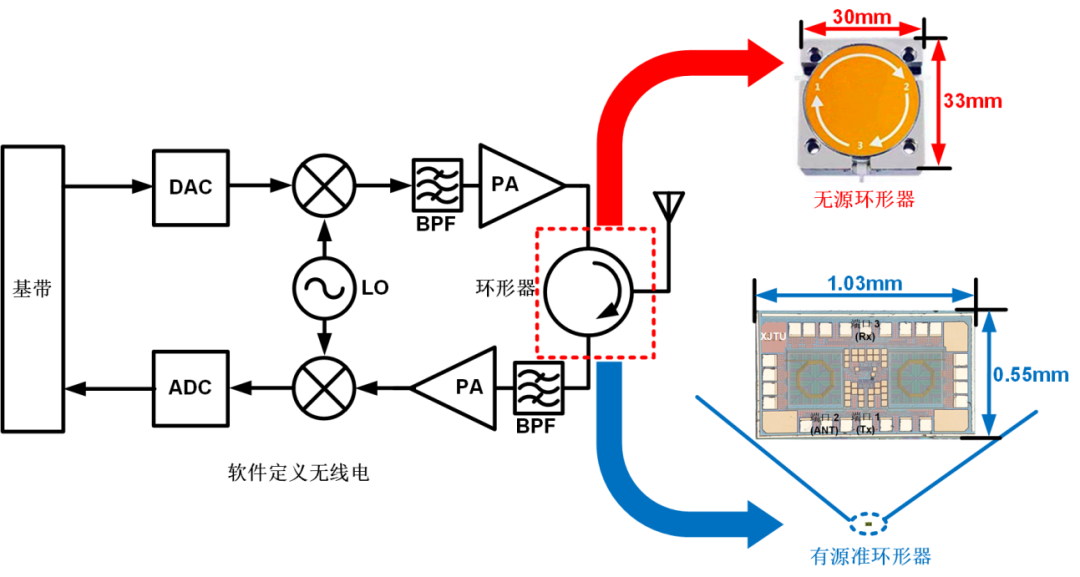

有源准环形器研究

移动电子产品对高速数据需求的日益增长促使通信电路与系统必须具有更宽的带宽和更高的数据传输速率。多频带无线通信系统由于能够以更高数据速率实现大数据传输,在现代通信系统中得到了广泛应用。环形器作为三端口非互易元件通常用在射频和微波系统中,实现发射信号与接收信号的隔离。环形器作为多频带无线通信系统的天线接口模块,应具有在多个频率下工作的能力,即具有在宽带下工作的能力,同时还需要提高发射端至接收端的高隔离度,以降低发射信号对接收信号的干扰。传统无源环形器通常基于铁氧体设计,铁氧体价格昂贵、体积大、难以集成,设计有源环形器可以提高通信系统的集成度,减小体积和价格。有源准环形器是有源环形器的一种,不存在接收端至发射端的传输路径。目前有源环形器的研究主要集中在有源准环形器上,已有的研究成果多为窄带有源准环形器,在宽带上实现发射端至接收端的高隔离度是有源准环形器的设计难点之一。

为了突破有源准环形器宽带和高隔离度不可兼得的瓶颈,西安交通大学耿莉教授课题组的唐炳俊博士提出并设计实现了反馈结构、双路结构和改进型双路结构有源准环形器。首先,在基本的有源环形器结构上增加负反馈通路,设计的负反馈有源准环形器的带宽达到了6 GHz,隔离度提高至27 dB。为了进一步提高隔离度、降低插损,课题组又提出了双路有源准环形器结构,增加了一条与已有抵消路径结构一致的抵消路径,该结构不仅拓宽了有源准环形器的宽带、提高了隔离度,同时也提升了工艺、电压及温度(PVT)鲁棒性。

芯片测试结果表明,隔离度相较于反馈结构提升了9 dB,而插入损耗降低了3 dB。随后,进一步将应用于低噪声放大器的噪声抵消技术运用到有源准环形器的设计中,降低了噪声,同时,加入了对称隔离缓冲器,有效降低了插入损耗。芯片测试结果表明,在隔离度保持不变的情况下,该有源准环形器的插入损耗比双路结构降低了6 dB,噪声系数降低了8 dB,工作带宽提升了1 GHz。三款有源准环形器分别在国际会议IEEE国际无线会议 (IWS)和国际期刊IEEE微波和无线元件通讯(MWCL)上发表,同时申请了国家发明专利。

有源环形器芯片的开发和应用将进一步减小通信系统的体积和成本。开发具有我国自主知识产权、面向5G和多频带无线通信应用的有源环形器芯片,对提高我国通信产品的竞争力具有重要的意义。

A survey of active quasi-circulators

Bingjun Tang, Li Geng

J. Semicond. 2020, 41(11): 111406

doi: 10.1088/1674-4926/41/11/111406

Full Text

7.

全自动模拟版图设计面临的挑战和机遇

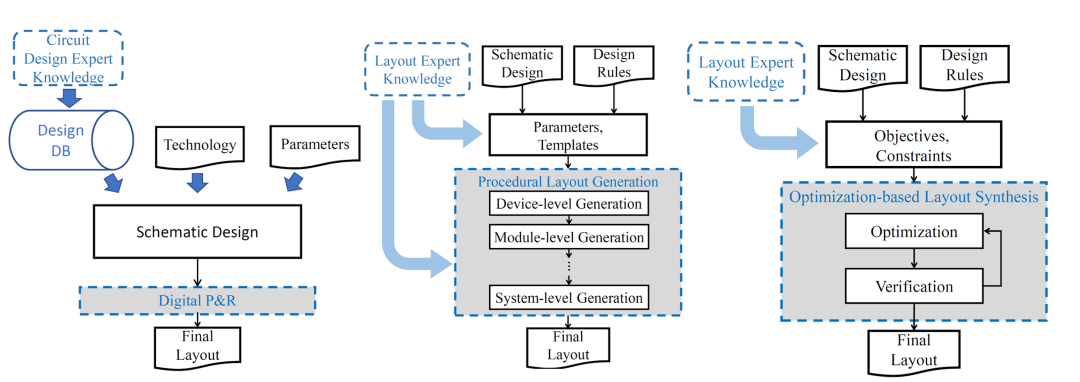

近年来,随着包含物联网、5G通信、智能计算、医疗电子等各种新兴应用的快速成长,市场对模拟集成电路的需求也在快速增加。在模拟集成电路设计中,后端版图一直是手动繁琐、耗时且易出错的工作。由于日趋复杂的设计规则,这个趋势在先进工艺中尤为明显,极大限制了芯片开发速度。尽管近年来,科研工作者在模拟集成电路版图自动化领域不断努力,但受限于模拟电路本身的复杂性,其与数字后端设计辅助相比仍有很大的差距。模拟电路涉及较多特定的电路类别,并往往需要对每种架构进行针对性优化。此外,模拟版图对信号耦合、整体布局和工艺变化较为敏感。电路性能可能会因版图实现中的微小变化而显著下降。此外,学术界目前尚缺能够有效模拟版图对性能的影响的方法。这些都对模拟版图自动化设计提出了重大挑战。

德州大学奥斯汀分校David Z. Pan课题组概述了当前的模拟/混合信号集成电路版图设计自动化方法,研究趋势以及模拟版图自动化的新愿景。文中首先回顾了三种主流的模拟集成电路布局布线方法和相关框架,包括可综合模拟电路设计、基于过程的布局布线技术、和基于优化的版图自动设计方法;然后介绍了学术界的一些最新进展,重点包括具有机器学习和统计功能的算法;最后在文中对未来EDA开发中的开放性问题和趋势提出了看法。

文章介绍到,随着开源EDA软件社区的成熟与机器学习算法的进步,最近几年来,模拟电路版图自动化领域取得了快速的进步。其中,以德州大学的MAGICAL、加州大学的BAG和明尼苏达大学的ALIGN为代表,开源模拟电路版图自动化已经成功证明了自身能够做到较为复杂的模拟、数字混合信号集成电路系统的版图设计。文章还着重展望了今后几年此领域的研究重点和挑战。文章指出,通过流片与测量验证,将会是将学术界研究转换为工业实际工具的重要一步。

Challenges and opportunities toward fully automated analog layout design

Hao Chen, Mingjie Liu, Xiyuan Tang, Keren Zhu, Nan Sun, David Z. Pan

J. Semicond. 2020, 41(11): 111407

doi: 10.1088/1674-4926/41/11/111407

Full Text

研究论文

1.

基于VCO比较器振荡数的自适应多旁路窗在SAR ADC中的应用

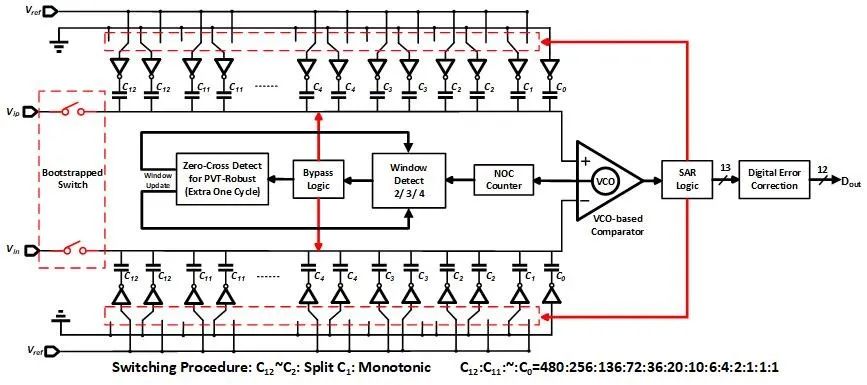

模数转换器(ADC)是模拟集成电路的核心问题之一,也是我国“卡脖子”的重大需求领域。近年来,逐次逼近(SAR)型ADC由于其高度数字化、功耗低、可并行等特点,在先进工艺下得到了长足的发展,并在高速领域逐步取得明显的优势。但受制于器件匹配,SAR ADC的高精度设计一直是个难题。而低功耗、低延迟、中高精度的ADC在传感器和自动控制系统中扮演着不可或缺的角色。

随着半导体工艺技术的发展,先进CMOS 工艺的特征尺寸与最大供电电压均在逐年下降。数字电路在功耗和工作速度方面相对较模拟电路在先进CMOS 工艺中获得了非常大的优势。对于模拟电路来说,特征尺寸的减小会导致CMOS 管的本征增益降低,低电压会带来噪声与电压裕度问题。

因此数字化模拟电路成为了一个热门的研究领域。因为比较器是电荷重分配SAR ADC 系统中唯一的模拟电路,所以将电压域的比较器替换成时间域的电路就能实现SAR ADC 的数字化。VCO比较器可以将电压差异转化为时间差异,如果输入信号电压差较大,则基于VCO 的比较器仅需要消耗少量的能量就能得出比较结果;如果输入信号电压差较小,则该比较器可以实现低噪声的性能。基于VCO 的比较器在得出比较结果的时候,其所需要消耗的振荡周期数与输入信号的电压范围有一定的关系。

电子科技大学低功耗集成电路与系统研究所李强教授团队首先利用随机过程理论对VCO比较器的噪声特性进行了理论分析,得到闭环VCO比较器行为的解析解,发现VCO比较器会因为噪声原因而在没有达到足够多的振荡次数之前停止振荡,会降低比较器的噪声性能。VCO比较器每一个不同的振荡次数均对应一个不同的电压范围,但此对应关系对PVT敏感,自适应旁路窗技术则是通过窗宽度检测技术得到在PVT变化的情况下的合适的旁路窗,使系统可以跳过正确的逐次逼近周期数。在较高速的高精度ADC中,参考电压的变化会导致错误的输出,为了避免使用过大面积的片上去耦电容来稳定参考源,论文提出一种用于旁路窗逻辑的分裂-重组冗余算法来纠正错误的结果。

本论文展示了一款12-bit 30-MS/s的SAR ADC,使用40nm CMOS工艺进行了仿真,在30MS/s 采样率、1.1V 供电电压以及tt corner 下的总功耗为0.38W,SFDR 达到85.35dB,ENOB 为11.12 位,品质因子为5.69 fJ/conversion-step。该项工作证明自适应旁路窗逻辑和用于旁路窗逻辑的分裂-重组冗余算法这两种技术都可以有效降低电路功耗和提高电路速度。未来还可以深度挖掘振荡信息,进一步提高ADC 的动态性能,比如利用一些统计学方法得到的ENOB 甚至可以超过ADC 本身的分辨率,但这就需要对VCO-based 比较器的原理比如相位噪声等进行更深刻的分析。

A 12-bit 30-MS/s VCO-based SAR ADC with NOC-assisted multiple adaptive bypass windows

Xiangxin Pan, Xiong Zhou, Sheng Chang, Zhaoming Ding, Qiang Li

J. Semicond. 2020, 41(11): 112401

doi: 10.1088/1674-4926/41/11/112401

Full Text

2.

适用于高频DC-DC转换器的快速瞬态响应技术

随着对高性能计算不断增长的需求,现代微处理器的电流消耗和电流变化速率都大大增加。由于负载变化而引起的大而快速的电流变化会导致大的电源电压下降,从而导致处理器严重的性能下降甚至停止工作。为了缓解该问题,向处理器供电的DC-DC转换器应具有快速的瞬态响应,以便减少输出电压降低的幅度和持续时间。

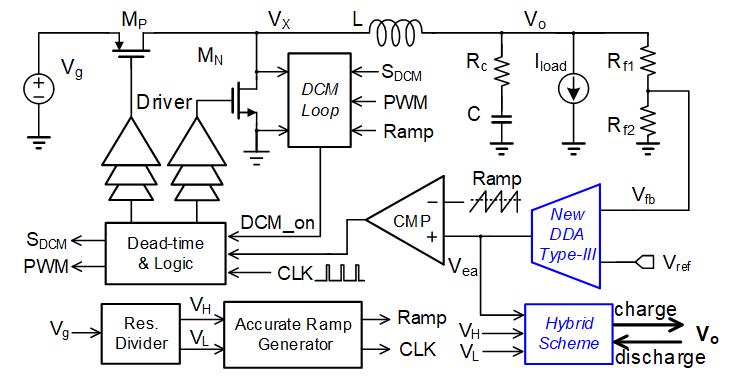

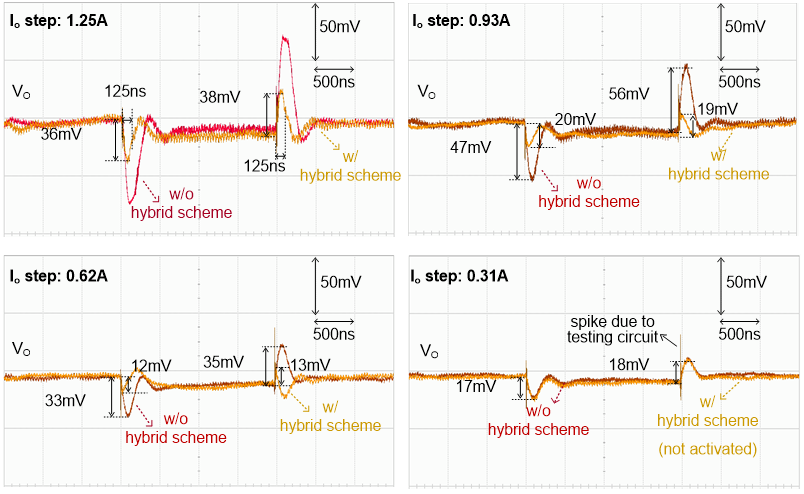

中国科学技术大学程林教授课题组提出了一种快速负载瞬态响应的补偿器,使得即使使用简单的电压型 PWM 控制模式,也可以将转换器的瞬态响应速度提高到接近理论上的最快速度,显著降低了电路的复杂度;同时在此补偿器基础上提出了一种数字线性调整器(digital linear regulator)辅助的混合控制模式(hybrid scheme),利用该技术设计了一款Buck DC-DC芯片,测试结果显示了其瞬态响应性能得到进一步的显著提高,取得了125ns/1.25A的瞬态跳变响应速度。

本文所提出的快速瞬态响应技术可以广泛应用于各种高频DC-DC转换器,能有效提高转换器的负载瞬态响应速度。

图1. 本文设计的Buck DC-DC转换器系统框图。

图2. 负载瞬态响应测试图。

Fast-transient techniques for high-frequency DC–DC converters

Lin Cheng, Kui Tang, Wang-Hung Ki, Feng Su

J. Semicond. 2020, 41(11): 112402

doi: 10.1088/1674-4926/41/11/112402

Full Text

责任编辑:xj

原文标题:半导体学报2020年第11期——模拟和数模混合集成电路专刊

文章出处:【微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

-

一文读懂信号源正弦波的特性2020-02-19 3873

-

基于STM32和FPGA的可控线性调频信号源的设计2010-07-08 906

-

横幅正弦波信号源电路图2009-07-01 701

-

基于DDS的雷达校准信号源设计2011-05-03 907

-

基于DDS理论的多模式多波形雷达信号源设计2012-02-10 3032

-

FPGA+DDS实现数控信号源的设计2012-03-23 1319

-

基于AD9959的高精度多通道雷达信号源设计2012-09-24 1823

-

基于FPGA的线性调频雷达各体制信号源的设计与实现2017-11-18 8123

-

连续波雷达介绍2017-12-12 6372

-

矢量信号源与射频信号源的区别?2018-01-08 35349

-

什么是调频连续波雷达物位计2020-07-11 5398

-

高频连续调频波雷达物位计的简介2022-04-17 2778

-

脉冲雷达和调频连续波雷达的区别2022-04-20 8924

-

傻傻分不清?射频模拟信号源和矢量信号源的区别2024-01-19 15070

-

Aigtek功率信号源的输出信号有哪些2024-02-26 1279

全部0条评论

快来发表一下你的评论吧 !