基于TMS320C6713和EP2C5 FPGA实现实时视频图像加密系统的设计

可编程逻辑

描述

引言

随着数字通信在网络中使用越来越频繁,视频的安全保密也显得越来越重要。在数字通信领域,许多在存储和传输中安全可靠的视频产品得到广泛应用,例如:付费电视、机密视频会议和医学图像系统等。从1970年开始就有许多优秀的密码技术已经确定并得到广泛的应用,如DES、IDEA和RSA等,同时也有许多密码技术由于加密速度不是很快,不能直接应用于视频加密中。因此,为了保护传输中的实时视频内容,研究一些专门的实时视频图像加密算法显得十分重要。针对上述问题,本文提出一种基于DSP+FPGA技术来实现实时视频图像加密。

1 多混沌图像加密

多混沌图像加密算法是通过多路选择器选择针对某一段数据采取哪种加密方式和密钥,然后对明文进行加密生成密文,多混沌图像加密算法框架如图1所示。多混沌图像加密算法涉及到流加密、分组加密及多路选择器。

1.1 流加密

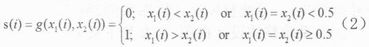

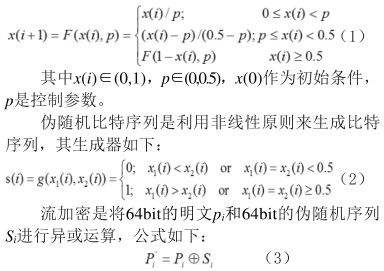

流加密的密钥是利用两个不同的一维逐段性混沌映射x1(i+1)=F1(x1(i),p1),x2(i+1)=F2(x2(i),p2)来生成x1(i+1)和x2(i+1)两个拟混沌轨道变量,然后利用非线性变换生成伪随机比特序列。采用的一维逐段性混沌映射如下:

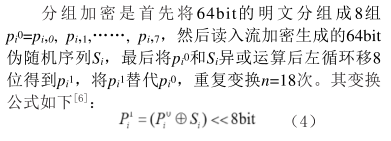

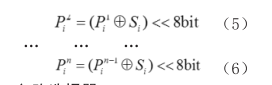

1.2 分组加密

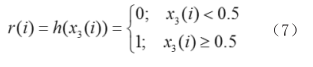

1.3 多路选择器

多路选择器是利用一个一维逐段性混沌映射x3(i+1)=F3(x3(i),p3)迭代多次来生成一个混沌轨道变量x3(i+1),然后依据式(7)来生成伪随机比特r,最后根据r来决定采用哪种加密算法,r=0时采用流加密,r=1时采用分组加密。

2 系统的总体设计

选用TI公司的TMS320C6713 DSP,该款DSP为高性能32位浮点型,其主频可达到300MHz,处理速度高达2400MIPS,片上共有264k×8位存储器,内置2个MCASP、2个MCBSP、2个I2C、1组GPIO、2个32位定时器、1个16位主机接口HPI和32位EMIF总线。选用Altera公司CycloneII系列的EP2C5 FPGA,该款FPGA拥有4608个逻辑单元,片上共计119808比特的RAM,2个高性能的锁相环,13个18×18的硬件乘法器以及具有142个用户可用的IO口。

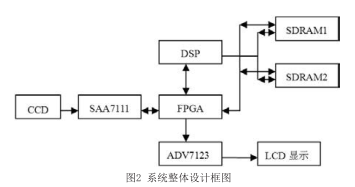

系统的CCD摄像头直接与视频解码芯片SAA7111相连,SAA7111将采集到的模拟图像数据转换成RGB565格式的图像数据,FPGA将接收到的图像数据存入到SDRAM1,然后发送一个信号给DSP;FPGA同时检测DSP对SDRAM2的数据加密完了的标志信号,这时FPGA读取SDRAM2中的数据,将数字图像数据通过ADV7123转换模拟图像数据,通过VGA接口显示。当DSP得到FPGA发送过来中断信号后读取SDRAM1的图像数据,然后根据多混沌加密算法对其进行加密,然后将加密后的数据存储到SDRAM1中,同时发送一个加密完成的标志信号给FPGA。系统整体设计框图如图2所示。

2.1 FPGA子系统设计

FPGA子系统需要实现的功能包括SAA7111的初始化、SDRAM接口控制以及VGA实时显示模块。

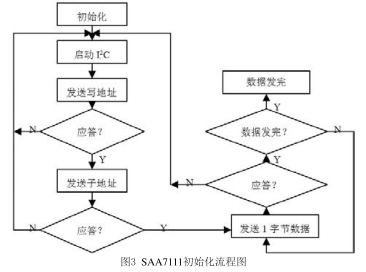

视频解码芯片SAA7111在系统的视频输入处理部分,需要对其进行合理的配置后,才能实现将模拟视频信号转换成相应格式的数字图像数据。SAA7111片内有32个控制寄存器,其中20个是可编程的,FPGA需通过I2C接口对其进行初始化,初始化流程图如图3所示。在对SAA7111进行配置时,首先时钟信号采用400kHz较为可靠,其次是I2C总线的开始信号、停止信号和应答信号,再次是设置好SAA7111相应寄存器的数据。

SDRAM的主要任务是完成图像数据的存储及加密数据输出。FPGA控制SDRAM程序主要由命令状态机模块和数据传输2个子模块组成。系统上电时需有100-200μs的等待时间,然后FPGA对其进行初始化。在进行完初始化之后,便可以对SDRAM进行读写控制。对SDRAM进行读写操作时,需先激活要读写的行和列,才可以对相应的行列进行数据读写,读写完成后FPGA将对SDRAM产生一个预充电的命令。

FPGA对SDRAM1和SDRAM2是采取乒乓缓存的方式控制。假如这时FPGA对SDRAM1进行存储图像数据,写完数据后对SDRAM2进行读数据;当FPGA对SDRAM1写完数据后,DSP读取SDRAM1里的数据,加密后将数据存入SDRAM1;下一次就是FPGA对SDRAM2进行写数据,如此反复交叉进行操作。

VGA显示子模块主要是产生VGA时序控制信号,VGA时序控制信号主要包括RGB数据信号、行同步信号及场同步信号。

2.2 DSP子系统设计

DSP子系统的主要工作是完成多混沌加密算法及对SDRAM数据的读写。多混沌图像加密算法在DSP中实现步骤如下:

(1)对式(1)中xj(0)和pj(j=1,2,3)的系统参数进行初始化设置;

(2)为确保系统进入混沌状态,首先将Fj(xj(i),(pj)迭代256次得到x1(i)和x2(i),然后将其代入l=[x1(i)+x2(i)+p1+p2)×1015]mod 256+1,得到F3(x3(i),p3)在第(3)步中需要迭代的次数,其中[y]表示对数据y进行下取整;

(3)继续迭代F1(x1(i),p1)和F2(x2(i),P2)并利用式(2)来生成密钥Si;同时将F3(x3(i),p3)迭代1次后,根据式(7)生成伪随机比特r,如果r=0,这时进入第(4)步流加密,否则进入第(5)步分组加密;

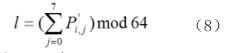

(4)将64bit的明文pi成8组(即pi=pi,0,pi,1,……,pi,7)与密钥Si进行异或操作,得到密文pi’=p’i,0,p’i,1,……,P’i,7,然后得到迭代次数1:

最后进入第(6)步;

(5)首先将明文分成8组得到pi=pi,0,pi,1,…,pi,7,然后将其按照式(4)、(5)、(6)进行变换,得到密文

,最后根据式(8)得到下一次F3(x3(i),p3)需迭代次数1,进入第(6)步;

(6)判断一帧的图像数据是否全部加密,如果没有完成则进入第(3)步,否则就进入第(1)步。

3 实验结果

为了验证系统的实时性和可靠性,对其进行了3种实验:FPGA单独工作实验、DSP单独工作实验和系统正常运行的实验。第一种实验是检验FPGA对实时视频图像数据在SDRAM中的读写是否正确,实验结果如图4所示,从图4可以看出FPGA对实时视频图像的传输是正确的。第二个实验是DSP直接读入一幅图片对其进行加密,加密完后FPGA将其读出并显示出来,实验结果如图5所示。同时通过Matlab软件编程对该幅图片进行相同的加密,实验结果如图6所示。图6证明了DSP对图像的加密是非常准确的。系统正常运行的实验结果如图7所示。

4 结束语

系统设计充分运用了TMS320C6713是浮点型处理器及其强大的运算能力等,同时结合了FPGA芯片对实时信号处理速度快等优点,使整个系统的设计具有很高的灵活性和更高的实时性。通过实验结果分析证明:采用DSP+FPGA的设计方案能满足对视频图像数据进行快速加密的需求,同时也说明了多混沌对视频传输具有较强的实时性和保密性等优点。

责任编辑:gt

-

从TMS320C6713迁移到TMS320C672x2024-10-16 396

-

TMS320C6713管脚分类2023-11-16 621

-

基于TMS320C6713的数字电源调节器2021-09-22 800

-

如何使用一个TMS320C6713的EMIF口是否可以和多个tms320c6416的HPI口通信?2020-05-27 1540

-

TMS320C6713 DSP芯片与pc机间的数据传输2019-06-05 2449

-

使用TMS320C6713进行数字电源调节器的设计方案和资料说明2019-03-05 1241

-

跪求TMS320C6713的资料2016-12-08 3789

-

TMS320C6713 DSK原理图2016-08-05 1447

-

卡尔曼滤波算法在TI TMS320C6713 DSP上的实现2016-06-03 1407

-

TMS320C6713程序怎么烧进Flash里面2015-03-16 2230

-

[共享] 卡尔曼滤波算法在TI TMS320C6713 DSP上的实现2011-08-20 10791

-

基于TMS320C6713B的数字视频消旋系统设计2010-11-26 639

-

基于TMS320C6713的G.723.1语音编解码的实时实2009-11-27 772

全部0条评论

快来发表一下你的评论吧 !