台积电第二代3nm工艺将于2023年量产 苹果首发

台积电第二代3nm工艺将于2023年量产 苹果首发

描述

电子发烧友网(文/黄山明)12月18日,据海外媒体报道,随着台积电5nm工艺在今年一季度大规模量产,并为苹果等企业进行代工后,下一步台积电将把目光转向更为先进的3nm工艺,而相关厂房已经在11月份就已建成。

其实早在8月份,台积电就已经公布了自己第一代3nm工艺的生产计划,将在2021年进入到风险试产、2022年开始量产。相较于5nm N5工艺,相同功耗下,台积电3nm N3性能将提升10-15%,而在相同性能下,N3功耗可降低25-30%。此外,N3的逻辑密度、SRAM密度、模拟密度分别为N5的1.7倍、1.2倍、1.1倍。

但就像N5有N5P技术一样,N3同样有第二代N3P工艺,据相关报道显示,台积电宣布他们的3nm Plus工艺将于2023年推出,但并未具体透露是在上半年还是下半年。

苹果将成为台积电N3P的首发客户,按照苹果A系列芯片发布时间预计,苹果将在2023年推出iPhone 15,其中采用N3P工艺制作的A17芯片,这也将成为N3P工艺的首款产品。

虽然台积电并没有透露N3P工艺相比N3到底有哪些区别,但从过去技术升级的常规路径来看,大概率会有更高的晶体管密度、更低的功耗以及更高的运行频率。

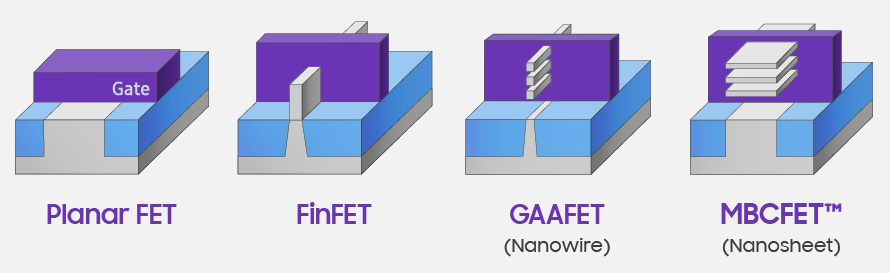

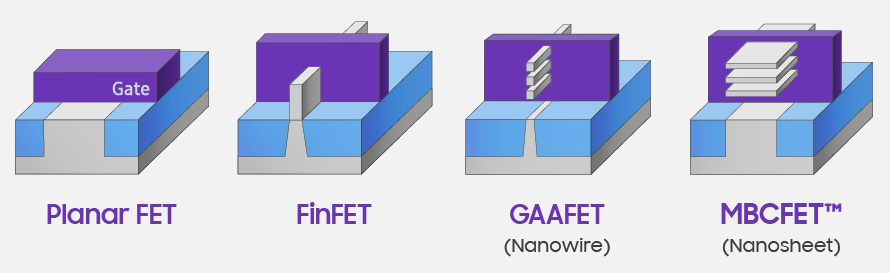

此前有业内人士推测,台积电的第二代3nm工艺将放弃 FinFET 晶体管工艺,转向GAA环绕栅晶体管。因为在芯片制程越小的情况下,可能发生两种情况,一种是短沟道效应,第二个则是量子隧穿,GAA技术能够有效的抑制短沟道效应。

而在2nm工艺上,台积电在前段时间已经传来消息,由于工艺上取得重大突破导致,研发进度提前,业界也看好台积电在2023年下半年风险试产良率能够达到90%,2024年正式量产。而台积电的2nm工艺将采用全新的多桥通道场效电晶体(MBCFET)架构。

MBCFET技术能够解决由于制程萎缩所产生的电流控制漏电的物理极限问题,不过从原理上来看,MBCFET同样可以看做是一种GAA,不过由于设计不同,GAA采用的是纳米线,而MBCFET采用的是板片状结构多路桥接鳍片。此外,GAA还有六角形截面纳米线与纳米环的设计形式。

虽然GAA能够带来性能的提升和功耗的降低,但其成本显然也不容小觑。据市场研究机构IBS的数据显示,28nm工艺的成本在0.629亿美元左右,而5nm工艺价格暴涨至4.76亿美元,因此如果台积电N3P采用GAA技术,其成本将超过5亿美元。

从台积电工艺量产的时间间隔来看,3nm Plus工艺将在2023年正式推出,与7nm到5nm工艺的时间间隔基本一致。而7nm与5nm工艺的第二代技术都是在第一代工艺量产的后一年推出。据台积电总裁魏哲家此前的公开演讲显示,台积电制程每前进一个世代,客户的产品速度效能提升30%- 40%,功耗可以降低20%-30%。

打开APP阅读更多精彩内容

其实早在8月份,台积电就已经公布了自己第一代3nm工艺的生产计划,将在2021年进入到风险试产、2022年开始量产。相较于5nm N5工艺,相同功耗下,台积电3nm N3性能将提升10-15%,而在相同性能下,N3功耗可降低25-30%。此外,N3的逻辑密度、SRAM密度、模拟密度分别为N5的1.7倍、1.2倍、1.1倍。

但就像N5有N5P技术一样,N3同样有第二代N3P工艺,据相关报道显示,台积电宣布他们的3nm Plus工艺将于2023年推出,但并未具体透露是在上半年还是下半年。

苹果将成为台积电N3P的首发客户,按照苹果A系列芯片发布时间预计,苹果将在2023年推出iPhone 15,其中采用N3P工艺制作的A17芯片,这也将成为N3P工艺的首款产品。

虽然台积电并没有透露N3P工艺相比N3到底有哪些区别,但从过去技术升级的常规路径来看,大概率会有更高的晶体管密度、更低的功耗以及更高的运行频率。

此前有业内人士推测,台积电的第二代3nm工艺将放弃 FinFET 晶体管工艺,转向GAA环绕栅晶体管。因为在芯片制程越小的情况下,可能发生两种情况,一种是短沟道效应,第二个则是量子隧穿,GAA技术能够有效的抑制短沟道效应。

而在2nm工艺上,台积电在前段时间已经传来消息,由于工艺上取得重大突破导致,研发进度提前,业界也看好台积电在2023年下半年风险试产良率能够达到90%,2024年正式量产。而台积电的2nm工艺将采用全新的多桥通道场效电晶体(MBCFET)架构。

MBCFET技术能够解决由于制程萎缩所产生的电流控制漏电的物理极限问题,不过从原理上来看,MBCFET同样可以看做是一种GAA,不过由于设计不同,GAA采用的是纳米线,而MBCFET采用的是板片状结构多路桥接鳍片。此外,GAA还有六角形截面纳米线与纳米环的设计形式。

虽然GAA能够带来性能的提升和功耗的降低,但其成本显然也不容小觑。据市场研究机构IBS的数据显示,28nm工艺的成本在0.629亿美元左右,而5nm工艺价格暴涨至4.76亿美元,因此如果台积电N3P采用GAA技术,其成本将超过5亿美元。

从台积电工艺量产的时间间隔来看,3nm Plus工艺将在2023年正式推出,与7nm到5nm工艺的时间间隔基本一致。而7nm与5nm工艺的第二代技术都是在第一代工艺量产的后一年推出。据台积电总裁魏哲家此前的公开演讲显示,台积电制程每前进一个世代,客户的产品速度效能提升30%- 40%,功耗可以降低20%-30%。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

台积电第二代3nm工艺产能颇受客户欢迎,预计今年月产量达10万片2024-01-05 1337

-

台积电3nm工艺预计2024年产量达80%2024-01-03 1706

-

台积电3nm制程工艺正式量产 已举行量产及产能扩张仪式2022-12-30 1652

-

第二代有人用了!台积电最新3nm工艺首颗芯片流片2022-10-27 2094

-

iPhone15系列或采用3nm苹果A17芯片 台积电代工2022-10-10 3510

-

台积电2nm和3nm制程工艺2022-07-04 4051

-

台积电宣布3nm Plus工艺将在2023年推出,消息称苹果将是3nm Plus工艺的首个客户2020-12-18 2493

-

消息称台积电第二代3nm工艺计划2023年推出2020-12-02 2203

-

台积电将于2022下半年开始量产3nm芯片 首发苹果A162020-11-25 2035

-

台积电第二代 5nm 工艺性能提升水平有望高于预期2020-11-06 2229

-

苹果A13芯片将采用台积电第二代7nm工艺 并率先采用EUV光刻技术2019-05-13 5348

全部0条评论

快来发表一下你的评论吧 !