利用不恢复余数阵列除法和VHDL实现雷达数据接收/显示系统的设计

描述

根据系统要求,脉冲雷达高度表通过RS-422串行输出高度数据,要求数据接收模块实时接收,并显示雷达高度数据。接收模块接收到的高度数据采用二进制(BIN)码表示,而数码管等显示设备需要BCD码(即二进制编码的十进制码),所以二者之间的转换非常必要。

BCD码与BIN码的相互转换比较传统的方法是采用DAA调节指令来实现,需要逐位调节,比较费时。文献提出利用模除,每次移动半字节,使转换效率大为提高,但也仅是软件算法,无法满足数制转换高效率和实时性的要求。文献提出了采用分段查找EPROM的硬件方法,满足点阵记录实时性的要求,但是该算法需要大容量的EPROM。文献利用BCD码与BIN码的逻辑对应关系直接转换,需要经过多级复杂的变换逻辑,面积和时延较差。

为此,本文采用Verilog HDL硬件描述语言将雷达高度数据接收/显示的核心功能集成到XILINX公司的FPGA(XCS200)中,使得整个设计更加紧凑、小巧、稳定和可靠。利用不恢复余数阵列除法快速准确地实现BIN码到BCD码的转换,仅需要少量的移位和加/减法操作,简化实现数制转换中的求余和整除运算。该单元阵列结构规整,不仅节省了面积,适于超大规模集成电路实现需要,而且易向更高进制扩展,具有很高的转换速度。

1 串行高度数据接收/显示模块简介

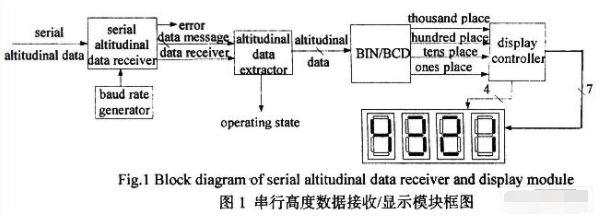

数字式自动距离跟踪脉冲雷达高度表串行输出的高度数据,首先通过串行高度数据接收模块将串行数据转换为并行报文数据,再通过报文滤波/数据提取模块,提取出高度数据,并根据输出高度数据的时间间隔标识雷达的工作状态,然后BIN码表示的高度数据通过以不恢复余数阵列除法为基础的BIN/BCD码转换模块,转换为适合七段码显示的90BCD码后送到扫描七段码显示控制器,以驱动四位七段共阳极动态显示数码管,如图1所示。

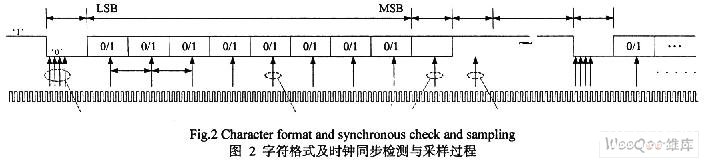

串行高度数据收发模块采用三线制连接方式,通信方式为异步传输,波特率:9 600,数据位:8位,停止位:1位,奇校验,其字符格式及时钟同步检测与采样过程如图2所示。

2 基于不恢复余数阵列除法的二进制到BCD码的转换

提出的BIN码到BCD码的转换算法采用数据除以位权的方式得到千、百、十、个位BCD码,因此除法器的设计是关键。在数字计算中各种除法都可以用下列递归公式来描述:

(1)

这里_j=0,1,…,n-1为递归下标;D为除数;qj+1为小数点右边第j+1位商;r为基数,r×R(j)为部分被除数;R(j+1)为部分余数;R(0)为被除数(初始部分余数);R(n)为最后余数。

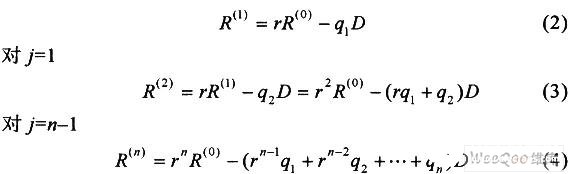

除法过程可通过重复应用递归式1来得到证明。

对j=0

上述迭代推导过程说明了除法过程是由一系列加法、减法或移位所组成,对于基数r=2,q…∈{0,1}。

当部分被除数rR(j)不够除数D减时,商qj+1为0,同时补充被除数的下一位,组成更大的部分被除数;如果够减,则该位商为1,在部分被除数rR(j)中减去除数D,然后补充被除数的下一位,直至被除数的每一位都使用到为止。

在除法进行过程中,可使用专门的数据比较器来比较部分被除数rR(j)是否比除数D大(nonperforming算法),或直接用部分被除数减去除数。方式1浪费了专门的数据比较电路,运算延迟加大,降低了运算速度。方式2,当完成了减法操作后,如果不够减,把除数加回到产生的差,以恢复原来余数(恢复余数法);或把产生的差留给下一次运算时再处理(不恢复余数法)。

2.1 不恢复余数阵列除法器

为简化起见,下文用A表示被除数,D表示除数,R表示余数。在恢复余数法中,如果余数R为负数,即不够减,则需要加上除数D,恢复成原来的余数,即R+D。然后,余数R和被除数A联合左移1位。此时余数为2(R+D)+ai,其中ai为A中的一位,被移入R中。随后,进入下一步运算。即从余数中减去除数D:(2(R+D)+ai)-D,有

(2(R+D)+ai)-D=2R+ai+D (5)

因此,当在某一步中,余数R为负,无需再加上除数D来恢复成原来的余数,只需在下一步中把恢复余数法中的减去除数D改成加上除数D,这种算法称为不恢复余数法。恢复余数除法需要2个步骤来确定1个商位,而不恢复余数法没有这个缺点。

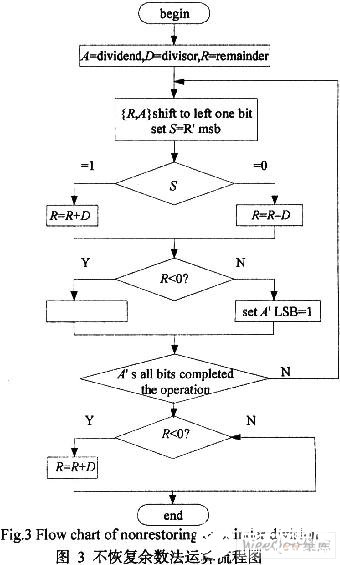

表1以45 10/1010=101101 2/10102作为一个数值计算的例子,详细展示了图3所示的不恢复余数法算法流程图。首先将余数尺和被除数A联合左移一位,如果余数R的符号位S为0,将执行减法操作,否则应该加上除数D,如果余数大于零,则当前商位为‘1’,否则为‘0’,循环这个过程直到被除数A的所有位都完成运算。最后得商:0001002,余数:000101 2。

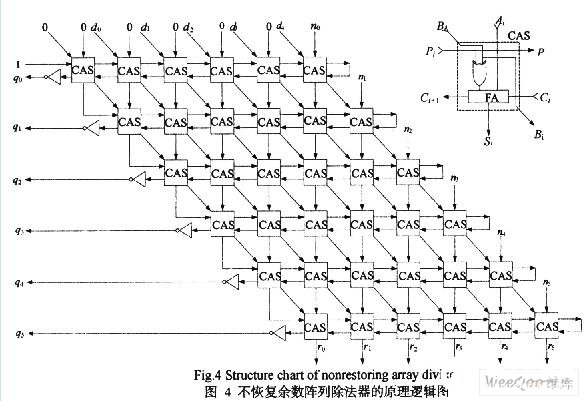

在除法中所需要的部分余数的左移可以用余数保持固定,而用除数沿对角线右移的等效操作来代替。如图4所示,不恢复余数阵列除法器可以用一个由可控加法/减法(CAS)单元所组成的叠接阵列来实现。不恢复阵列每一行所执行的操作究竟是加法还是减法,取决于前一行输出的符号与被除数的符号是否一致(最上面一行所执行的初始操作通常是减法,因此最上面一行的控制线P固定置成‘1’。当出现不够减时,部分余数相对于被除数来说要改变符号。这时应该产生一个商位‘0’,除数首先沿对角线右移,然后加到下一行的部分余数上。当部分余数不改变它的符号时,即产生商位‘1’,下一行的操作应该是减法。

3 仿真验证

图5的仿真结果说明了数据接收/显示模块的功能特点。串行高度数据接收模块将串行数据转换为并行报文数据,从并行报文中提取出高度数据(1100h=4352,068eh=1678),不恢复余数叠接阵列除法器将多位二进制编码的高度数据转换为千、百、十、个位BCD码送到扫描七段码显示控制器。scanout信号选择四位七段共阳极数码管的某一位,leddata分别对应7个阴极引脚,对应分段字符串“abcdefg”,实现一位一位轮流点亮显示。由于视觉的记忆性,看到的是稳定的多位十进制高度数据显示。从仿真结果图中可见其与前述设计思想完全吻合。

4 结论

采用不恢复余数阵列除法设计的BIN码到BCD码转换器,仅需少量的移位、加/减法等操作,该算法逻辑简单,结构规整,速度高,非常适合实时性要求较高的场合,而且非常容易向其它进制转换扩展。以异步串行数据接收、阵列除法及动态显示等技术为基础的脉冲雷达高度表串行高度数据接收/显示模块作为一个工程的子模块,在某雷达高度表的设计中已经得到应用。

责任编辑:gt

-

e203除法器算法改进(二)2025-10-22 177

-

数字IC设计中的除法器的工作原理2025-10-21 186

-

单片机使用硬件除法器求出的商和余数数据怎么处理?2023-10-30 604

-

数字阵列雷达系统的基本框架和工作原理2023-09-05 8459

-

如何利用FPGA和VHDL语言实现PCM码的解调?2021-05-07 1383

-

FPGA怎么实现除法操作?2020-12-24 2530

-

数字阵列雷达:零中频接收机的优缺点2020-08-29 4836

-

汽车雷达:阵列天线设计步骤2020-06-15 4247

-

基于SOPC技术实现雷达数据采集和图像大屏幕显示2018-02-21 6110

-

总线细胞阵列中空闲细胞冗余数量研究2017-01-07 496

-

CRC除法的余数为什么跟普通除法产生的余数不一样2015-01-26 3824

-

51单片机proteus仿真用单片机端口演示数据的除法运算结果2012-03-22 4638

-

实现模2除法的线路2009-10-13 7214

全部0条评论

快来发表一下你的评论吧 !