时钟分频及定时变换电路

信号处理电子电路图

347人已加入

描述

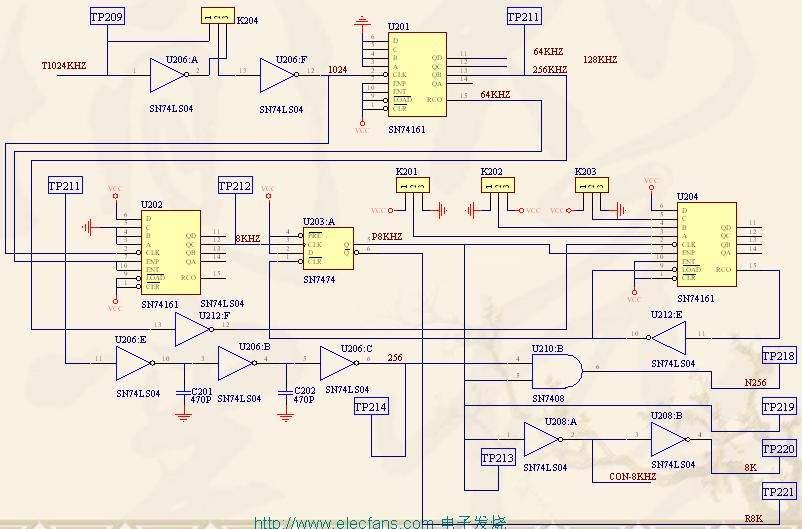

时钟分频及定时变换电路

发送1024KHz方波信号进入倒相器U206:A(74LS04)的输入端(第1引脚)后,再经过U206:F(74LS04)输出到第一级分频电路U201(74LS161)中,逐级分频,得到256KHz的时钟信号,在测试点TP211处可测出波形。将U201(74LS161)的第15引脚输出的64KHz窄脉冲信号送至第二级分频电路U202(74LS161)的第7与10引脚,作选通信号。由于只有在64KHz的窄脉冲期间,分频电路才能有输出。因此U202的输出经过逐次分频后,通过U203:A(74LS74)与U204:A(74LS161)U212(74LS04),在U203:A的Q端输出8KHz作为发送分帧同步信号,端输出反相8KHz作为接收分帧同步信号。

U208:A(74LS08)的输出8KHz信号作为软定时信号的计数信号,输送至CPU U215(89C51)的定时器T0、T1。

U210:B(74LS04)是8KHz窄脉冲对256KHz方波进行选通输出。U206:B、C、E(74LS04)作延时用,对256KHz方波信号进行延时,克服逻辑竞争现象。

图7-7分频电路及定时变换电路波形图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 变换电路

-

时钟分频电路实现精讲2013-04-18 0

-

时钟分频电路精讲2013-07-11 0

-

CC3200 定时器捕获时钟 预分频2018-06-23 0

-

定时器时钟分频因子和预分频系数区别2021-08-09 0

-

时序脉冲产生和分频电路2008-12-01 5962

-

供数字时钟使用的+5000分频器电路2009-01-13 1426

-

时钟555定时器电路2009-01-17 2680

-

可编程定时、分频两用电路图2009-05-30 533

-

基于FPGA的高频时钟的分频和分配设计2009-06-20 1360

-

时钟分频因子是什么有什么作用?2017-11-15 19908

-

二分频电路及代码2019-10-08 24159

-

verilog的时钟分频与时钟使能2023-01-05 1774

-

利用FPGA的高频时钟扇出电路的分频和分配设计2023-08-16 341

-

FPGA学习-分频器设计2023-11-03 2024

-

如何实现分频时钟的切换2023-12-14 843

全部0条评论

快来发表一下你的评论吧 !