关于risc-v启动部分的思考

描述

关于risc-v启动部分思考

1.本文说明

1.1 risc-v的诞生的时代背景

1.2 发展现状

2.risc-v 的芯片boot过程

2.1 risc-v的启动模式

2.2 risc-v的启动顺序

3.什么是SBI?

4.什么是opensbi

5.openSBI call接口的实现

6.总结

1.本文说明

risc-v的架构有着非常鲜明的特点,如果看过arm,aarch64,mips等架构的一些架构手册的基础知识,再看risc-v的芯片的架构设计,就会觉得非常有意思,可以找到一些影子,但是又比这些架构设计简洁的多。当我看完aarch64的芯片手册,再看risc-v的boot时,设计思想竟然可以做一些对比,同样去看risc-v和mips的寄存器,也可看到高度的一致性。

对于x86的架构我未曾深入了解,但是在risc-v上应该也可以找到一些设计元素。总体说来,risc-v的架构设计集合了各种架构的设计的优点。我突然觉得这种堆叠即模块的设计思想,在当前iot物联网发展的如火如荼的时代又要被赋予最新的使命了。我十分看好risc-v的设计思想,也期待着与软件界的Linux一样,发展的繁荣昌盛。

1.1 risc-v的诞生的时代背景

risc-v至诞生之日起,就赋予了良好的设计模式,吸收了大量的arm、x86、以及mips中良好的设计基因,将过时指令设计的与架构设计中的坑都避免了。这几十年的芯片的发展过程中,不少的芯片架构都曾因为设计问题消失在历史长河中,有着曾经一度辉煌的sparc,还有当时被十分看好的mips。如今市场上最热门的就属x86和arm了,一个主打移动市场,一个主打pc市场,两个在芯片架构的市场上发展的如火如荼。

然而,两个巨头都牢牢的把控着核心技术的门槛,用arm必须去买ip授权,以及x86的交叉授权模式等等。这些都让很多崇尚开源的人看不下去了。那么设计芯片的指令集很难么?设计芯片的指令并非难事,这要很多人使用才行,因为芯片上需要搭载操作系统,需要去运行各种各样的软件,比如浏览器、数据库、办公系统、专业软件等等。这些适配工作投入的精力和难度恐怕是需要集结各国最强的研发实力才能发展完善的。而risc-v就有这个魔力,竟然可以一呼百应,大概是大家受到arm与因特尔的压迫已经很久了,大家都想自己造芯片玩玩。

arm与x86架构由于时间累计的问题,都积累了大量的指令集,x86当时诞生时不过80条指令,而今也有着上千条指令集了,各种复杂的指令集,多媒体指令集等等,使得写底层软件的人苦不堪言。乔布斯有句名言:至繁归于至简。历史遗留的问题既然不能克服和解决,那就干脆抽取精华,设计出一个优秀的架构出来,于是risc-v在这种时代背景下开始了其新的使命。

1.2 发展现状

新事物的崛起,必会引来众多人的围观,技术的风所到之处,均是机会的影子。

而今risc-v已经成为众多大学生积极学习的课程,各大公司也已经启动了预研和探索的脚步。

RISC-V虽仍是星星之火,却已现出燎原之态。

2.risc-v 的芯片boot过程

2.1 risc-v的启动模式

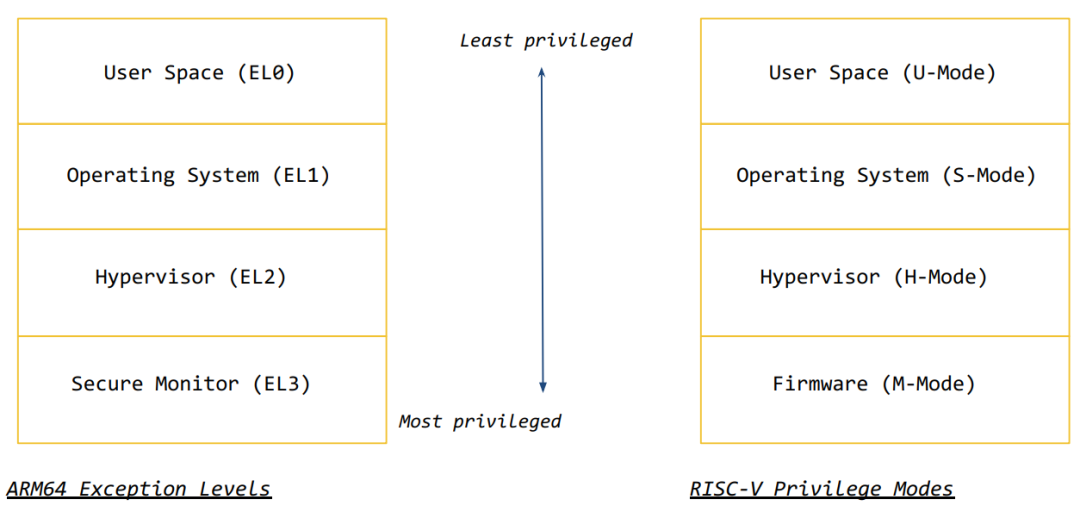

在理解risc-v的boot流程之前,首先需要知道的是risc-v设计的三种模式:

M-mode(Machine Mode)

S-mode(Supervisor Mode)

U-mode(User Mode)

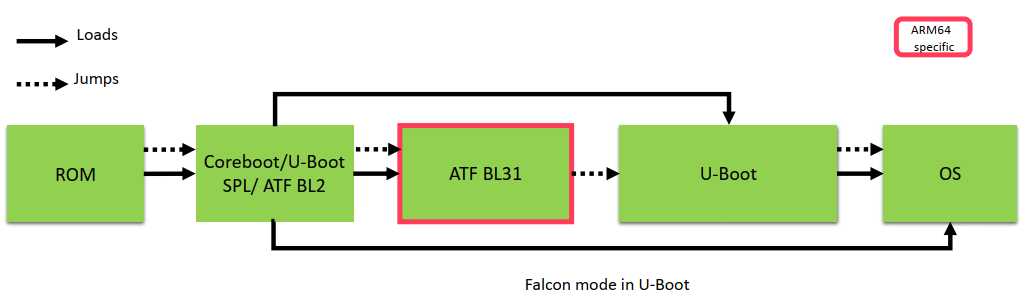

对于arm64来说,系统上电后启动会处于EL3 secure world ,所以对于arm64来说,一般都会使用ARM Trusted firmware (TF-A) 在normal world EL2 与 secure EL3 进行切换。

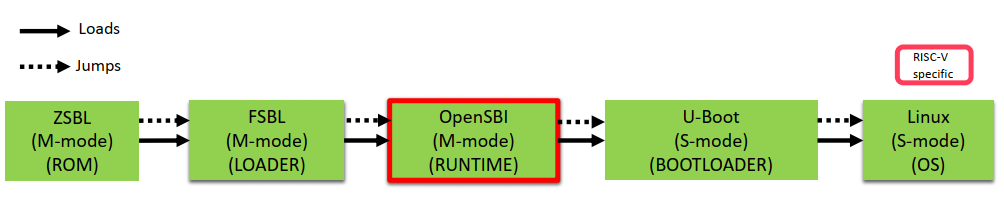

而对于risc-v来说,系统上电启动后会在M-Mode,而risc-v目前是没有Hypervisor这一层的概念的,所以目前采用的是opensbi。

2.2 risc-v的启动顺序

对于标准的risc-v启动顺序,可查看FU540的芯片手册,其中有如下的顺序描述:

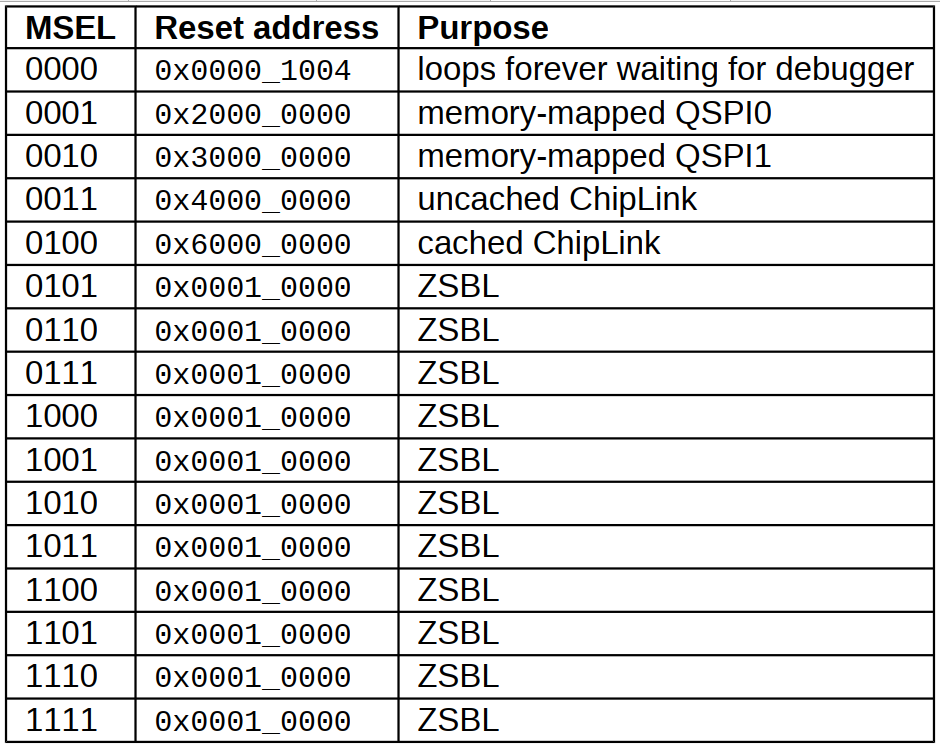

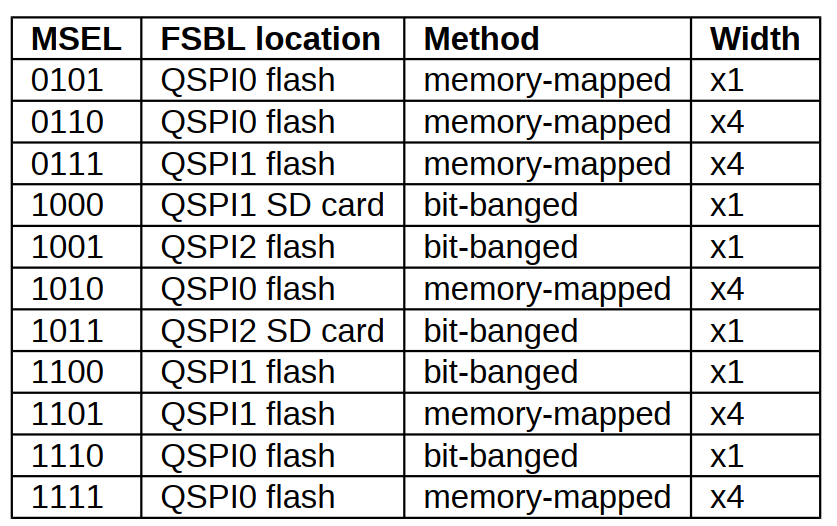

MSEL(Mode Select):启动模式,一般为选择拨码开关等方式进行选择。

ZSBL (Zeroth Stage Boot Loader):片上ROM程序。

FSBL(First Stage Boot Loader ):启动PLLs和初始化DDR内存。

BBL(Berkeley Boot Loader ):提供加载,并且管理着二进制接口(SBI)。

下面详细分析一下FU540的启动流程。

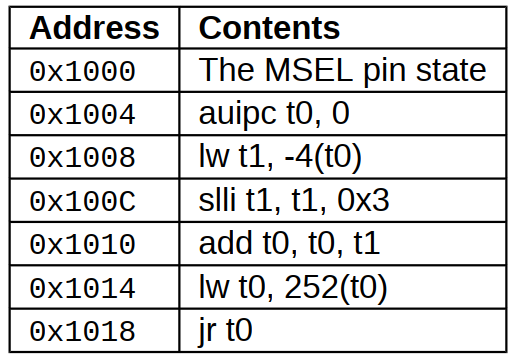

复位向量表

当芯片上电后,当芯片有33.3MHz外部晶振时钟时,所有的核会跳转到地址0x1004地址处去执行程序。

程序会根据MSEL选择,选择如下的跳转地址:

Zeroth Stage Boot Loader (ZSBL)

零级引导程序加载会从GUID分区中下载更加复杂的FSBI,一般都是QSPI的flash或者sd卡中下载FSBI,然后将该程序放到地址0x08000000处,至于从哪个介质查找FSBI,可以看到如下的选项:

The First Stage Boot Loader (FSBL)

该执行的地址位于L2 LIM,也就是地址0x08000000。该程序的目的是DDR初始化后,将系统在DDR中执行起来。

切换频率到1GHz。

配置ddr pll,外设时钟和控制器等等。

拷贝设备树和SBI固件到DDR中。

跳转到0x80000000开始执行程序。

Berkeley Boot Loader (BBL)

Berkeley引导加载程序(BBL)从位于0x8000_0000的DDR执行。它负责提供管理器二进制接口(SBI)以及模拟所需的任何RISC-V不是由芯片本身实现的指令。该接口可以为Linux等其他的os提供调用接口。

3.什么是SBI?

SBI的全称是RISC-V Supervisor Binary Interface 。它提供了risc-v标准的S-mode OS与SupervisorExecution Environment (SEE) 接口。

一般来说,操作系统都不会直接管理硬件资源,会通过SBI去调用到M-mode。

4.什么是opensbi

简单的说,opensbi就是一个开源的RISC-V虚拟化二进制接口的通用的规范。

使用的是BSD-2的开源协议,也就是任何人都可以随意修改和使用,也提供了通用的规范化的接口实现。

这里就需要理解一下为什么需要规范化了。

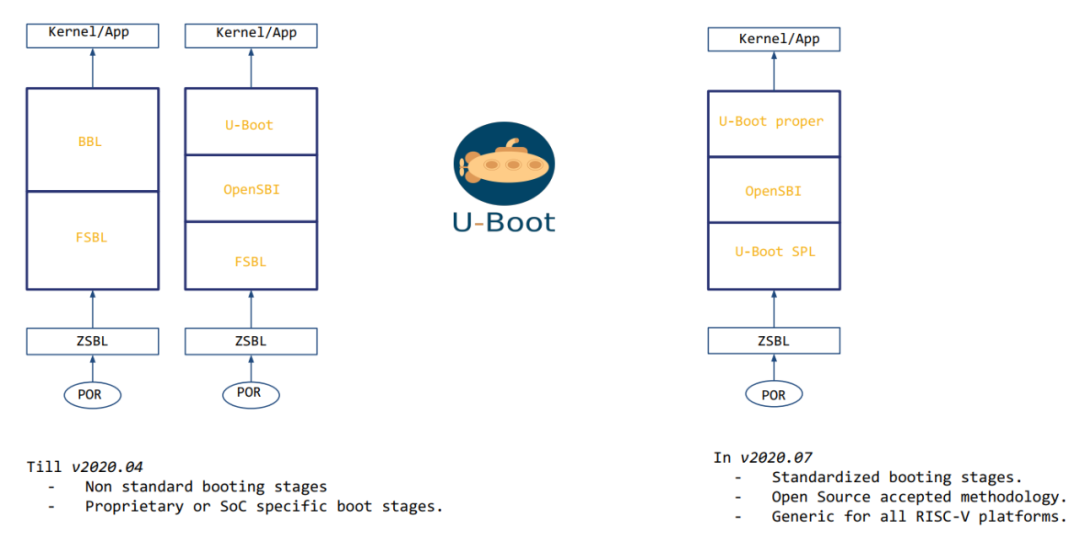

以往芯片厂家都会按照自己的启动规则定义一些启动的流程,比如有些需要SPL+UBOOT,有些可以是直接从SPI或SD卡中boot,这些启动的规则很多,每当使用一款芯片,都需要去理解其启动的流程,十分的复杂。于是就出现了一些规则和定义。

比如苹果公司定义了个人PC电脑的规则:

又比如Linux定义了设备规则等等:

而risc-v虽然目前芯片种类少,但是也需要制定一些启动规则,于是有了下面的规则:

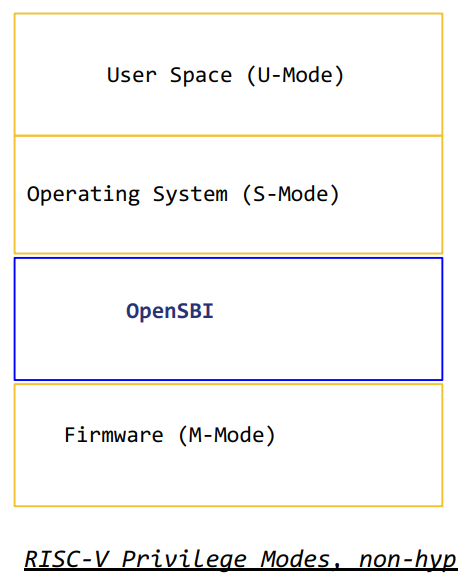

当有了opensbi后,再回头看启动流程,与aarch64之间进行一个对比:

aarch64借助atf框架,从EL3跳转到EL1,并启动u-boot。

对于riscv,上图是一个标准的加载启动流程,其中Opensbi提供了M模式的运行时库。

5.openSBI call接口的实现

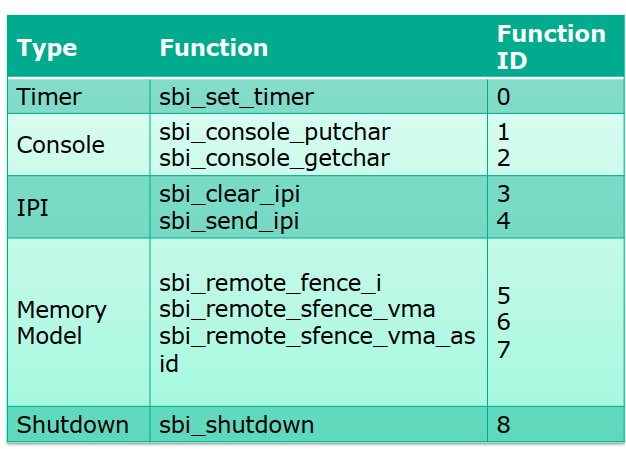

opensbi不仅仅具有加载和引导功能,也能够供S-Mode的OS使用,比如提供串口控制台或者中断的分发等等。调用方式可以通过ecall来实现。类似于syscall的实现规则。当前阶段实现了下面的接口:

详细可以看下面的官方文档描述。

https://github.com/riscv/riscv-sbi-doc/blob/master/riscv-sbi.adoc

6.总结

riscv的启动规范可以按照opensbi的接口实现来自行定义,芯片厂家也可以通过适配opensbi的接口来实现平台通用化的移植,这样将会大大简化上层设计的复杂度。同时规范化的启动流程对于使用者来说更加的友好。相信在这种规范化的模式下,riscv的设计将会越来越完善。

责任编辑:xj

原文标题:关于risc-v启动部分思考

文章出处:【微信公众号:嵌入式IoT】欢迎添加关注!文章转载请注明出处。

-

关于RISC-V芯片的应用学习总结2025-01-29 1862

-

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!2024-08-26 1536

-

RISC-V的MCU关于USB高速通信设计的难点2024-05-27 792

-

RISC-V设计支持工具,支持RISC-V技术的基础2023-07-14 826

-

RISC-V开源带来的思考2023-04-21 794

-

RISC-V 发展2023-04-14 1067

-

关于RISC-V 5大潜力和优势2022-10-14 2985

-

一图看懂RISC-V星光板的启动流程2022-04-22 4043

-

浅谈RISC-V星光板的启动流程2022-03-17 2142

-

RISC-V规范的演进 RISC-V何时爆发?2021-02-11 4382

-

RISC-V如何填补CPU知识空白2020-09-25 3421

-

RISC-V有哪些特点2020-08-25 3191

-

RISC-V你了解多少?2020-08-13 3039

-

科普RISC-V生态架构(认识RISC-V)2020-08-02 6965

全部0条评论

快来发表一下你的评论吧 !