解析RISC-V正面临的挑战

嵌入式技术

描述

新的处理器指令集架构(ISA)并不会经常出现。加州大学伯克利分校开发的开源RISC-V ISA 已经在嵌入式产业中产生了不小的波澜,项目的目的是让开发者能够设计处理器核和生成对应的软件编译器。目前,该项目由RISC-V基金会运作,成员包括众多大学、跨国科技企业(比如谷歌、IBM、微软、英伟达和甲骨文)、芯片厂商和创业公司。

RISC-V 的目标是从其他处理器ISA的错误中学习,这之中的核心是稳定性,既包括指令集和核心本身,也扩展到芯片设计者、编译器作者、操作系统构架师和开发工具供应商。稳定性让强力的处理器核更加易于获取,并增强其可用性,这对于鼓励更多的工程师在整个生态圈中使用这一开源技术而言非常重要。应用开发者可以针对一个冻结的ISA 进行代码优化,在达到最小的内存使用和功耗的同时保证扩展性和对未来设备的兼容性。这使得处理器核开发者可以开发各种不同的指令集实现,从简单的多级流水线(pipeline)到乱序执行(out of order execution)。它们会有不同的延迟、尺寸和功耗,但是它们相互兼容,而且与生态系统中的工具兼容。

整个生态系统的稳定性对于RISC-V 指令集而言至关重要,在设计时RISC-V 考虑了32/64/128位地址空间并保证三者之间的兼容性;其架构还支持扩展,从而提供芯片制造商所需的功能差异和对未来应用场景的支持,不过ISA的基本组成并不会发生变化。

128位的ISA 目前处在开放状态,这是因为嵌入式系统中依然没有多少处理如此巨大的理论内存容量的经验。不过,体系结构对大地址空间的支持正是前瞻思考的证明。针对RISC-V编写和移植的代码可以永久地在类似的RISC-V核上运行,让开发者得以收回投资成本。因为ISA 是开源的,多种硬件实现可以同时进行开发,软件构架师对于最终的硬件实现也就有了话语权。软件架构师对硬件设计者的反馈让RISC-V 核变得更加以软件为中心。市场上已经出现了许多实现RISC-V ISA的处理器核心,基于这些核心也出现了许多不同的片上系统(SoC)芯片。开发RISC-V 处理器核心的厂商包括Codasip、Syntacore、HexFive、T Head,以及已经推出了32和64位SoC的SiFive。

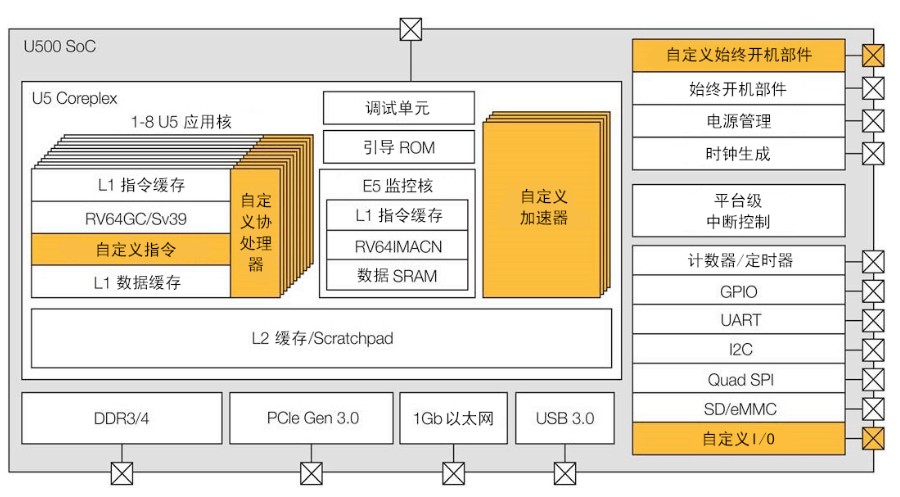

SiFive由Yunsup Lee创立,他是RISC-V 的创始人之一。2017年公司发布首个RISC-V 核和SoC平台家族,以及相关支持软件和开发板,这些芯片包括采用28纳米制造技术的64位多核处理器核心,支持Linux操作系统(见图1),以及采用180纳米制造技术的多外设低成本IoT处理器核心。

图1 SiFive U500 64位多核开源处理器

SiFive的Freedom 平台包含完整的软件规范、用于支持操作系统的板级支持包(BSP)、开发板和基础芯片,允许用户自行扩展/自定义芯片功能。Freedom U500系列多核RISC-V嵌入式应用处理器完全支持Linux,时钟速度为1.6 GHz或者更高。针对机器学习、存储和网络功能的需要,U500支持加速器和快取一致性,这使得处理器能够支持PCIe 3.0、USB 3.0、千兆以太网和DDR3/DDR4等高速外设。

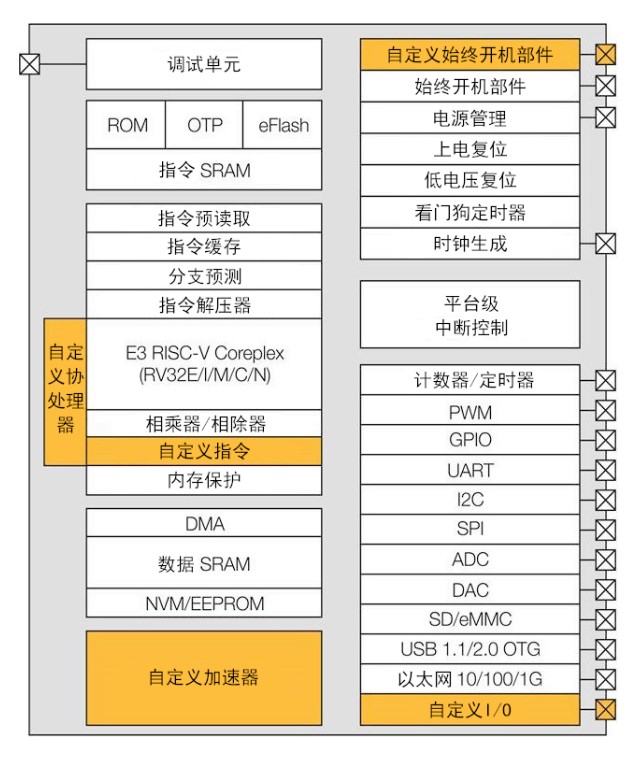

Freedom E300系列(如图2所示)是针对IoT和可穿戴设备市场设计的嵌入式微处理器。基于Freedom E310的HiFive1 兼容Arduino,其上搭载高性能32 位RV32IMAC核心SiFive E31 CPU Coreplex(时钟速度320 MHz以上)。

图2 基于RISC-V ISA的开源E300系列32位微处理器

SiFive还自称在世界最小的嵌入式处理器核中使用了RISC-V指令集(见图3),S2系列IP核最小可配置为只有13500个逻辑门(RV32E 32位版本)。64位的S21嵌入式核心有单独的指令和数据总线,以及两个紧密集成的内存(TIM)单元,这使得SoC可以同时搭载始终开机的32位CPU 和高性能的64位CPU,当应用程序需要更高性能(比如语音活动繁忙的智能设备)时,启动64 位CPU。在边缘节点上,大量的实时任务使得对嵌入式智能的需求大幅增长,这样的设计可以满足互联设备对机器学习和IoT的需求。

图3 HiFive1 RISC-V开发板

开源的RISC-V帮助众多创业公司进入到SoC设计领域中,比如嘉楠科技(Kendryte)、efabless和lowRISC,主流芯片厂商也在使用RISC-V。Microsemi(现在是Microchip的一部分)为SiFive生产了一些开发板,恩智浦有自己的RISC-V芯片,晶芯科技(Andes Technology)和Greenwaves针对RISC-V 开发了芯片和IP。Faraday Technology在下一代边缘计算AI/IoT SoC上的ASIC平台中使用了RISC-V ISA 架构,整合RISC-V IP核和SoC设计验证,全功能设计套件包含了RTOS的支持,配合55纳米工艺制造,适合电池驱动边缘设备及外设应用。

即使ISA是标准的,硬件制造商也能够在设计中相互区分,Faraday Technology 在平台上使用了动态电压频率调整(DVFS)技术,支持电源模式切换和快速系统唤醒,软件库和驱动程序支持特殊接口、传感和电源管理功能的正常使用。

工 具

RISC-V ISA的另一个优势是可以配合多种工具使用,Microsemi在他们的FPGA上配合RISC-V使用多种嵌入式操作系统,比如Express Logic ThreadX、华为LiteOS 和Micrium μC/OS II。Microsemi开发板有RTG4开发套件和PolarFire评估板,套件中包括Microsemi和Olimex 的调试器、引导程序和多个软外设(IP),在GitHub上你可以找到驱动、固件和工程的样例。

UltraSoC是另一个从稳定性中受益的工具公司,他们开发可以嵌入在SoC上用于监控其活动的技术。这项技术用于帮助高效地调试芯片和监控芯片的应用。UltraSoC在晶芯科技高性能的AndresCore IP核和EsperantoTechnologies的AI片上超级计算机上整合自己的技术,这个超级计算机上有数千个RISC-V核。Esperanto的工程团队由RISC 先驱Dave Ditzel领衔,他参与了SPARC RISC处理器的开发。2019年9月,Esperanto使用64位RV64GC ISA完成了10段高性能核ET Maxion的RTL开发工作,样片于2019年下半年面世,芯片计划于2020年实现量产。Esperanto还研发了更加小巧和低功耗的ET Minion 64位核,它使用先进的7纳米制造技术,采用顺序执行指令,支持多线程,并增加了向量浮点数单元,用于支持图形扩展和Google的Tensor AI指令。这两种核在开发中都使用了同一个RISC-V ISA 工具链,其中包括测试和验证工具。两种核被整合到一个超级片上计算机上,搭载16个Maxion和4 096个Minion,Maxion负责运行Linux和其他高层软件,AI类的负载则交由Minion执行。能够使用同一个ISA 让这样的设计成为可能,这正是RISC-V的优势所在。

RISC-V面临的挑战

RISC-V 的开发和市场扩展已经取得了不错的进展,但是前方还是有不少困难。普林斯顿大学的研究者已经在RISC-V的开源处理器核中发现了严重的缺陷,包括不同RISC-V体系结构中超过100个处理存储和内存读取时的顺序错误,不修正它们的话,运行在RISC-V上的软件可能会遇到问题。RISC-V基金会表示:多数RISC-V版本不受这些错误的影响,但是高性能系统会受到很大影响。

通用的32、64和128位(未来将会出现)地址空间,让处理器核开发者可以将注意力转移到特定的处理器实现上。无论是科研项目、IoT节点,还是超级片上计算机,开发者都可以使用同样的编译器、开发工具和调试工具,这让企业不需要针对多种核心维护不同版本的软件,从而降低碎片化,帮助企业专注于提高性能指标。与此同时,开源的精神还意味着对项目的贡献可以造福整个产业界,对扩展指令集的支持使得企业可以在同一个工具链生态系统中进行功能差异化和优化(特别是在安全方面)。RISC-V的特性使得硬件开发者可以根据用户对成本、功耗、安全和性能的要求进行创新。

Mark Patrick: 2014年7月加入Mouser Electronics。Mark曾在德州仪器担任应用支持和技术销售的职位,之后在RS Components任资深市场职务。Mark拥有英国考文垂大学颁发的首席电子工程荣誉学位。

责任编辑:tzh

-

时擎科技亮相2025 RISC-V中国峰会,深度解析高性能RISC-V SoC技术挑战与创新2025-07-21 1869

-

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !2024-09-10 1549

-

rIsc-v的缺的是什么?2024-07-29 1214

-

RISC-V国际人才培养认证中心蒋学刚主任参加RISC-V工作委员会应用调研活动2024-07-10 2208

-

什么是RISC-V2024-02-02 1650

-

RISC-V设计支持工具,支持RISC-V技术的基础2023-07-14 846

-

有没有深度解析RISC-V的文章2023-03-22 996

-

RISC-V拿什么挑战ARM?2023-01-16 1691

-

RISC-V学习笔记【1】RISC-V概述2022-11-24 3436

-

RISC-V不得不面临的专利问题2022-07-08 20796

-

RISC-V的挑战分析2022-02-25 3947

-

RISC-V开发生态和MCU芯片的相关资料推荐2022-02-15 1306

-

RISC-V规范的演进 RISC-V何时爆发?2021-02-11 4408

-

RSIC-V正面临哪些挑战?2018-10-07 15165

全部0条评论

快来发表一下你的评论吧 !