二进制解码器到底是什么

模拟技术

描述

二进制解码器是由单独的逻辑门构成的另一种组合逻辑电路,与编码器完全相反。

名称“解码器”是指将编码信息从一种格式转换或解码为另一种格式,因此二进制解码器使用2 n个输出将“ n”个二进制输入信号转换为等效代码。

二进制解码器是另一种类型的数字逻辑设备,根据数据输入线的数量,其输入的2位,3位或4位代码,因此具有一组2位或更多位的解码器将定义为具有n位代码,因此将有可能表示2 n个可能的值。因此,解码器通常通过将其n个输出中的一个准确地设置为逻辑“ 1”来将二进制值解码为非二进制值。

如果二元解码器接收Ñ输入(通常归类为一个二进制或布尔数)它激活一个且只有其中的一个2个Ñ基于与所有其它输出该输入输出停用。

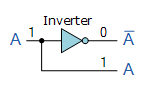

因此,例如,一个逆变器( 非门 )可以被归类为一个1至2个二进制解码器1-输入和2-输出(2 1)是可能的,因为与输入阿它可以产生两个输出甲和甲(不是-A),如图所示。

那么我们可以说标准的组合逻辑解码器是n-m解码器,其中m≤2 n,其输出Q仅取决于其当前输入状态。换句话说,二进制解码器查看其当前输入,确定在其输入处存在哪个二进制代码或二进制数,并选择与该二进制输入相对应的适当输出。

甲二元解码器将编码的输入成编码输出,其中输入和输出代码是不同的和解码器可用于“解码”二进制或BCD(8421码)输入图案以通常为十进制输出代码。常用的BCD到十进制解码器包括TTL 7442或CMOS4028。通常,解码器的输出代码通常比其输入代码具有更多的位,并且实际的“二进制解码器”电路包括2到4、3到8和4至16线配置。

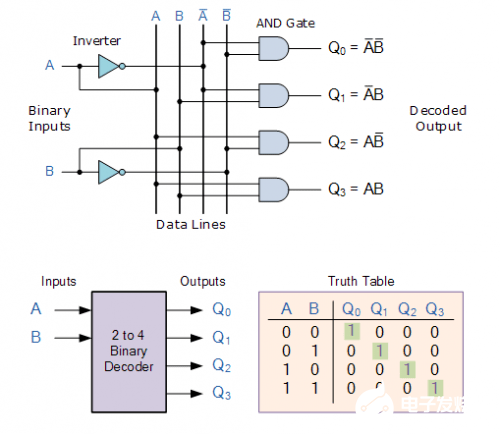

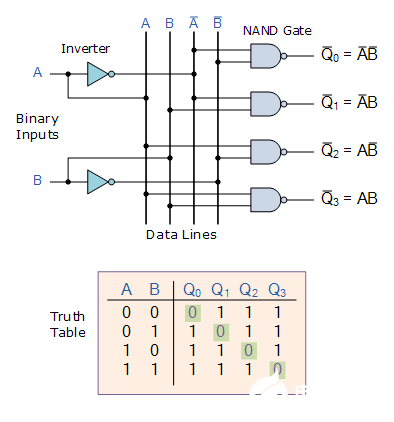

2至4行解码器及其真值表的示例如下:

2对4二进制解码器

上面的2到4行二进制解码器的简单示例由四个“ 与”门的阵列组成。标记为A和B的2个二进制输入被解码为4个输出之一,因此对2到4二进制解码器进行了描述。每个输出代表2个输入变量的最小项之一(每个输出=一个最小项)。

二进制输入A和B确定从Q0到Q3的哪条输出线在逻辑电平“ 1”下为“高”,而其余输出在逻辑“ 0”下保持为“低”,因此在任何情况下只有一个输出有效(高)一度。因此,无论哪条输出线为“ HIGH”,都标识输入处存在的二进制代码,换言之,它“解码”二进制输入。

一些二进制解码器还有一个附加的输入引脚,标为“ Enable”,用于控制设备的输出。此额外的输入允许解码器的输出根据需要设置为“ ON”或“ OFF”。这些类型的二进制解码器通常在微处理器存储应用中用作“内存地址解码器”。

我们可以说二进制解码器是具有用于启动解码器的附加数据线的多路分解器。查看解码器电路的另一种方法是将输入A,B和C视为地址信号。A,B或C的每个组合定义一个唯一的内存地址。

我们已经看到2到4行二进制解码器(TTL 74155)可用于解码任何2位二进制代码以提供四个输出,每个可能的输入组合一个。然而,有时需要二进制输出数量大于可用数量的二进制解码器,因此通过添加更多输入,解码器可能会提供2 n更多的输出。

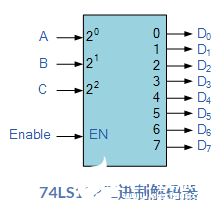

因此,例如,具有3个二进制输入(n = 3 )的解码器 将产生3到8行解码器(TTL 74138),而4个输入( n = 4 )将产生4到16行解码器(TTL) 74154)等。但是,解码器也可以具有少于2 n的输出,例如BCD到七段解码器(TTL 7447),该解码器具有4个输入和只有7个活动输出来驱动显示器,而不是像您那样将其输出为16(2 4)个输出期望。

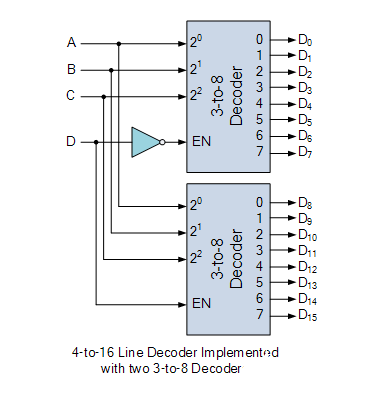

在这里,已经使用两个较小的3至8解码器实现了更大的4(3数据加1使能)至16行二进制解码器。

4到16二进制解码器配置

输入A,B,C用于选择任一解码器上的哪个输出为逻辑“ 1”(高),输入D与启用输入一起使用,以选择第一个或第二个编码器将输出“ 1”。

但是,可用于一个特定解码器的输入数量是有限制的,因为随着n的增加,产生输出所需的AND门的数量也会变大,从而导致用于驱动的门扇出他们越来越大。

此类有源“ HIGH”解码器可仅使用反相器( 非门 )和与门实现。使用“ 与”门作为输出的基本解码元素非常方便,因为仅当其所有输入均为逻辑“ 1”时,它才会产生“高”或逻辑“ 1”输出。

但是有些二进制解码器是使用“ 与非”门代替“ 与”门构建其解码输出的,因为与“与”门相比,“与非”门的生产成本更低,因为它们需要更少的晶体管来实现其设计。

使用“ 与非”门作为解码元件,将导致有效的“ LOW”输出,而其余的将为“ HIGH”。当“ 与非”门产生具有反相输出的“ 与”运算时,“ 与非”解码器的反相真值表看起来像这样。

2至4行NAND二进制解码器

然后,对于NAND解码器,在任何给定时间只有一个输出为LOW且等于逻辑“ 0”,而所有其他输出为逻辑“ 1”时为HIGH。

解码器还可提供一个附加的“使能”输入引脚,该输入引脚可通过分别对它们施加逻辑“ 1”或逻辑“ 0”来使解码输出变为“ ON”或“ OFF”。因此,例如,当使能输入为逻辑电平“ 0”(EN = 0)时,无论输入A和B的状态如何,所有输出均为逻辑“ 0”的“ OFF”(对于AND门)。

一般来实现这个功能使得能够在2输入AND或NAND栅极与3-输入替换AND或NAND门。附加输入引脚代表使能功能。

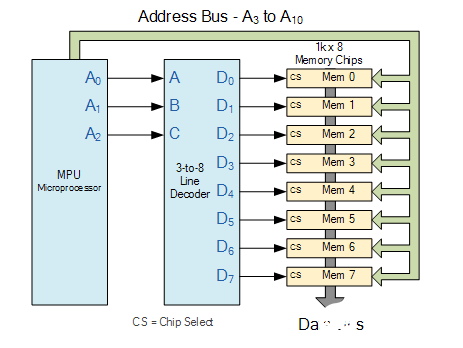

内存地址解码器

二进制解码器最常用于更复杂的数字系统中,以基于计算设备产生的“地址”访问特定的存储位置。在现代微处理器系统中,所需的内存量可能会很高,并且通常不止一个内存芯片。

克服此问题的一种方法是将许多独立的存储芯片连接在一起,并在公共“数据总线”上读取数据。为了防止同时从每个存储芯片“读取”数据,每个存储芯片一次要一个一个地选择,此过程称为地址解码。

在这种类型的应用中,地址代表编码数据输入,而输出则是特定的存储元件选择信号。每个存储芯片都有一个称为“ 芯片选择”或CS的输入,MPU(微处理器单元)使用它来在需要时选择合适的存储芯片。通常,片选(CS)输入上的逻辑“ 1” 选择存储设备,而输入上的逻辑“ 0”取消选择存储设备。

因此,通过一次选择或取消选择每个芯片,可以使我们为特定的地址位置选择正确的存储器地址设备。地址解码的优势在于,当我们指定特定的存储器地址时,相应的存储器位置仅存在于其中一个芯片中。

例如,让我们假设我们有一个非常简单的微处理器系统,仅具有1Kb(一千个字节)的RAM存储器和10条可用的存储器地址线。该存储器由128×8位(128×8 = 1024字节)设备组成,对于1Kb,我们将需要8个单独的存储芯片,但是为了选择正确的存储芯片,我们还需要3至8行二进制解码器如下所示。

内存地址解码

二进制解码器仅需要3条地址线(A 0至A 2)来选择8个芯片中的每个芯片(地址的下部),而其余8条地址线(A 3至A 10)则选择正确的存储器该芯片上的位置(地址的上部)。

使用地址总线选择存储位置后,特定内部存储位置上的信息将发送到公共“数据总线”以供微处理器使用。这当然是一个简单的示例,但是对于所有类型的存储芯片或模块,其原理均相同。

二进制解码器是将一种数字格式转换为另一种数字格式的非常有用的设备,例如将二进制或BCD类型的数据转换为十进制或八进制等,常用的解码器IC是TTL 74LS138 3至8行二进制解码器或74ALS154 4至16线解码器。

-

探讨2对4二进制解码器及4到16二进制解码器配置2020-12-29 13102

-

labview中的二进制存储2014-03-03 3760

-

二进制2009-04-06 9007

-

同步二进制计数器2009-09-30 12946

-

二进制编码和二进制数据2009-10-13 5253

-

什么是二进制计数器,二进制计数器原理是什么?2010-03-08 31993

-

二进制电平,什么是二进制电平2010-03-17 2755

-

二进制加法程序【汇编版】2015-12-29 936

-

二进制编码的十进制表示转换解码器2019-06-24 16838

-

二进制解码器案例说明2019-06-22 10830

-

数字二进制计数器的设计和实现2022-07-28 2828

-

二进制解码器开源设计2023-06-16 766

-

二进制串行计数器工作原理是什么?2024-05-28 2292

-

二进制编码器工作原理 如何选择二进制编码器2024-11-06 4032

-

探索CD4555B与CD4556B:高性能CMOS双二进制至1-of-4解码器/多路分解器2026-01-16 410

全部0条评论

快来发表一下你的评论吧 !