基于EP2c35 FPGA和NiosII 软核实现视频监控系统的设计

可编程逻辑

描述

随着视频监控系统的广泛应用,人们对监控系统的实时性提出了更高的要求,特别是在数据的高速采集应用中,传统技术在处理速度上面临着严峻的考验,当前通用的解决方案很难满足用户日益提高的需求。为此,Altera 公司于2006 年4 月7 日提出了C2H 技术。这个技术的实质是通过硬件映射的方式直接用硬件对C 语言进行加速,获得系统性能的提高。

本文将 C2H 技术应用于视频监控系统的数据存储功能部分,有效的加快了数据的读写速度,使系统的性能得到大幅度的提升。

1 C2H 技术介绍

1.1 C2H 的特点

C2H 是一种可以直接对ANSI C 函数定制硬件加速的技术,在推出短短的一年时间内就得到了嵌入式及FPGA 设计者的广泛使用。C2H 编译器能分析程序要加速实现的存储器接口类型,生成硬件加速器逻辑以及合适的Avalon(总线互联架构)的主机和从机接口,达到与存储器延时的匹配。这样,分担了处理器的数据计算和存储器访问任务,使处理器能够更好的处理其他任务。数据表明,与未采用C2H 加速的系统相比,采用NiosII C2H 编译器加速的系统性能提高了10 到45 倍,而耗费的逻辑资源仅比处理器本身多出0.7 至2.0 倍。NiosII C2H 编译器是基于Eclipse 的NiosII 集成开发环境(IDE)中的一个插件。同时,C2H编译器具有识别并行运行事件的功能,能在硬件中同时运行相互独立的事件。与前面结果无关的事件将被尽早的执行。软件调用以线程的方式进行加速——每个加速器完全并行运行,真正的多任务系统(CPU, 硬件加速器)。

1.2 C2H 的使用流程

C2H的使用需要进行反复的调试,直到性能符合设计要求。具体流程如下:

(1)在NiosII中开发和调试C程序;

(2)分析C程序,找到最适合加速的部分;

(3)将需要加速的代码段写成一个独立的子函数;

(4)指定这个函数为硬件加速的函数;

(5)在NiosII IDE中重新编译整个工程;

(6)分析硬件加速的结果,观察C2H*估报告;

2 视频监控系统的设计

设计中选用的是 Altera 公司生产的CycloneII 系列中的EP2c35 FPGA。CycloneII 系列是低成本嵌入式处理解决方案,具有可以扩展外设集、存储器、I/O 的特点。同时Altera 公司免费提供NiosII 嵌入式处理器。NiosII 软核是一个32 位RISC 嵌入式处理器,性能超过200MIPS,满足当前系统的设计要求。Altera 公司提供了一整套针对NiosII 软核的SOPC 开发工具,轻松实现从底层的硬件设计到上层的软件开发。

2.1 视频监控系统的总体设计

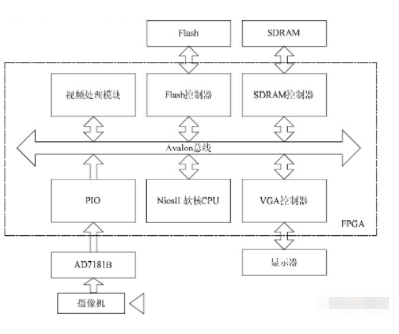

本文中设计的视频监控系统的基本构成是现场实时采集图像的摄像机、视频解码芯片AD7181B、视频D/A 芯片ADC7123、VGA 控制器、Flash、SDRAM 控制器及控制核心NiosIICPU。整个系统除A/D 和D/A 采用专用芯片外,其余部分均在FPGA 上实现。视频监控系统的硬件设计框图如下图1 所示:

图1 系统硬件设计框图

各模块功能描述如下:NiosII 软核CPU 是32 位的RISC 嵌入式处理器,为整个系统的中枢;SDRAM,是系统大容量的数据缓冲存储区域;Flash,存储系统的硬件和软件的系统上电配置数据;视频处理模块,实现对视频流的ITU656 解码、去隔行、格式转换等功能。

2.2 C2H 在视频监控系统的应用

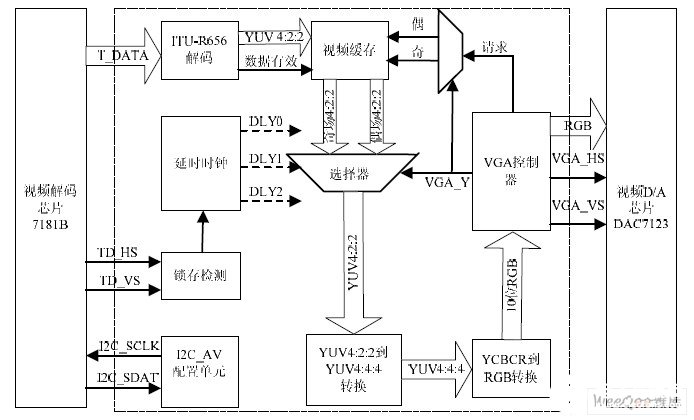

下图 1.2 详细表示出了系统中视频数据流的处理过程。

图2 视频数据流处理过程图

从上图 2 可以看出,数据流处理过程是先经过视频解码芯片AD7181B 的模数转换,变成8 位的数字视频信号;再由ITU-R656 解码器解码,使视频格式变成YUV4:2:2;然后对视频流进行去隔行处理。去隔行处理中,需要将奇场数据和偶场数据分别存于两个FIFO(FIFO A 和FIFO B)中,然后再以两倍的频率按ABABA……的顺序读出,便可完成视频的去隔行处理。最后经过YUV 到RGB 时域变换,便可在VGA 控制器的控制下在显示器上进行显示。由于视频解码A/D 和视频D/A 是由专用的芯片完成,速度很快,未对系统的速度有太大影响。经过分析比较,系统性能提升的瓶颈是数据中间处理中的数据读写等环节。由于涉及到从存储器读数和写数,使这部分成为系统中最耗时的部分。所以提高系统性能的关键是从减少数据读写的时间耗费入手。本设计中针对这一点,采用C2H 技术,对数据的读写进行硬件加速。进行加速部分程序如下:

其中,dest_ptr 是数据目的地址,source_ptr 是数据原地址,length 是字节数,测试中length取1048576 个字节长。

实现过程按照论文 1.2 节所述。首先,经过对时耗的分析比较,确定耗时最多的部分是数据读写部分。因此,确定这个环节为加速对象,并将其编写为独立的子函数,即上述的c2h_acceleration 函数,然后在IDE 中直接选择以上函数,点击右键,选择HardwareAcceleration,最后再重新生成系统并编译整个工程。

3 结果分析比较

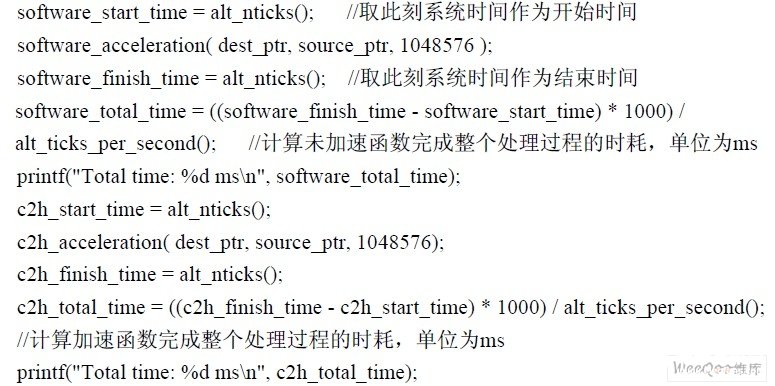

为了进行加速性能比较,在系统中又定义了一个与c2h_acceleration功能相同的函数:software_acceleration,然后对函数c2h_acceleration进行C2H加速。并将结果与未采用C2H加速的software_acceleration比较。定义了测试函数,部分代码如下:

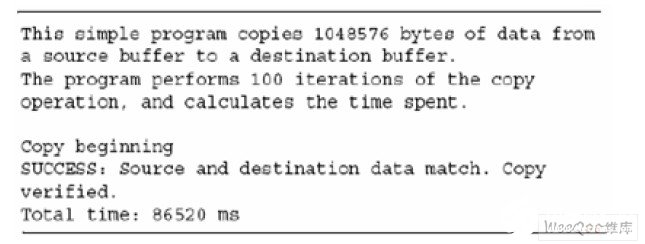

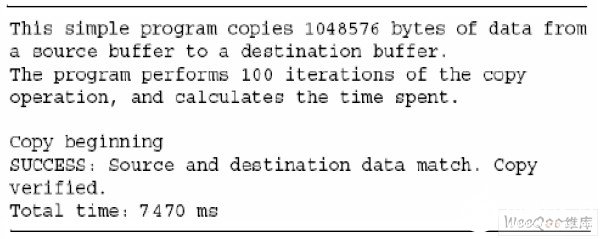

编译运行后,分析硬件加速的结果,观察C2H*估报告,可以清楚的从运行结果看出通过C2H加速后性能的提高。未进行C2H加速的函数读写1048576字节的运行结果如下图3所示,经过C2H加速的函数运行结果如下图4所示。

图 3 未进行C2H加速测试结果

图 4C2H加速后的测试结果

从图3和图4的结果可以看出来,软件实现读写1048576字节数据需要86520ms;经过C2H硬件加速后耗时减小至7470ms,速度提升多达11倍。

4 结 论

本文介绍了一个在 Altera 公司提供的EP2c35 FPGA 上设计的视频监控系统。

本文作者创新点:在视频监控系统中应用C2H 技术对数据读写环节进行加速,使数据的读写速度提高了11 倍,提升了整个系统的性能。本文的设计方法和实现技术适合在对数据处理实时性要求较高的视频产品中应用,有很大的实用价值。

责任编辑:gt

-

基于FPGA解决方案的SOPC技术实现二维条码识别系统的设计2020-07-21 2869

-

如何实现视频采集与DVI成像系统的设计2019-04-22 3183

-

请问FPGA的NIOSII只是一个软核吗?2019-04-08 2646

-

基于NiosII软核的视频解码系统优化设计2018-03-19 1118

-

EP2C35A用户手册V1(一版)2017-10-28 1631

-

基于EP2C35的DSP阵列板通信接口设计与实现2017-10-19 1018

-

基于FPGA的高炉TRT顶压控制系统的研究2012-10-16 790

-

基于FPGA视频监控系统的设计2012-05-22 4208

-

基于FPGA的乒乓游戏机设计2010-02-24 674

-

EP2C8 FPGA SOPC(NiosII)学习开发套件V3.02009-11-02 2975

-

EP2C5型 FPGA/SOPC(NiosII)学习开发套件 V3.02009-10-23 4737

-

基FPGA Cyclone II_EP2C5 EP2C8的频2008-11-30 1056

-

基于FPGA NiosII的MPEG-4视频播放器2008-10-09 2028

全部0条评论

快来发表一下你的评论吧 !