基于可编程逻辑器件和VHDL语言实现算术逻辑单元的设计

可编程逻辑

描述

1、引 言

随着可编程逻辑器件的发展,FPGA的应用已经越来越广泛,且用可编程逻辑器件代替传统的普通集成电路已成为一种发展的趋势。可编程逻辑器件FPGA以其高集成度、高速度、开发周期短、稳定性好而受到了人们的青睐,并得到了广泛的应用。由于算术逻辑单元(ALU)在运算中对系统性能要求很高,而采用中小规模的集成电路设计的系统既庞大又存在稳定性的问题。因此,用可编程逻辑器件FPGA来实现算术逻辑单元是一个很好的选择。而硬件描述语言(HDL)是使用可编程逻辑器件的不可缺少的工具,所以本文选用VHDL语言。并以设计4位算术逻辑单元为例,来实现算术逻辑单元的功能,又通过纯组合逻辑电路和超级进位方法的应用,使得在高速可编程逻辑器件FPGA的基础上,实现了算术逻辑单元在速度上的进一步优化。

2、电路设计

本算术逻辑运算单元可实现与、或、非、异或、逻辑左移、逻辑右移的逻辑运算和加、减、乘、除的算术运算等10种功能,也可以根据需要进行功能的增

减,这也体现出了用VHDL语言设计硬件系统的灵活性。

2.1 设计思想

该ALU单元采用模块化设计。共划分了4个模块:控制与逻辑运算电路模块(Control)、加减法电路模块(Addsub)、乘法电路模块(Mul)和除法电路模块(div)。总体构成如图1所示。

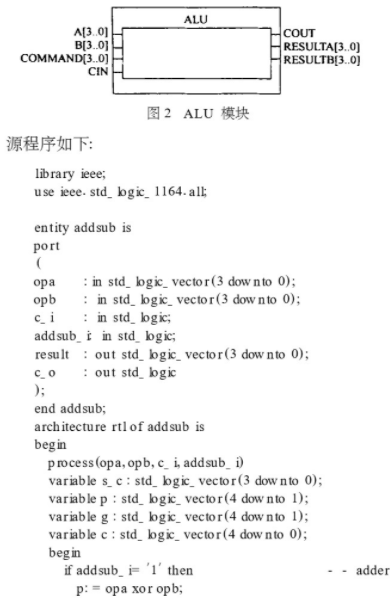

ALU模块图如图2所示。图中A,B为2个4位的输入;Command为功能选择输入;CIN为加减法的进位和借位输入;COUT为加减法的进位和借位的输出;Resulta和Resultb为2个4位的输出,乘法时Resultb存放积的高4位,Resulta存放积的低4位,除法时Resulta 存放商,Resultb存放余数。

2.2 各模块分析

(1)控制模块(Control) 该模块对系统的工作进行总体控制。根据对Command输入的信号分析来决定ALU执行的功能,并进行加减法模块、乘法模块、除法模块的选择和输出的控制。在程序中使用3个CASE语句来实现。第1个CASE语句控制逻辑运算的实现,第2个CASE语句控制加减法模块、乘法模块、除法模块的选择,第3个CASE语句控制输出的选择。

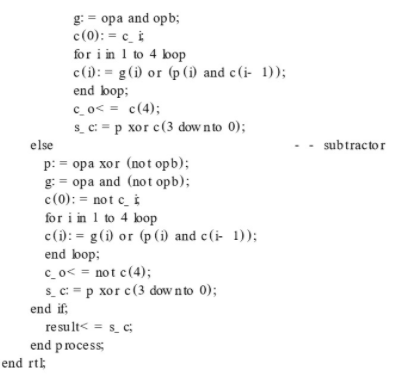

(2)加减法模块(Addsub) 本设计中减法运算通过加补码的方式由加法器实现,这样可以简化系统 前进位(有关超前进位的内容可参阅文献[1]的应用,使得加法器速度受进位限制的问题得到解决。

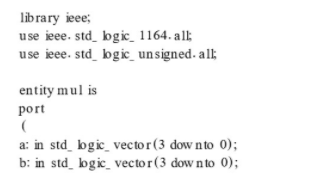

(3)乘法模块和除法模块(Mul,Div) 乘法、除法模块也采用了纯组合逻辑电路的设计。比时序逻辑构成的乘除法器在速度上具有优势。编程原理采用通过逐位相加减的方法来实现。乘法模块源程序如下:

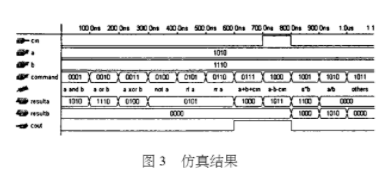

2.3 系统仿真

最后采用VHDL语言中的例化语句对上述各模块进行整合,并对其进行仿真,得到了预期的效果。实现了ALU的各项功能。仿真图如图3所示。

3、结 语

随着EDA技术的发展,可编程逻辑器件FPGA和VHDL语言在硬件电路设计中,越来越显示出其优越性,本设计即是一个很好的验证。通过实际的应用和日常的实验中的使用,该ALU系统体现出了良好的稳定性,在速度上也能很好的满足系统的要求。

责任编辑:gt

-

可编程逻辑器件2014-04-15 3693

-

基于EDA技术的可编程逻辑器件在数字信号处理系统中的应用2019-06-28 2211

-

可编程逻辑器件是如何发展的?2021-04-29 1885

-

PLD可编程逻辑器件2021-07-22 2335

-

可编程逻辑器件设计2006-03-25 1191

-

可编程逻辑器件基础及应用实验指导书2010-03-24 798

-

什么是PLD(可编程逻辑器件)2009-06-20 30094

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1178

-

可编程逻辑器件(书皮)2022-07-10 809

-

什么是可编程逻辑器件2020-06-04 10435

-

利用C/C++语言实现大规模可编程逻辑器件的应用设计2020-09-11 1809

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 2278

-

可编程逻辑器件的结构2023-03-24 2186

-

可编程逻辑器件测试2023-06-06 1331

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4615

全部0条评论

快来发表一下你的评论吧 !