ESR、ESL如何影响电容?

描述

看到这个标题, 估计很多人已经笑了. 如果看完这篇文章你还在笑, 那说明你真的很了解.

如果你真的觉得自己了解, 那就不用继续往下看了.

我记得当年毕业找工作时面试了大大小小10几家公司, 形形色色的面试题也见了不少, 但关于RLC最最基本的电路相关问题几乎是必问的, 更有甚者几乎一半问题都是与此有关. 为什么? 一切都是从基础开始的. 这是一句我以后会不断重复的话, 这也是我目前为止对电路的理解. 再复杂再酷炫的电路也离不开这些, 如果真的搞明白了, 对以后理解更高级的东西会有很大的帮助.

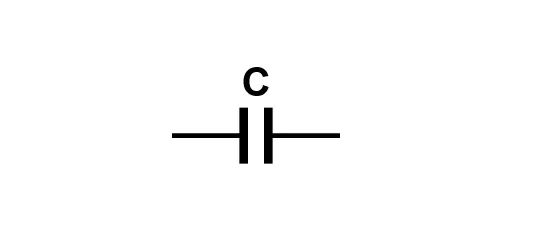

众所周知, 电容, 两边加上电压, 就能开始充电储存电荷. 理想状态下, 就是一个C:

可现实永远是残酷的, 你会发现你所做的一切几乎都是和在这些非理想的问题作斗争.

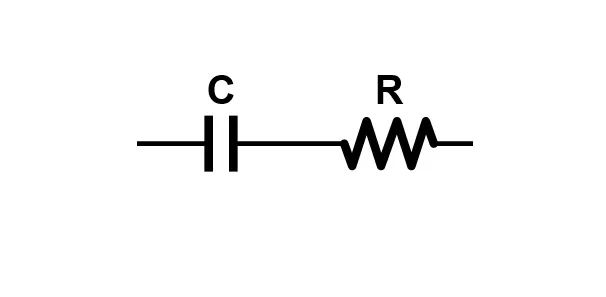

ESR(Equivalent Series Resistance)

如果你去看电容的datasheet(比如去Murata的关网随便找一个), 每个非理想电容都会有一个叫ESR的指标. 顾名思义, 电容本身会有一个等效串联电阻, 那么电容的等效电路就变成了:

这个电阻一般有多大呢? 通常是在100mΩ ~ 1000mΩ不等, 具体数值大小根据电容种类和电容值大小来定, 这里先不细说, 我会在之后比较不同电容的区别时详细讲解.

那么肯定会有人问这么小的串联电阻, 会有什么大的影响么? 不好意思, 还真会有, 在要求极其苛刻情况下还会把两个电容并联以减小ESR. 比如 LDO 的output capacitor, 如果这个ESR过大或者过小, 很有可能会引起LDO的stability问题.

另一方面, 当电容被用做电源的decoupling cap时, 你希望的是这个R越小越好. 当电容被用做的decoupling cap时, 其作用是为了提供高频的电流供给. 假如你的芯片电源会有一个非常短暂的100mA的peak current, 而且这个电流几乎是你的decoupling cap来提供的, 如果你的电容ESR有1Ω,想象一下100mA的电流流过这个电阻, 到达另一端的时候, 已然有了100mV的压降了.

所以一句话: 通常情况下, 你希望这个电阻越小越好. 除了用于例如LDO的输出电容, ESR的大小会影响到LDO的稳定性, 但这个问题说来话长, 有机会单独开一篇细讲.

说完R, 我们来讲讲L.

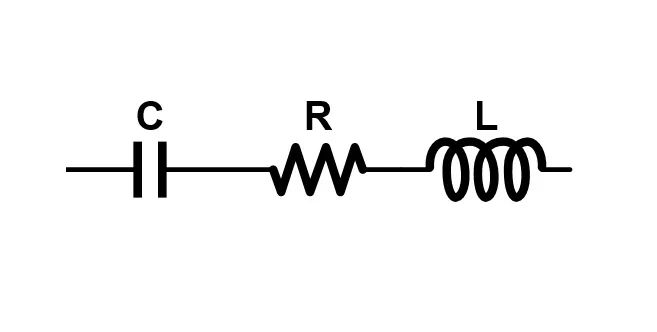

ESL(Equivalent Series Inductance)

很多情况下这是一个往往被人忽略的一个指标, 你经常会看到ESR的spec, 很多电容的datasheet往往都没有ESL这个spec在里面. 但是随着信号频率的越来越高, ESL是完全不能被忽视的. 既然如此, 电容的等效电路又要变成这样:

ESL主要影响的是电容的高频特性. 通常这个ESL是很小的, 即便如此, 当信号的频率高到一定程度, 这个L的阻抗会变得不可忽略, 当频率继续升高, Z_{L} 会逐渐的变大, 因此电容就开始逐渐的开始看起来像一个电感. 同样的情况, decoupling cap其中一个重要的作用是用来提供瞬时的大电流的, 而这里的L会尝试阻止电流的瞬时变化, 因而如果ESL太大, 会使得decoupling cap的作用大大降低, 尤其是在高频的情况下.

上图来自:

通常情况下, 当你打开一个电容的datasheet, 你会找到如上图所示的一个电容阻抗 v.s. 频率的一个图表. 这张图清楚的表示了ESR和ESL是如何改变理想电容的阻抗v.s. 频率的曲线的.

责任编辑:lq

-

电容器频率特性360度全解析2011-11-18 4163

-

电容的ESR是什么意思2014-12-30 3394

-

怎么计算陶瓷电容的ESR和ESL2015-07-16 23715

-

电容器的ESR特性2019-05-24 2476

-

ESR与ESL对电容高频特性有什么影响2019-05-31 1912

-

ESR,ESL对电容有何影响?2021-03-05 2431

-

什么电容的ESR2021-05-25 2174

-

ESR/ESL/电容容量2011-10-31 16641

-

DC-DC电路电容等效电阻ESR和等效电感ESL2016-12-17 1908

-

esr与esl对电容高频特性有什么影响?2017-11-23 29604

-

ESR,ESL,如何影响电容?资料下载2021-04-04 1779

-

为什么电容可以去耦? ESR和ESL对于电容滤波作用的影响2023-02-08 5159

-

关于电容频率的特性分析2023-12-08 2355

-

贴片电容选型指南2025-04-17 1443

全部0条评论

快来发表一下你的评论吧 !