通过小脚丫板载的两个数码管来显示字符

描述

今天我们任务是通过小脚丫板载的两个数码管来显示字符,所以首先我们要了解一下数码管的基本工作原理,接下来再研究怎么通过捣鼓小脚丫把数码管给点亮,并且显示出有效信息。

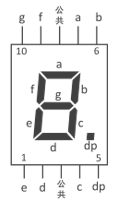

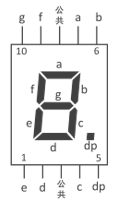

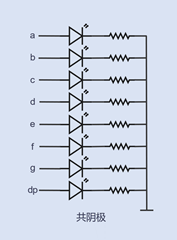

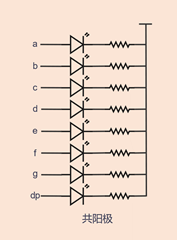

图1 7段数码管

图1 7段数码管

小脚丫板载的数码管是7段数码管(如果包括右下的小点可以认为是8段),它分别由a、b、c、d、e、f、g位段和表示小数点的dp位段组成,见图1。

图1 7段数码管

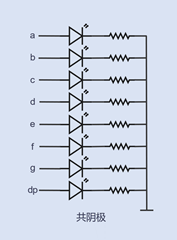

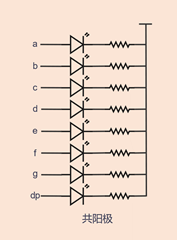

图1 7段数码管数码管的各个段位是由LED灯组成的,控制每个LED的点亮或熄灭实现数字显示。通常数码管分为共阳极数码管和共阴极数码管,结构如图所示。共阴8段数码管的信号端低电平有效,而共阳端接高电平有效。比如,使共阳端数码管的a段发光,则在a段信号端加上低电平即可。共阴极的数码管则相反。

小脚丫的板载数码管为7段共阴极数码管,可以显示数字0-9以及字母A-F共计16种选择。因此,如果我们需要数码管能显示所有的16种选择,需要至少4位输入码(24=16)。表1列出了各个数码管字符所对应的LED灯段位。

表1 各数码管字符所对应的LED灯段位

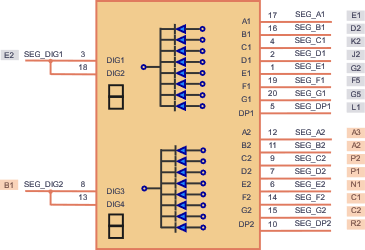

图2标注了小脚丫板载的两个数码管的各LED段位以及小脚丫上所对应的引脚。其中SEG_DIP为公共端,因此在共阴极数码管的设计中需要接低电平。可以看出,每一个数码管都含有9个引脚,因此每一个字符的显示都需要由一个9位的输出信号来实现。

图2

接下来我们通过Verilog实现对数码管的控制。其中,我们将模块的输出定义为两个7段数码管,每个数码管有9个引脚,分别由9位信号控制。输入端由4路信号控制,可以分别对应0-F等十六个字符选择。

module segment(input wire[3:0] seg_data_1, //四位输入数据信号,可通过4个拨码开关控制input wire[3:0] seg_data_2, //四位输入数据信号,可通过4个按键开关控制output wire[8:0] segment_led_1, //数码管1,MSB~LSB =SEG,DP,G,F,E,D,C,B,Aoutput wire[8:0] segment_led_2 //数码管2,MSB~LSB =SEG,DP,G,F,E,D,C,B,A);reg[8:0] seg [15:0]; //存储7段数码管译码数据initialbeginseg[0]=9'h3f; // 0seg[1]=9'h06; // 1seg[2]=9'h5b; // 2seg[3]=9'h4f; // 3seg[4]=9'h66; // 4seg[5]=9'h6d; // 5seg[6]=9'h7d; // 6seg[7]=9'h07; // 7seg[8]=9'h7f; // 8seg[9]=9'h6f; // 9seg[10]=9'h77; // Aseg[11]=9'h7C; // bseg[12]=9'h39; // Cseg[13]=9'h5e; // dseg[14]=9'h79; // Eseg[15]=9'h71; // Fendassign segment_led_1 = seg[seg_data_1]; // 将对应字符导入数码管1并显示assign segment_led_2 = seg[seg_data_2]; // 将对应字符导入数码管2并显示endmodule

上述代码是定义7段共阴极数码管的通用模块,可以保存起来作为一个独立模块。这样,在以后遇到需要用数码管显示的实验时我们可以直接调用(之后我们还会讲解如何调用子模块),而不用再重新写一遍代码。

接下来是提问环节:

当我们指定用拨码开关SW1-SW4来控制左边数码管,按键开关K1-K4来控制右侧数码管,此时如果开关的状态分别如下图所示,数码管应该显示什么字符?

注:拨码开关调至上方为1,下方为0。按键开关白色为1(松开),黑色为0(按下)。大家可以当作课后练习来巩固一下知识,也欢迎在公众号留言给出自己的答案。

而为了帮助更多老师快速上手FPGA的使用和教学,在即将到来的寒假,我们针对高校从事教学/实验室一线工作的教师,推出一个为期5天(2021年1月25日-1月29日)的FPGA设计及应用快速培训,通过实用性非常强的典型案例动手实践,帮助大家快速、有效地上手FPGA,并能够在未来的教学、实践、电赛中大显身手,硬禾实战营也将成为参加培训的老师们长期的教学后援。

责任编辑:xj

原文标题:基于FPGA的数字电路实验3:点亮数码管

文章出处:【微信公众号:FPGA入门到精通】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

【基于Lattice MXO2的小脚丫FPGA核心板】工程创建和固件烧录2024-01-31 3361

-

【基于Lattice MXO2的小脚丫FPGA核心板】03数码管显示控制2024-02-29 5294

-

使用同一个程序,单个数码管就有反应,两个数码管就没有显示,怎么回事啊?2018-05-05 4674

-

六个数码管轮流显示数字2016-05-11 989

-

数码管显示的多种方式2017-09-06 2560

-

8个数码管静态显示_数码管的动态显示2018-01-16 20926

-

PIC单片机实现8个数码管实现循环显示的设计2019-09-10 3598

-

8只数码管滚动显示单个数字的两个仿真电路图免费下载2019-12-27 1437

-

通过小脚丫FPGA搭建实验电路并验证一个二进制比较器2021-01-06 6515

-

如何用小脚丫FPGA核心板实现4位加法器功能2021-10-11 6328

-

8个数码管循环显示数字2022-10-20 883

-

怎么通过捣鼓FPGA板把数码管给点亮并显示有效信息?2023-06-20 2613

-

单片机是如何控制数码管显示各种字符的?2023-12-13 4569

-

数码管显示屏的静态显示编程是什么2024-08-28 2053

全部0条评论

快来发表一下你的评论吧 !