通过小脚丫FPGA搭建实验电路并验证一个二进制比较器

描述

前一篇文章我们介绍了通过小脚丫FPGA核心开发板来进行门电路的实验过程。当然,我们还可以画出更多复杂的门电路组合,并且通过小脚丫FPGA轻松实现对应的输入/输出特性的定义。现在,我们利用小脚丫来学习更多具有特定功能的实用组合逻辑电路。

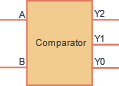

本篇中,我们希望设计一个二进制比较器,通过小脚丫FPGA搭建实验电路并验证结果。

顾名思义,二进制比较器就是比较两个二进制数的大小,因此对于一个两位输入的比较器来说,其输出结果不外乎有小于,大于和等于三种可能。因此我们列出这个电路的真值表。

表1 二进制比较器真值表

|

A |

B |

Y2(A |

Y1(A>B) |

Y0(A=B) |

|

0 |

0 |

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

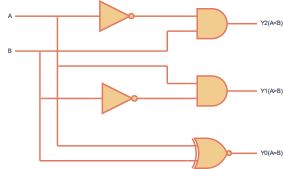

相信学习过数字电路课程的同学都知道如何将该电路进行逻辑运算,化简并画出对应的门电路组合,因此该步骤我们不在此过多赘述,直接上图。

图1 电路图

图2 门电路组合

通过Verilog代码,我们对该电路进行硬件描述。这次我们采用Data-flow的写法,代码中出现的!&^等符号,实际上就是等于同直接对数据进行逻辑运算,并分别对应NOT, AND, OR。希望大家之后对这些符号的熟悉程度就如同看¥$€等符号一样亲切。module comparer1(inputwire A, //定义输入的两个数a、binputwire B,outputwire Y2, //定义三种输出结果对应的ledoutputwire Y0,outputwire Y1);assign Y2 =(!A) & B; //对应Aassign Y1 = A & (!B); //对应A>Bassign Y0 =!(A^B); //对应A=Bendmodule

在完成代码编译后,我们将输入变量A和B以及输出变量Y2,Y1,Y0分别对应至小脚丫的板载外设上。

表2 各变量对应小脚丫相应引脚

|

变量 |

小脚丫 |

|

A |

SW1 |

|

B |

SW2 |

|

Y2 |

L1 |

|

Y1 |

L2 |

|

Y0 |

L3 |

这样,我们就在小脚丫上构建了一个二进制比较器,我们可以通过调节输入编码开关,并观察LED灯的现象来验证我们的设计。

文章的最后我们提两个问题:1. 如果我们将开关SW1, SW2拨至如下图所示,L1,L2,L3所对应的状态应该是怎样的?注意:小脚丫板载的LED是低电平点亮,也就是说,当输出为1时,LED熄灭,反之则亮。

图3

2. 假如现在小脚丫上L2、L3处于点亮状态,那么拨码开关SW1和SW2现在应该是什么状态?(图中将拨码开关放置中间未知仅为示意作用,实际不存在中间状态)。

图4

是不是入手很简单,随后能够很方便地做扩展和结果验证?今天的内容到此结束,下一篇我们会介绍如何通过小脚丫实现更多实用且有趣的组合逻辑电路实验,敬请期待。

责任编辑:xj

原文标题:基于FPGA的数字电路实验2:比较器的实现

文章出处:【微信公众号:FPGA入门到精通】欢迎添加关注!文章转载请注明出处。

-

二进制编码器工作原理 如何选择二进制编码器2024-11-06 4134

-

怎么去设计一个基于FPGA的二进制比较器呢?2023-06-20 2899

-

基于FPGA的二进制时钟设计方案2022-05-13 3622

-

如何用小脚丫FPGA核心板实现4位加法器功能2021-10-11 6328

-

如何通过FPGA实现一个流水灯?2021-06-06 9632

-

小脚丫FPGA的综合技能学习平台2021-01-06 6924

-

二进制与十进制数对照显示实验,十进制,二进制对照2018-09-20 4004

-

二进制电平,什么是二进制电平2010-03-17 2773

-

二进制编码和二进制数据2009-10-13 5268

-

同步二进制计数器2009-09-30 12965

-

二进制时钟电路2009-09-11 3369

-

十六位二进制数比较器2009-04-13 5256

-

二进制2009-04-06 9036

全部0条评论

快来发表一下你的评论吧 !