如何操作ECO方式更新RAM/ROM初始值更方便?

描述

各种类型的Memory在FPGA设计中被广泛使用,例如单端口RAM、简单双端口RAM、真双端口RAM、单端口ROM以及双端口ROM。这些RAM或ROM都可通过coe文件的形式定义其初始值。那么可能在实际应用中会出现这样一种情形:设计的其他部分未做任何改动,只是更新RAM初始值。那么该如何操作更为方便呢?

如果采用传统方式,先定义好coe文件,然后重新生成IP,这样就必须重新执行整个设计流程包括综合、布局布线,编译时间可想而知。但换个角度,细细分析一下,只是初始值改动,那么能否通过ECO(Engineering Change Order)的方式实现呢,就像更改触发器初始值或者查找表的真值表内容一样?答案是肯定的。这样做好处也是显而易见的:无需重新布局布线,只需更改RAM相关属性,然后再次生成.dcp(这个不是必须的),最后生成.bit或.bin文件,这样最大程度地继承了原有设计,也最大程度地缩短了编译时间。采用此方法的前提是RAM的规格要保持不变,这里的规格包括数据位宽和RAM深度。

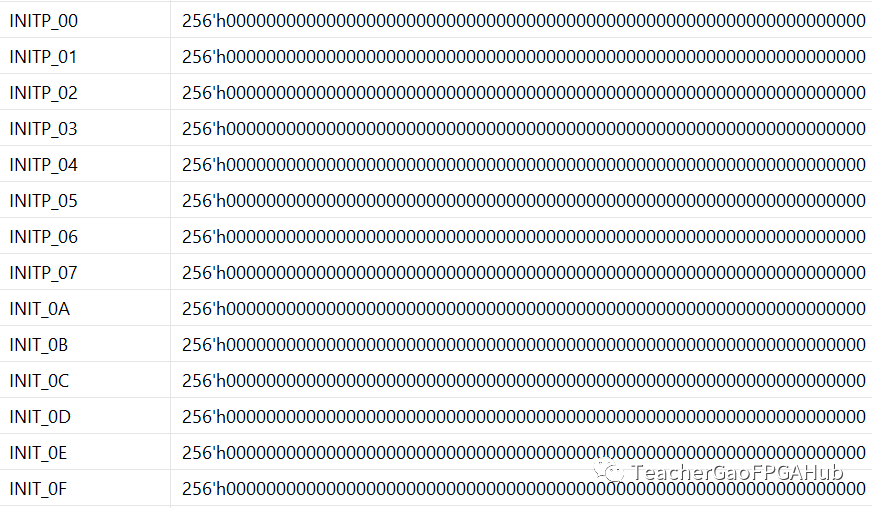

这里我们以Block RAM为例,先看看有哪些属性与初始值密切相关,如下图所示。基本上凡是以INIT打头的属性都与初始值相关。更新初始值本质上就是重新设定这些初始值。这些初始值是在IP生成阶段根据coe内容被设定的。

第一步,根据更新后的coe文件生成一个同规格的IP,并对该IP执行OOC综合。

第二步,打开第一步生成的.dcp文件,找到相应的Block RAM,获取上文提到的这些属性对应的属性值。

原文标题:ECO方式更新RAM/ROM初始值

文章出处:【微信公众号:Lauren的FPGA】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

RAM和ROM的区别,哪个与CPU连接2024-01-31 5138

-

全局变量的初始值,是在哪里赋值的?2023-10-27 1899

-

手机上的ROM和RAM技术原理2023-03-30 4300

-

如何使用FPGA内部的ROM以及程序对该ROM的数据读操作2022-02-08 13329

-

MCU内部的RAM上电之后的初始值到底是什么2021-11-10 1599

-

如何保证MCU上电后RAM的初始值唯一2021-11-05 669

-

采用IEEE745格式的浮点+ROM RAM的方式成功实现FFT的设计2021-07-30 1215

-

由RAM上电后初始值引起的问题2021-04-28 1132

-

教你们怎么去设定寄存器的初始值2021-04-01 8921

-

想要对RAM初始化该怎么操作2019-06-06 9886

-

具有VHDL初始值的分布式RAM?2019-02-26 1985

-

浅析MCU内部的RAM上电之后的初始值相关问题2019-01-05 7152

-

在哪里可以在PAR之后检查RAM的初始值2018-10-10 1618

-

换路定律及初始值的确定2009-05-10 4959

全部0条评论

快来发表一下你的评论吧 !