如何借助Cyclone 10 GX ATX PLL refclk切换实施功能模拟

描述

你知道如何借助Cyclone 10 GX ATX PLL refclk切换实施功能模拟吗?嵌入式流转换器实施ATX PLL重配置和通道重配置以及实施ATX PLL和通道再校准呢?想学啊?我(视频)教你啊。

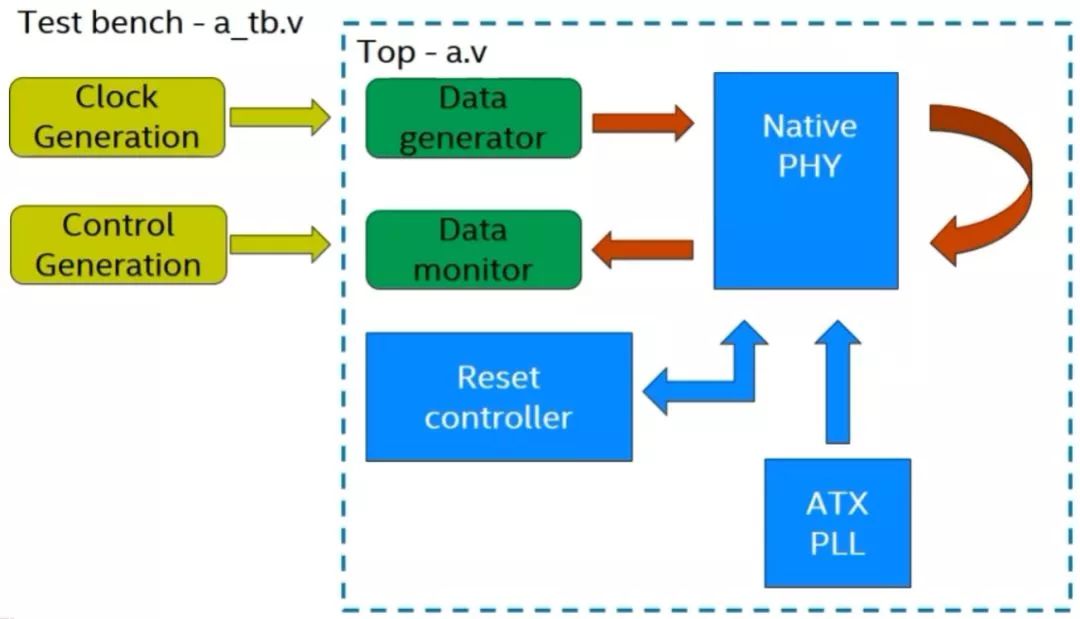

设计中的实例包括:Native PHY、TX PLL、重置控制器,数据和时钟生成逻辑等。两个refclk用于支持,无法通过TX本地除法器实现的两个不同数据速率。125MHz用于2Gbps,150MHz用于1.2Gbps。

在模拟开始时,收发器以2Gbps的数据速率运行,然后使用ATX PLL refclk切换动态重配置,重新配置为1.2Gbps。ATX PLL refclk切换通过寄存器写操作实施,接着使用嵌入式流转换器进行ATX PLL重配置和再校准,然后就可以实施CDR refclk切换、通道重配置和再校准了。

温馨提示

在上面的视频中有实施ATX PLL refclk切换的高级步骤,详情见视频。

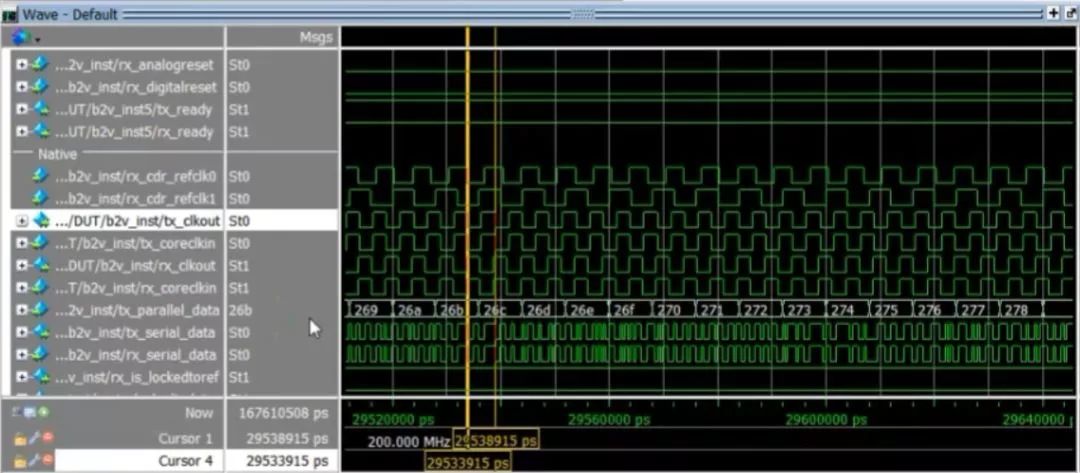

在最后的运行模拟示例中,我们可以看到增量数据从TX发送至RX。在启动过程中,收发器通道的运行速率为2Gbps。PCS内核宽度为10比特时,tx_clkout频率为200MHz。在实施ATX PLL refclk切换和通道重配置后,收发器通道的运行速率变为1.2Gbps。Tx_clkout频率将变为120MHz。这显示ATX PLL refclk切换和通道重配置已成功完成。

责任编辑:xj

原文标题:参考时钟切换动态重配置不会玩儿?我教你啊

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

#英特尔FPGA应用 如何实施英特尔 Cyclone 10 GX ATX PLL 参考时钟切换动态重配置电子技术那些事儿 2022-08-27

-

如何使用Cyclone器件中的PLL2021-01-15 1249

-

Cyclone 10 GX开发套件板的电路原理图免费下载2020-08-19 1353

-

Cyclone V GX启动套件的用户手册免费下载2019-10-16 957

-

借助 Altera Remote Update IP对 Cyclone 10 LP 进行配置(1)2018-06-22 7400

-

简述 Cyclone 10 GX DDR3 设计的步骤2018-06-20 7127

-

Cyclone IV 器件中的时钟网络与PLL2017-11-14 3256

-

基于EP1C3的进阶实验cyclone_PLL_Test22016-10-27 528

-

Cyclone器件中PLL的配置方法2016-02-23 1249

-

Altera Cyclone IV GX系列FPGA开发方案2012-05-31 9898

-

模拟PLL,模拟PLL是什么意思2010-03-23 2849

全部0条评论

快来发表一下你的评论吧 !