基于复杂可编程逻辑器件的VME总线接口逻辑系统的设计

可编程逻辑

描述

作者:阎稳,王国东,姜运生

机载计算机的几何结构一般采用高强度机箱和底板来连接各功能模块。底板总线类型大部分采用VME总线规范。VME总线是1981年Motorola等公司为欧洲板(Euroboard)设计的总线,是欧洲通用模块(VME-Versa Module Europe)的首字母缩写。经过二十多年的演变发展,已经成为美国国家标准。它以高性能、并行性、实时性和高可靠性四大特点赢得机载计算机青睐,模块结构具有良好的抗震性,抗冲击能力。本文结合我们的实际工作,重点介绍VME总线接口逻辑的工程实践方法。

VME总线简介

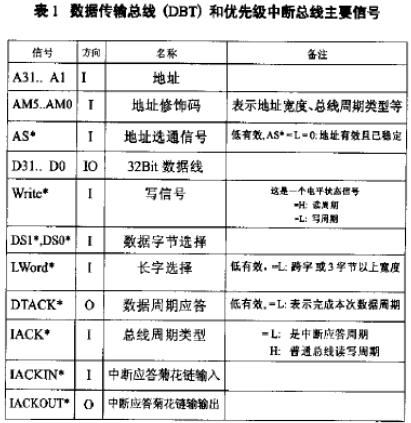

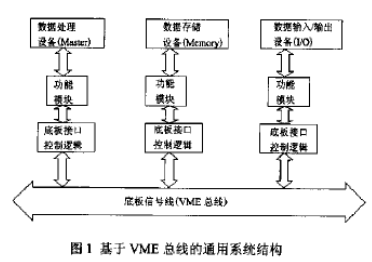

VME总线建立了8位、16位、32位和64位并行传输计算机体系,能够实现单个或多个微处理器共存的对等分布式系统。VME总线是一种紧耦合(Closely coupled)总线,将微处理器、数据存储器以及外设控制器通过总线统一互联起来,实现高速通讯。物理上采用96芯或160芯标准连接器,各功能模块分别插在其中某一个插槽(slot)中。图1是VME总线系统的通用结构,它包括4个子总线,即数据传输总线,优先级中断总线,仲裁总线,工具总线。表1是其中数据总线和优先级中断总线主要信号的定义。

在VME总线的4类子总线中,数据传输总线(DTB-Data Transfer Bus)和中断优先总线(PIB-Priority Interrupt Bus)包含了主要信号。VME总线允许多个处理器控制总线,所以必须有系统总线管理者,即系统控制器。它位于VME总线的一号插槽上,功能包括:提供系统时钟、总线仲裁器、中断响应菊花链驱动器和总线定时器,还可能包括串行时钟驱动器、电源监视器功能。总线周期类型主要由地址修饰码AM(Address Modifer)规定,主要包括读周期、写周期、块读周期、块写周期、信号复用周期等周期。寻址单元以字节为单位,可以进行单字节、双字节、3字节、4字节,甚至8字节存取。字节界限可以是偶地址或奇地址,可以通过数据选通信号DS1*和DS0*,LWord* 以及A2 A1地址线的组合决定。

VME数据总线通用访问逻辑设计

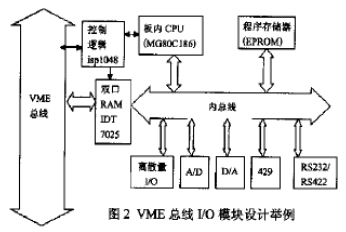

VME总线各功能模块现在一般设计为智能型,把自己映射成整个VME总线地址空间的一部分。在模块内部一般都有自己的CPU管理模块内功能接口,然后通过双口存储器和主控模块交换数据。这样,对各功能模块的访问统一转换成对存储器的访问。图2是我们为歼轰七机载计算机设计的VME总线的I/O 模块,下面以此为例说明DTB总线控制逻辑。

在图2中,板内CPU可以根据需要选择,内总线随CPU型号而变化,但必须对底板提供VME总线接口。控制逻辑需要处理的主要信号如表1所示,其中信号方向从VME总线进入本模块为输入,否则为输出。

在表1中可以看到,数据线只有32-Bit,地址只有31位,如何实现64Bit传输,这涉及到信号复用(Multiple)问题。在32Bit以下模式,地址线和数据线是独立的两组信号。在64Bit模式下,将访问周期分为两个相位阶段(Phase),阶段是地址阶段,用D31..D0的数据线传输高32Bit地址。在第二阶段是数据阶段,利用31Bit地址A31..A1以及长字选择LWord*作为高32Bit数据。显然,在64Bit模式下,从方模块应该设计一个64Bit地址锁存器,将相位阶段的地址稳定锁存,保证第二阶段的数据寻址正确。6位地址修饰码AM5..AM0用来定义本次总线寻址模式,即地址宽度和传输性质,如16地址块传输等,可以产生64种寻址类型。

图2中的I/O模块是作为系统从设备,当主控方选择访问时,控制逻辑首先应该产生系统选择信号,以启动模块内数据通路。可以用以下方法实现:

…

VA15,VA14,VA13 pin; // VME 总线地址高 3 位

VA3,VA2,VA1 pin; // VME 总线地址低 3 位

VAM5..VAM0 pin; // VME 总线地址修饰码

VAM node;

VDS1,VDS0 pin; // 字节选择。

VAS,VRW pin; // 地址选通、读写信号

…

VAM = VAM5 & !VAM4 & VAM3 & !VAM2 & !VAM1 & VAM0; // = 10.1001: 短管理访问

// 为双口普通读写产生片选信号

!CS_VME = !VAS & VIACK & VAM & (VAddr 》= StartA ddr) & (VAddr 《= EndAddr);

// VME 数据总线使能

!VDEN = (!VDS1 # VDS0) & !CS_VME #

// 普通DTB读写时要开门

!VIACK & !VIACKIN & (IntID == MyIntID);

// 应答中断时也要开门

VDIR = !VRW; // VME 数据方向

…

上面一段逻辑代码,主要判断地址修饰码AM和地址映像范围,产生VME总线访问启动信号,亦即双口RAM的片选信号CS_VME。为增强信号驱动能力,在模块输出数据信号前插入双向驱动。VDEN信号就是数据驱动器的开门信号,数据方向控制信号VDIR由读写信号反相后产生。当从模块完成DTB周期后,应该驱动DTACK*,通知主控模块本次访问完成。这个信号各个从模块都要驱动,一般在控制逻辑产生应答后加OC驱动(如54F05)。其上拉电阻由底板统一,若由各模块自行上拉,势必造成并联电阻值变小,灌电流变大,严重影响信号驱动能力,使各模块不能同时工作。这个信号产生的逻辑涉及到下面的菊花链中断处理,详细逻辑方法可参考下节。

菊花链中断优先级逻辑设计

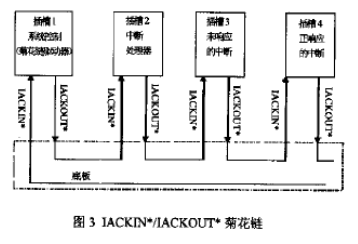

VME优先级中断机制采用菊花链,它用于在板与板之间传送一电平信号。它始于槽而终结于一槽。系统可以提供IRQ1*~IRQ7*共7个中断请求,其中IRQ7*具有优先级。当中断处理器处理中断请求时,中断应答菊花链驱动器启动中断应答菊花链工作,以确保只有一个中断器响应正在进行中的中断应答周期。整个原理示意如图3所示。当应答某个中断时,首先把IACK*信号驱动为低,表示当前周期是中断应答周期,同时将中断识别码通过数据线传输,而中断响应主要由中断响应输入(IACKIN*)和中断响应输出(IACKOUT*)组成应答菊花链。若某一模块发出中断请求,并且响应的中断识别码和自己匹配,同时要接到上传下来的有效的IACKIN*信号。若是自己的中断响应,应该堵塞IACKOUT*信号,使之为高电平,否则应该继续下传IACKOUT*信号。显然,若某一插槽为空或者不具备中断响应能力,应该将IACKIN* 和IACKOUT* 短接,否则菊花链将中断。当中断响应后,要及时撤除中断请求。下边逻辑实现菊花链优先级中断,其中状态机处理包含数据总线访问周期和菊花链中断实现的所有逻辑。

// VME 中断管理逻辑。

VCLK pin; //VME 总线时钟,16MHz

VMID3..VMID0 pin; //底板为该模块分配的标识

VIACK pin; //VIACK = 0: VME 中断应答周期

= 1: VME 普通总线周期

VIACKIN ,VIACKOUT pin; //中断应答菊花链输出/输出

Qv2,Qv1,Qv0 pin istype ‘REG’; //VME 总线操作控制状态机

VDTACK pin istype ‘REG’; //VME 总线读写完成应答,

//高有效,经OC 门后低有效

VIRQ3 pin istype ‘REG’; //向VME之中断请求

VD3..VD0 pin istype ‘REG’; //要发送的中断应答向量(具 有输出 /OE 之缓冲)

MyIntID = [0,1,1]; //通过 VA3 VA2 VA1 送来的中

断应答号,本模块使用 IRQ3*

图3 LACKIN*/IACKOUT*菊花链

MyVector = [VMID3..VMID0]; //本模块使用的中断应答向量

IntID = [VA3,VA2,VA1]; //VME 送来的 IRQ 号

IntVec = [VD3..VD0]; //本模块应答时的中断向量

// VME 中断申请 和 清除 状态编码

IntS0 = ^B0;

IntS1 = ^B1;

EQUATIONS

// 以下语句确立VME 总线器控制由系统时钟管理

[Qv2,Qv1,Qv0].clk = VCLK;

VDTACK.clk = VCLK;

IntVec.clk = VCLK;

VIRQ3.clk = VCLK;

IntVec:= !MyVector; // 中断应答向量随时准备放出去

// 放出中断应答向量。

IntVec.OE = !VIACK & !VIACKIN & // 中断应答周期

(IntID = MyIntID); // 而且是我们的

。.

//==========================================

// VME 总线周期控制之状态机 (包括中断应答)

//==========================================

State_Diagram [Qv2,Qv1,Qv0];

State SV0:

VIACKOUT = 1; // 不能乱传中断应答

VDTACK := 0; // 不能随便应答

if (!RST) then SV0

else if (!CS_VME) then SV1 // VME 普通读写

else if (!VIACK & !VIACKIN) then SV4

else SV0; // 原地待命

State SV1: // 普通读写周期

VIACKOUT = 1; // 不传中断应答

VDTACK := 0;

if (!RST) then SV0

else SV2; // 顺延

State SV2:

VIACKOUT = 1; // 不传中断应答

VDTACK := 0; // 还在干

if (!RST) then SV0;

else if (!BUSYL) then SV2 // 双口正忙

else SV3

with { VDTACK := 1;}

State SV3:

VIACKOUT = 1; // 不传中断应答

VDTACK := 1; // 准备好了

if (!RST) then SV0

else if (!CS_VME) then SV3 // 本周期没完没了

else SV0

with {VDTACK := 0; }

// SV4..SV7 为中断应答周期

State SV4:

VIACKOUT = H; // 情况不明,先别往下传

VDTACK := L;

if (!RST # VIACK # VIACKIN) then SV0

else if (IntID == MyIntID) then SV6 // 应答我们的

with {

VDTACK := H; // 早已准备好

}

else SV5 // 应答别人的

with {VIACKOUT = L; } // 赶快往下传

State SV5:

VIACKOUT = L; // 传。传.传

VDTACK := L;

if (!RST) then SV0

else if (!VIACK & !VIACKIN) then SV5

// 还在中断应答周期

else SV0; // 总算熬到结束了

State SV6:

VIACKOUT = H; //是自己的,不能往下传

VDTACK := H;

if (!RST) then SV0

else if (!VIACK & !VIACKIN) then SV6

// 还在中断应答周期

else SV0;

State SV7:

goto SV0; // 非法状态,赶快转

//=========================================

// 本状态机实现 VME 总线中断请求和清除控制

//=========================================

State_Diagram [VIRQ3]

State IntS0:

//对 011AH 读写,触发对 VME 中断请求

if (!RST) then IntS0

else if (!CS_ALLP & (IOAddr == VMEIRQReg))

then IntS1

else IntS0; // 老实呆着

State IntS1:

// 此状态时,保持中断请求

if (!RST ) then IntS0

else if (!VIACK & !VIACKIN & (IntID == MyIntID))

then IntS0 // 已经应答

else IntS1; // 不应答不走

END

结束语

VME总线的应用愈来愈广泛,各种机载计算机系统总线都在逐渐向它靠拢。按照以上思想设计的机载计算机已经经过了试飞阶段,实践也证明VME总线性能和可靠性优于以前的各种总线。

责任编辑:gt

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4568

-

可编程逻辑器件测试2023-06-06 1297

-

可编程逻辑器件的结构2023-03-24 2125

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 2246

-

可编程逻辑器件(书皮)2022-07-10 782

-

PLD可编程逻辑器件2021-07-22 2319

-

可编程逻辑器件是如何发展的?2021-04-29 1869

-

可编程逻辑器件2014-04-15 3674

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1162

-

可编程逻辑器件基础及应用实验指导书2010-03-24 784

-

可编程逻辑器件在积分式A/D转换器中的应用2009-08-29 1012

-

什么是PLD(可编程逻辑器件)2009-06-20 30042

-

基于单片机的复杂可编程逻辑器件快速配置方法2009-03-28 1157

-

可编程逻辑器件设计2006-03-25 1179

全部0条评论

快来发表一下你的评论吧 !