高质量仿真,从参考频率开始

描述

如果没有深入了解 PLL 理论以及逻辑开发过程,可能你在设计并调试锁相环(PLL)电路时会感到非常棘手。那有没有比较容易理解或学习妙招呢?小A今日就为大家送上一份妙计锦囊,并提供有效、符合逻辑的方法助你调试PLL问题。请往下看~

高质量仿真,从参考频率开始

如果不在特定条件下进行仿真,则估计一个 PLL 电路的规格将会是十分困难的。因此,进行 PLL 设计的第一步应当是仿真。建议工程师使用ADIsimPLL 软件运行基于系统要求的仿真,包括参考频率、步进频率、相位噪声(抖动)和频率杂散限制。

许多工程师面对如何选择参考频率会感到无所适从,但其实参考频率和输出频率步进之间的关系是很简单的。采用整数 N 分频 PLL,则输出频率步进等于鉴频鉴相器(PFD)输入端的频率,该频率等于参考分频器 R 分频后的参考频率。采用小数 N 分频 PLL,则输出频率步进等于 PFD 输入频率除以 MOD 值,因此,您可以使用较高的参考频率,获得较小的频率步进。决定使用整数 N 分频或是小数 N 分频时,可牺牲相位噪声性能换取频率步进,即:较低的 PFD 频率具有更好的输出频率分辨率,但相位噪声性能下降。

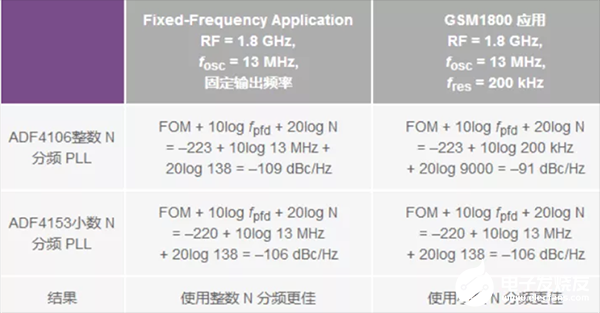

例如,表1显示若要求具有固定频率输出以及极大的频率步进,则应首选整数 N 分频 PLL(如ADF4106),因为它具有更佳的总带内相位噪声。相反,若要求具有较小的频率步进,则应首选小数 N 分频 PLL(如ADF4153),因为它的总噪声性能优于整数 N 分频 PLL。相位噪声是一个基本的 PLL 规格,但数据手册无法针对所有可能的应用指定性能参数。因此,先仿真,然后进行实际硬件的测试就变得极为关键。

表1. 相位噪声确定 PLL 的选择

甚至在真实条件下通过 ADIsimPLL 仿真 PLL 电路时,结果也可能是不够的,除非真实参考以及压控振荡器(VCO)的模型文件已包含在内。如果未包含在内,则仿真器将使用理想参考和VCO 进行仿真。若要求高仿真精度,则花在编辑 VCO 和基准电压源库文件上的时间将会是值得的。

PLL 使用与放大器类似的负反馈控制系统,因此环路带宽和相位裕量的概念此处依然适用。通常,环路带宽应设为 PFD 频率的十分之一以下,且相位裕量的安全范围为 45°至 60°。此外,应当进行针对真实电路板的仿真和原型制作,以便确认电路符合 PCB 布局对寄生元件、电阻容差和环路滤波器电容的规格要求。

有些情况下,暂时没有合适的电阻和电容值,因此工程师必须确定是否能使用其他值。在 ADIsimPLL 的"工具"菜单中隐藏了一项小功能,称为"BUILT"。该功能可将电阻和电容值转换为最接近的标准工程值,允许设计人员返回仿真界面,验证相位裕量和环路带宽的新数值。

寄存器值的判定

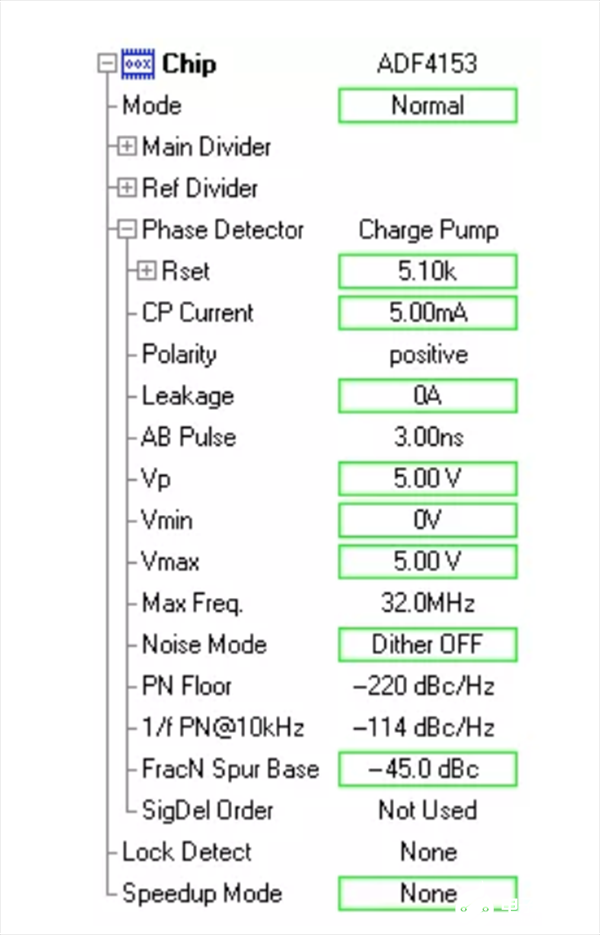

ADI PLL 提供很多用户可配置选项,具有灵活的设计环境,但也会产生如何确定存储在每个寄存器中数值的难题。一种方便的解决方案是使用评估软件设置寄存器值,甚至 PCB 未连接仿真器时也能这么做。然后,设置文件可保存为.stp 文件,或下载至评估板中。图 1 显示 ADIsimPLL 仿真结果,提供诸如VCO 内核电流等参数的建议寄存器值。

图 1. ADIsimPLL 仿真软件提供寄存器设置的建议值

原理图和 PCB 布局

设计完整 PLL 电路时,需牢记几点。首先,重要的是匹配 PLL的参考输入端口阻抗,将反射降至最低。另外,保持电容与输入端口并联组合值尽量小,因为它会降低输入信号的压摆率,增加 PLL 环路噪声。更多详细信息请参考 PLL 数据手册上的输入要求。

其次,将模拟电源与数字电源相分离,最大程度减少它们之间的干扰。VCO 电源特别敏感,因此此处的杂散和噪声可轻易耦合至 PLL 输出。更多注意事项以及详细信息,请参考利用低噪声 LDO 调节器为小数 N 分频压控振荡器(VCO)供源,以降低相位噪声 (CN-0147)

再则,用于组成环路滤波器的电阻和电容应当放置在尽可能离PLL 芯片近的地方,并使用仿真文件中的建议值。若您在改变环路滤波器元器件值之后发现难以锁定信号,请尝试使用最初用于评估板的数值。

对于 PCB 布局而言,其主要原则是将输入与输出分离,确保数字电路不会干扰模拟电路。例如,若 SPI 总线太过靠近参考输入或 VCO 输出,则访问 PLL 寄存器时,VCO 输出会在 PLL输出端产生杂散现象。从热设计角度来看,可在 PLL 芯片底下放置一个导热接地焊盘,确保热量流经焊盘,到达 PCB 和散热片。在极端环境下使用时,设计人员应计算 PLL 芯片和 PCB 的所有热参数。

有效利用 MUXOUT

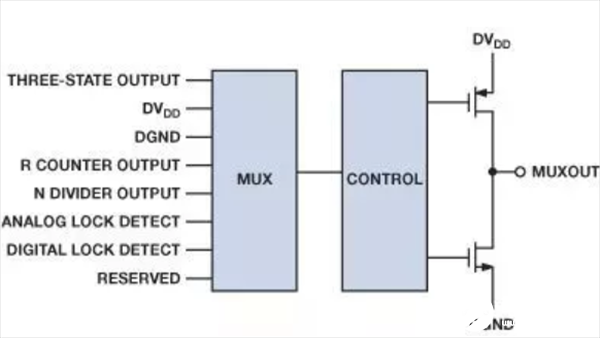

在调试阶段开始时,若 PLL 不锁定,则很难确定应当从何处开始。第一步,可以使用 MUXOUT 查看是否所有内部功能单元都正常工作,如图 2 所示。例如,MUXOUT 能显示 R 计数器输出,指示参考输入信号良好,且寄存器内容成功写入。MUXOUT 还能检查检测器的锁定状态,以及反馈环路中的 N分频输出。通过这种方法,设计人员可确定每个分频器、增益或频率值是否正确。这是调试 PLL 的基本过程。

图 2. MUXOUT 引脚辅助 PLL 进行调试

时域分析助力PLL调试

调试 PLL 时,使用时域分析,演示写入串行外设接口(SPI)总线上的寄存器数据是正确的。虽然读写操作需要的时间比较长,但请确保 SPI 时序符合规格,且不同线路之间的串扰减小到最低程度。

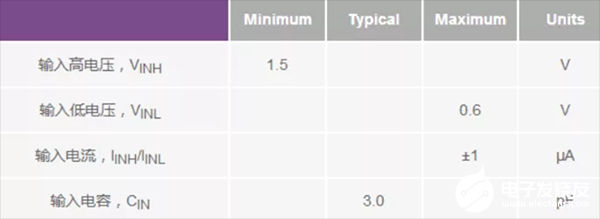

应当参考 PLL 数据手册中的时序图,以便确定数据建立时间、时钟速度、脉冲宽度和其他规格。确保留有足够的裕量,以便在所有条件下都满足时序要求。使用示波器检查时域内的时钟和数据边沿位于正确位置。若时钟和数据线路太过接近,则串扰会使时钟能量通过 PCB 布线耦合至数据线路。这种耦合会导致数据线路在时钟的上升沿产生毛刺。因此,读写寄存器时需检查这两条线路,尤其当寄存器出现错误时。确保线路电压满足表 2 的规格。

表 2. 逻辑输入

复杂的频谱分析

频域中的问题更常见、更复杂。如果使用频谱分析仪,则应当首先检查 PLL 输出是否锁定;如果波形具有稳定的频率峰值则表示锁定。如果未锁定,则应当遵循前文所述的步骤。如果 PLL 已锁定,则收窄频谱分析仪带宽,以便确定相位噪声是否位于可接受范围内,并将测试结果与仿真结果对照确认。测量某些带宽条件下的相位噪声,如 1 kHz、10 kHz 和 1 MHz。

若结果与预期不符,则应首先回顾环路滤波器设计,检查 PCB板上元器件的真实值。然后,检查参考输入的相位噪声是否与仿真结果一致。PLL 仿真相位噪声应与真实值接近,除非外部条件有所不同,或向寄存器写入了错误值。

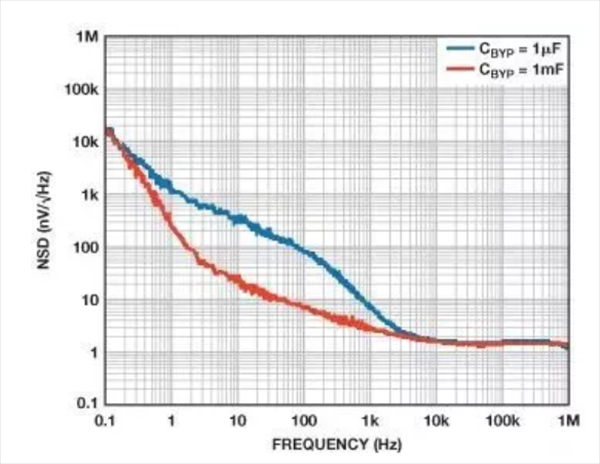

电源噪声不可忽略,哪怕使用了低噪声 LDO。因为 DC-DC 转换器和 LDO 都可能成为噪声源。LDO 数据手册显示的噪声频谱密度通常会影响噪声敏感型器件,比如 PLL(见图 3)。为PLL选择低噪声电源,特别是需要为VCO的内核电流提供电源。

图 3. LDO 噪声频谱密度

通常 PLL 的输出端会有四种类型的杂散:PFD 或参考杂散、小数杂散、整数边界杂散以及外部来源杂散,如电源。所有PLL 都至少有一种类型的杂散,虽然永远无法消除这些杂散。但某些情况下,在不同类型的杂散或频率之间进行取舍,可以改进整体性能。

若要避免参考杂散,请检查参考信号的上升沿。边沿过快或边沿幅度过大都会对频域造成严重的谐波现象。另外,仔细检查PCB 布局,避免输入和输出之间产生串扰。如需最大程度地减少小数杂散,可增加扰动,迫使小数杂散进入本底噪声中,但这样做会略为增加本底噪声。

整数边界杂散不常见,且仅当输出频率过于接近参考频率的整数倍时才会发生,此时环路滤波器无法将其滤除。解决该问题的简便方法是重新调节参考频率方案。例如,若边界杂散发生在 1100 MHz 处,且输出为 1100.1 MHz,参考输入为 20 MHz,则使用 100 kHz 环路滤波器将参考频率改为 30 MHz 即可消除该杂散。

结论

调试 PLL 要求对 PLL 具有深入的理解,并且如果在设计阶段格外仔细,就能避免很多问题。若问题发生在调试阶段,请遵循本文所述之建议,对问题逐一进行分析并逐步解决问题。

审核编辑:何安

-

protel输出高质量gerber2011-12-12 26320

-

高质量C编程指南—林锐2012-08-03 2929

-

高质量C++、C编程指南2012-08-06 5103

-

高质量C&C++2012-08-16 2744

-

高质量C++&C 编程指南2012-08-19 2499

-

原版PIC实战项目-C(高质量PDF版本)2013-07-10 13767

-

高质量C语言编程2013-07-22 13926

-

编写高质量C语言代码2013-07-31 4738

-

林锐《高质量C语言编程》2013-08-17 2452

-

高质量C++与C编程指南2014-03-09 5441

-

高质量编程2016-02-27 7211

-

图书推荐:高质量C++编程指南2016-06-12 2319

-

【下载】高质量干货-22本高质量EMC电磁兼容性设计资料2020-03-20 5910

-

请问怎么才能设计出高质量的印制线路板?2021-04-23 1517

全部0条评论

快来发表一下你的评论吧 !