造时工艺不成熟5nm 芯片集体 “翻车”,从 7nm 到 5nm 的尴尬

电子说

描述

从 2020 年下半年开始,各家手机芯片厂商就开始了激烈的 5nm 芯片角逐,苹果、华为、高通、三星相继推出旗舰级 5nm 移动处理器,并宣称无论是在性能上还是在功耗上都有着优秀的表现。

不过从这几款 5nm 芯片的实际表现来看,一些用户并不买账,认为 5nm 手机芯片表现并没有达到预期,5nm 芯片似乎遭遇了一场集体 “翻车”。

5nm 芯片集体 “翻车”,从 7nm 到 5nm 的尴尬

最早商用的 5nm 芯片是去年 10 月份 iPhone12 系列手机搭载的 A14 仿生芯片,这款芯片晶体管达到 118 亿个,比 A13 多出近 40%,且 6 核 CPU 和 4 核 GPU 使其 CPU 性能提升 40%,图形性能提升 30%,功耗降低 30%。

紧接着华为发布麒麟 9000,集成 153 亿个晶体管,8 核 CPU、24 核 GPU 和 NPU AI 处理器,官方称其 CPU 性能提升 25% ,GPU 提升 50%。

到了十二月份,高通和三星又相继发布了由三星代工的骁龙 888 和 Exynos 1080,同样声称性能有较大提升,功耗下降。

最先被爆出疑似 “翻车”的是 A14。

据外媒 9to5Mac 报道,部分 iPhone 12 用户在使用手机时遇到了高耗电问题,待机一夜电量下降 20% 至 40%,无论是在白天还是晚上,无论有没有开启更多的后台程序,结果依旧如此。

最广为用户诟病的还属骁龙 888。

在首批使用者的测试中,不少数码评测博主都指出首发骁龙 888 的小米 11 性能提升有限,功耗直接上升。有人将此归结于骁龙 888 的代工厂三星的 5nm 工艺制程的不成熟,由此以来三星自己的两款 5nm 芯片也面临 “翻车”风险。

如果按照摩尔定律,芯片的晶体管数量每隔 18 个月翻一番,性能也将提升一倍,但晶体管的微缩越来越难,如今在从 7nm 到 5nm 的推进中,手机芯片的表现似乎并不尽人意,不仅在性能提升方面受限,功耗也 “翻车”,面临先进制程性价比上的尴尬。

为何 5nm 芯片频频翻车?当芯片工艺制程越先进时,性能与功耗究竟如何变化?

设计时性能优先,制造时工艺不成熟

集成电路的功耗可以分为动态功耗和静态功耗。

动态功耗通俗易懂,指的是电路状态变化时产生的功耗,计算方法与普通电路类似,依据物理公式 P=UI,动态功耗受到电压和电流的影响。

静态功耗即每个 MOS 管泄露电流产生的功耗,尽管每个 MOS 管产生的漏电流很小,但由于一颗芯片往往集成上亿甚至上百亿的晶体管,从而导致芯片整体的静态功耗较大。

在芯片工艺制程发展过程中,当工艺制程还不太先进时,动态功耗占比大,业界通过放弃最初的 5V 固定电压的设计模式,采用等比降压减慢功耗的增长速度。

不过,电压减小同样意味着晶体管的开关会变慢,部分更加注重性能的厂商,即便是采用更先进的工艺也依然保持 5V 供电电压,最终导致功耗增大。

随着工艺节点的进步,静态功耗的重要性逐渐显现。从英特尔和 IBM 的芯片工艺发展中可以看出,在工艺制程从 180nm 到 45nm 的演进过程中,晶体管集成度增速不同,动态功耗或增加或减少,但静态功耗一直呈上升趋势,45nm 时,静态功耗几乎与动态功耗持平。

尽管一些设计厂商宁愿在降低功耗上做出牺牲也要提升性能,但也不得不面对高功耗带来的负面影响。

对于用户而言,设备发热严重以及耗电严重是高功耗带来的直接影响,如果芯片散热不好,严重时会导致芯片异常甚至失效。

因此,行业内依然将低功耗设计视为芯片行业需要解决的问题之一,如何平衡先进节点下芯片的性能、功耗与面积(PPA),也是芯片设计与制造的挑战。

从理论上而言,芯片制程越先进,更低的供电电压产生更低的动态功耗,随着工艺尺寸进一步减小,已下降到 0.13V 的芯片电压难以进一步下降,以至于近几年工艺尺寸进一步减小时,动态功耗基本无法进一步下降。

在静态功耗方面,场效应管的沟道寄生电阻随节点进步而变小,在电流不变的情况下,单个场效应管的功率也变小。但另一方面,单位面积内晶体管数目倍速增长又提升静态功耗,因此最终单位面积内的静态功耗可能保持不变。

厂商为追求更低的成本,用更小面积的芯片承载更多的晶体管,看似是达成了制程越先进,芯片性能越好,功耗越低。但实际情况往往复杂得多,为提升芯片整体性能,有人增加核心,有人设计更复杂的电路,随之而来的是更多的路径刺激功耗增长,又需要新的方法来平衡功耗。

对芯片行业影响重大的 FinFET 就是平衡芯片性能与功耗的方法之一,通过类似于鱼鳍式的架构控制电路的连接和断开,改善电路控制并减少漏电流,晶体管的沟道也随之大幅度缩短,静态功耗随之降低。

不过,从 7nm 演进到 5nm 则更为复杂。

Moortec 首席技术官 Oliver King 曾接受外媒体采访时称:“当我们升级到 16nm 或 14nm 时,处理器速度有了很大的提高,而且漏电流也下降得比较快,以至于我们在使用处理器时能够用有限的电量做更多的事情。不过当从 7nm 到 5nm 的过程中,漏电情况又变得严重,几乎与 28nm 水平相同,现在我们不得不去平衡他们。”

Cadence 的数字和签准组高级产品管理总监 Kam Kittrell 也曾表示,“很多人都没有弄清能够消耗如此多电能的东西,他们需要提前获取工作负载的信息才能优化动态功耗。长期以来,我们一直专注于静态功耗,以至于一旦切换到 FinFET 节点时,动态功耗就成为大问题。另外多核心的出现也有可能使系统过载,因此必须有更智能的解决方案。”

这是 5nm 芯片设计、制造公司共同面临的问题,因此也就能够稍微明白为何现有的几款 5nm 芯片集体 “翻车”。不成熟的设计与制造都会影响性能与功耗的最大化折中,当然也不排除芯片设计厂商为追求性能更好的芯片,而不愿花大力气降低功耗的情况。

尴尬的是,越顶尖的工艺,需要的资金投入就越大,事实上追求诸如 7nm、5nm 等先进工艺的领域并不多,如果先进的工艺无法在功耗与性能上有极大的改善,那么追求更加先进的制程似乎不再有原本的意义。

走向 3nm,真的准备好了吗?

根据市场研究机构 International Business Strategies (IBS)给出的数据显示,65nm 工艺时的设计成本只需要 0.24 亿美元,到了 28nm 工艺时需要 0.629 亿美元,7nm 和 5nm 成本急速增长,5nm 设计成本达到 4.76 亿美元。

同时,根据乔治敦大学沃尔什外交学院安全与新兴技术中心(CSET)的两位作者编写的一份题为《AI Chips: What They Are and Why They Matter》的报告,作者借助模型预估得出台积电每片 5nm 晶圆的收费可能约为 17,000 美元,是 7nm 的近两倍。

在估算的模型中,作者估算出每颗 5nm 芯片需要 238 美元的制造成本,108 美元的设计成本以及 80 美元的封装和测试成本。这使得芯片设计公司将为每颗 5nm 芯片支付高到 426 美元(约 2939 元)的总成本金额。

这意味着,无论是芯片设计厂商还是芯片制造厂商,遵循摩尔定律发展到 5nm 及以下的先进制程,除了需要打破技术上的瓶颈,还需要有巨大的资本作为支撑,熬过研发周期和测试周期,为市场提供功耗和性能均有改善的芯片最终进入回报期。

因此,并不是业界所有人都对 5nm 芯片的推进持积极乐观的态度。芯片 IP 供应商 Kandou 的首席执行官 Amin Shokrollahi 曾在接受外媒采访时表示:“对我们而言,从 7nm 到 5nm 是令人讨厌的,电路不会按比例缩放,而且需要很多费用,我们没有看到这其中的优势。但是客户希望我们这样做,所以我们不得不这样做。”

还有全球第二大芯片代工厂 Global Foundries 出于经济考虑,于 2018 年宣布搁置 7nm 项目,将资源回归 12nm/14nm 上。就连实力强大的英特尔也在 10nm、7nm 的研发过程中多次受阻。

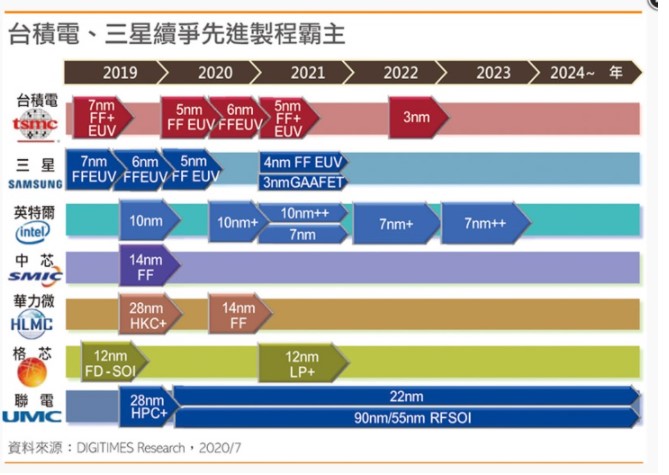

不过,这依然无法阻止各家手机芯片设计厂商在先进制程上的竞争,更无法阻止三星和台积电之间的制程霸主争夺。

此前雷 锋网报道过,在先进制程的芯片制造方面,三星视台积电为最大的竞争对手,三星在同台积电的竞争中,先进制程的推进断断续续,曾经为了先发制人直接从 7nm 跳到 7nm LPP EUV,二者同时在 2020 年实现 5nm FF EUV 的量产,如今又都斥巨资投入 3nm 的研发与量产中。

上周五,台积电 CEO 魏哲家在投资人会议上宣布,台积电 2021 年资本的支出将高到 250 亿至 280 亿美元,其中 80% 会使用在包括 3nm、5nm 及 7nm 的先进制程上,10% 用在高端封装及光罩作用,另外 10% 用在特殊制程上。

根据台积电 3nm 制程的进度,预计将在 2021 年试产,在 2022 年下半年进入量产,帮助英特尔代工 3nm 处理器芯片。

与此同时,三星也曾对外称其 3nm GAA 的成本可能会超过 5 亿美元,预期在 2022 年大规模生产采用比 FinFET 更为先进的 GAAFET 3nm 制程芯片。

回归到 5nm 移动处理器的实际情况,无论是出自哪家厂商的设计与生产,均面临性能和功耗方面的问题,5nm 芯片似乎还未成熟,3nm 量产就要今年开始试产。越来越趋于摩尔定律极限的 3nm,真的准备好了吗?

责任编辑:PSY

-

第1集|彻底绕过光刻机,“雕版印刷术”也能搞定5nm芯片? #芯片 #5nm工艺 #硬声创作季Hello,World! 2022-10-05

-

7nm芯片和5nm芯片哪个好2022-07-05 25560

-

5nm芯片是什么意思 哪些芯片是5nm2022-06-29 31926

-

从7nm到5nm,半导体制程 精选资料分享2021-07-29 8380

-

5nm手机芯片功耗过高?2021-02-04 5445

-

汽车芯片真的进入了5nm时代吗2021-02-03 8181

-

如何看待5nm芯片集体翻车?2021-01-27 3157

-

5nm芯片翻车,联发科成赢家2021-01-25 2531

-

台积电5nm、7nm订单爆棚2021-01-12 2643

-

消息称台积电5nm、7nm订单多,苹果、AMD备货曝光2020-12-02 2321

-

三星预计6月底完成5nm EUV生产线 且最快在今年底开始生产5nm工艺2020-03-13 3440

-

全球进入5nm时代2020-03-09 3644

全部0条评论

快来发表一下你的评论吧 !