PCB Layout设计的一些规范

描述

1、主要目的

1.1、规范PCB的设计流程。

1.2、保证PCB设计质量和提高设计效率。

1.3、提高PCB设计的可生产性、可测试性、可维护性。

2、适用范围

适用于所有PCB设计人员。

3、PCB设计前准备

3.1、准确无误的原理图包括电子档和书面说明文件。

3.2、正式BOM表。对于封装库中没有的元件硬件工程师应提供元件的数据资料或实物,并指定引脚的定义顺序。

3.3、提供PCB大致布局图或重要单元、核心电路摆放位置。提供PCB结构图,应标明PCB外形、安装孔、定位元件、禁布区等相关信息。

3.4、要求说明

3.4.1、设计要求说明

a)标明1A以上大电流元件、网络。

b)标明模拟小信号等易被干扰信号。

c)标明重要的时钟信号、差分信号以及高速数字信号。

d)标明其它特殊要求的信号。

e)标明强电弱电电路。

3.4.2、PCB特殊要求说明:

a)差分布线、需屏蔽网络、特性阻抗网络、等延时网络等。

b)特殊元件的禁止布线区、锡膏偏移、阻焊开窗以及其它结构的特殊要求。

3.5、仔细阅读原理图,了解电路架构,理解电路的工作条件。

3.6、与硬件工程师充分交流的基础上,确认PCB中关键的网络,了解特殊元件的设计要求。

4、设计流程

4.1、创建网络表

4.1.1.网络表是原理图与PCB的接口文件,PCB设计人员应根据所用的原理图和PCB设计工具的特性,选用正确的网络表格式,创建符合要求的网络表。

4.1.2.创建网络表的过程中,应根据原理图设计工具的特性,积极协助原理图设计者排除错误。保证网络表的正确性和完整性。

4.1.3.确定器件的封装(PCB FOOTPRINT

4.2、建立PCB板框

4.2.1.根据PCB结构图,或相应的模板建立PCB文件,包括安装孔、禁布区等相关信息。

4.2.2.尺寸标注。在钻孔层中应标明PCB的精确外形尺寸,且不可以形成封闭尺寸标注。

4.3、载入网络表

载入网表并排除所有载入问题,直到没有任何错误信息提示,才可以确认载入无误。

4.4、设置规则

关于设计规则(Design Rules)设置的详细说明,可参考有关PROTEL的使用说明。对于一般设置,可采用PROTEL默认设置即可。关于最小线宽、最小间隙、最小孔径等参数的设置,与PCB板的加工厂家的加工水平有关,设计人员必须了解PCB加工商常用的推荐设置如下:

4.4.1.布线层设置:有特殊要求的,经过批准可以采用4层板,一般情况尽量使用双面板。相邻布线层的走线方向应该相互垂直。

4.4.2.布局格点设置:推荐50mil;

4.4.3.布线格点设置:推荐25mil;

4.4.4.最小线宽设置:一般电路推荐12mil,密度较高的电路推荐10mil,不小于7mil;

4.4.5.最小间隙设置:一般电路推荐12mil,密度较高的电路推荐10mil,不小于7mil;

4.4.6.焊盘设置:焊盘设计要考虑到两个方面因素:首先要考虑可加工性,方便元件插装及焊接;其次要考虑焊盘强度,防止焊盘受热受力脱落。一般元件焊盘,推荐外径:62mil,不小于50mil;推荐孔径:32mil;特殊元件焊盘,根据元件引脚的实际大小设定,以元件引脚方便插入为原则。

4.4.7.过孔设置:一般电路推荐外径:40mil,推荐孔径:28mil。

4.5、元件布局

4.5.1.首先要确定参考点。

一般参考点都设置在左边和底边的边框线的交点(或延长线的交点)上或印制板的插件的第一个焊盘。

4.5.2.一但参考点确定以后,元件布局、布线均以此参考点为准,布局推荐使用25MIL网格。

4.5.3.根据要求先将所有有定位要求的元件固定并锁定。

4.5.4.布局的基本原则

a)布局的首要原则是保证布线的布通率,移动器件时注意飞线的连接,把有连线关系的器件放在一起,总的连线尽可能的短,关键信号线最短。

b)遵循先难后易、先大后小的原则。

c)放置器件时要考虑以后的焊接,不要太密集。

d)强信号、弱信号要完全分开。

e)高压元件和低压元件间隔要充分。

f)高频元件间隔要充分。

g)数字器件和模拟器件要分开,尽量远离。

4.5.5相同结构电路部分应尽可能采取对称布局。

4.5.6按照均匀分布、重心平衡、版面美观的标准来优化布局。

4.5.7同类型的元件应该在X或Y方向上一致。同一类型的有极性(方向性)分立元件也要力争在X或Y方向上一致,以便于生产和调试。

4.5.8元件的放置要便于调试和维修,大元件边上不能放置小元件,需要调试的元件周围应有足够的空间,发热元件应有足够的空间以利于散热,热敏元件应远离发热元件。

4.5.9双列直插元件相互的距离要大于80mil;BGA与相临元件距离大于200mil;阻容等贴片小元件相互距离大于30mil;贴片元件焊盘外侧与相临插装元件焊盘外侧要大于80mil;压接元件周围200mil不可以放置插装元器件;焊接面周围200mil内不可以放置贴装元件。

4.5.10集成电路的去耦电容应尽量靠近芯片的电源脚、高频最靠近为原则。使之与电源和地之间形成回路最短。

4.5.11旁路电容应均匀分布在集成电路周围。

4.5.12元件布局时,使用同一种电源的元件应考虑尽量放在一起,以便于将来的电源分割。

4.5.13.调整字符。

所有字符不可以覆盖焊盘,也不可以放在元件下方,要保证装配以后还可以清晰看到字符信息。所有字符在X或Y方向上应一致。字符、丝印大小要统一。推荐字符高度60mil,字符线宽8mil。

4.5.14.放置PCB的MARK点。

4.6、布线

4.6.1布线优先次序

关键信号线优先:电源、模拟小信号、高速信号、时钟信号和同步信号等关键信号优先布线。

密度优先原则:从电路板上连接关系最复杂的器件着手布线。从电路板连线最密集的区域开始布线。

4.6.2自动布线

在布线质量满足设计要求的情况下,可使用自动布线器以提高工作效率,在自动布线前为了更好地控制布线质量,一般在运行前要详细定义布线规则,这些规则可以在软件的图形界面内进行定义。

4.6.3尽量为时钟信号、高频信号、敏感信号等关键信号提供专门的布线层,并保证其最小的回路面积。必要时应采取手工优先布线、屏蔽和加大安全间距等方法,保证信号质量。

4.6.4电源层和地层之间的EMC环境较差,应避免布置对干扰敏感的信号。

4.6.5进行PCB设计时应该遵循的规则。

a)地线回路规则:

环路最小规则,即信号线与其回路构成的环面积要尽可能小,环面积越小,对外的辐射越少,接收外界的干扰也越小。针对这一规则,在地平面分割时,要考虑到地平面与重要信号走线的分布,防止由于地平面开槽等带来的问题;在双层板设计中,在为电源留下足够空间的情况下,应该将留下的部分用参考地填充,且增加一些必要的孔,将双面地信号有效连接起来,对一些关键信号尽量采用地线隔离,对一些频率较高的设计,需特别考虑其地平面信号回路问题,建议采用多层板为宜。

b)窜扰控制

串扰(CrossTalk)是指PCB上不同网络之间因较长的平行布线引起的相互干扰,主要是由于平行线间的分布电容和分布电感的作用。克服串扰的主要措施是:

● 加大平行布线的间距,遵循3W规则。

● 在平行线间插入接地的隔离线。

● 减小布线层与地平面的距离。

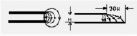

c)屏蔽保护

对应地线回路规则,实际上也是为了尽量减小信号的回路面积,多见于一些比较重要的信号,如时钟信号,同步信号;对一些特别重要,频率特别高的信号,应该考虑采用铜轴电缆屏蔽结构设计,即将所布的线上下左右用地线隔离,而且还要考虑好如何有效的让屏蔽地与实际地平面有效结合。

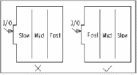

d)走线的方向控制规则:

即相邻层的走线方向成正交结构。避免将不同的信号线在相邻层走成同一方向,以减少不必要的层间窜扰;当由于板结构限制(如某些背板)难以避免出现该情况,特别是信号速率较高时,应考虑用地平面隔离各布线层,用地信号线隔离各信号线。

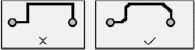

e)走线的开环检查规则:

一般不允许出现一端浮空的布线(Dangling Line),主要是为了避免产生天线效应,减少不必要的干扰辐射和接受,否则可能带来不可预知的结果。

f)走线闭环检查规则:

防止信号线在不同层间形成自环。在多层板设计中容易发生此类问题,自环将引起辐射干扰。

g)走线的分枝长度控制规则

尽量控制分枝的长度,一般的要求是Tdelay<=Trise/20。

h)走线的谐振规则:

主要针对高频信号设计而言,即布线长度不得与其波长成整数倍关系,以免产生谐振现象。

i)走线长度控制规则:

即短线规则,在设计时应该尽量让布线长度尽量短,以减少由于走线过长带来的干扰问题,特别是一些重要信号线,如时钟线,务必将其振荡器放在离器件很近的地方。对驱动多个器件的情况,应根据具体情况决定采用何种网络拓扑结构。

j)倒角规则:

PCB设计中应避免产生锐角和直角,产生不必要的辐射,同时工艺性能也不好。

k)器件去藕规则:

在印制板上增加必要的去耦电容,滤除电源上的干扰信号,使电源信号稳定。在多层板中,对去耦电容的位置一般要求不太高,但对双层板,去耦电容的布局及电源的布线方式将直接影响到整个系统的稳定性,有时甚至关系到设计的成败。

在双层板设计中,一般应该使电流先经过滤波电容滤波再供器件使用,同时还要充分考虑到由于器件产生的电源噪声对下游的器件的影响,一般来说,采用总线结构设计比较好,在设计时,还要考虑到由于传输距离过长而带来的电压跌落给器件造成的影响,必要时增加一些电源滤波环路,避免产生电位差。

在高速电路设计中,能否正确地使用去耦电容,关系到整个板的稳定性。

l)器件布局分区/分层规则:

主要是为了防止不同工作频率的模块之间的互相干扰,同时尽量缩短高频部分的布线长度。通常将高频的部分布设在接口部分以减少布线长度,当然,这样的布局仍然要考虑到低频信号可能受到的干扰。同时还要考虑到高/低频部分地平面的分割问题,通常采用将二者的地分割,再在接口处单点相接。

对混合电路,也有将模拟与数字电路分别布置在印制板的两面,分别使用不同的层布线,中间用地层隔离的方式。

m)孤立铜区控制规则:

孤立铜区的出现,将带来一些不可预知的问题,因此将孤立铜区与别的信号相接,有助于改善信号质量,通常是将孤立铜区接地或删除。在实际的制作中,PCB厂家将一些板的空置部分增加了一些铜箔,这主要是为了方便印制板加工,同时对防止印制板翘曲也有一定的作用。

n)电源与地线层的完整性规则:

对于导通孔密集的区域,要注意避免孔在电源和地层的挖空区域相互连接,形成对平面层的分割,从而破坏平面层的完整性,并进而导致信号线在地层的回路面积增大。

o)重叠电源与地线层规则:

不同电源层在空间上要避免重叠。主要是为了减少不同电源之间的干扰,特别是一些电压相差很大的电源之间,电源平面的重叠问题一定要设法避免,难以避免时可考虑中间隔地层。

p)3W规则:

为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。如要达到98%的电场不互相干扰,可使用10W的间距。

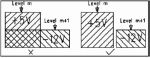

q)20H规则:

由于电源层与地层之间的电场是变化的,在板的边缘会向外辐射电磁干扰。称为边沿效应。解决的办法是将电源层内缩,使得电场只在接地层的范围内传导。以一个H(电源和地之间的介质厚度)为单位,若内缩20H则可以将70%的电场限制在接地层边沿内;内缩100H则可以将98%的电场限制在内。

4.7、设计规则检查(DRC)

设计完成,必须经过DRC检查,必须无任何错误报告才可以。

4.8、复查

PCB设计完成,自行检查无误后,根据需要可以由PCB设计者或产品硬件开发人员提出PCB设计质量的评审,如果不需要组织评审组进行设计评审,可由研发经理指定硬件工程师进行复查。自行检查或由他人复查的项目如下:

4.8.1.检查高频、高速、时钟及其他脆弱信号线,是否回路面积最小、是否远离干扰源、是否有多余的过孔和绕线、是否有垮地层分割区。

4.8.2.检查晶体、变压器、光藕、电源模块下面是否有信号线穿过,应尽量避免在其下穿线,特别是晶体下面应尽量铺设接地的铜皮。

4.8.3.检查定位孔、定位件是否与结构图一致,ICT定位孔、SMT定位光标是否加上并符合工艺要求。

4.8.4.检查器件的序号是否靠近器件摆放,并且无丝印覆盖焊盘;检查丝印的版本号是否符合版本升级规范,并标识出。

4.8.5.报告布线完成情况是否百分之百;是否有线头;是否有孤立的铜皮。

4.8.6.检查电源、地的分割正确;单点共地已作处理。

4.8.7.检查各层光绘选项正确,标注和光绘名正确;需拼板的只需钻孔层的图纸标注。

4.8.8.检查电路板编号、版本号表示是否正确。

4.8.9.检查电路板设计完成日期是否正确。

4.9、输出

经过评审或者检验合格后,将PCB文件、PCB说明文档以及制板要求(板厚、数量、周期以及特殊要求等)发给研发助理,由研发助理发给制板厂家制作电路板。

审核编辑:何安

-

pcb check list(PCB layout 检查列表)公司规范2008-06-03 12655

-

PCB Layout的一些总结2016-12-20 4555

-

PCB Layout设计规范分享2021-01-25 5087

-

PCB Layout的100+技术规范分享2021-03-02 1665

-

分享设计pcb layout的一些经验2021-04-23 1615

-

PCB layout时需要注意的一些细节记录2023-04-25 1203

-

PCB LAYOUT设计规范手册2010-11-01 2639

-

PCB布板一些简易常用规则2009-11-21 6944

-

pcb layout基础学习2011-11-21 18312

-

PCB Layout设计中的一些设计原则总结2019-04-26 1979

-

PCB Layout设计规范你了解多少2019-08-19 13088

-

PCB Layout设计规范有哪一些2019-08-20 5773

-

PCB Layout设计规范电子版下载2021-07-18 2407

-

一些与众不同的PCB布线经验规则2021-11-01 3891

-

PCB layout在布线上的设计规范有哪些?2024-02-23 1907

全部0条评论

快来发表一下你的评论吧 !