正则表达式在Vivado约束文件中的应用

描述

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/yinyeyy/article/details/106422415

使用xdc文件进行管脚、位置、时序和属性等约束的时候,经常会使用各种get命令。Vivado提供了很丰富的匹配表达式,比如等于==、不等于!=、匹配=~、不匹配!~、、=等等,这些表达式可以通过&&和||进行组合;同时还有大量的状态、属性和单元名称可用,比如DIRECTION、IN、IS_LOC_FIXED、IS_PRIMITIVE、NAME等等。

我在xdc文件中匹配目标的时候,在可行的情况下更倾向于使用正则表达式。本文就介绍一下我常使用的正则表达式和一些在Vivado中应用的特殊之处,同时也有个别自己尚未解决的问题。

1. -hierarchical和-regexp的使用

在匹配FPGA内部资源时,比如get_pins、get_cells、get_nets的时候,需要同时使用-hierarchical和-regexp。

-hierarchical表示Vivado在匹配对象的时候,将在工程中不同的层次内对该信号进行搜索。如果没有加这个选项,就必须在匹配字符中显式且精确的指出匹配对象所在的层次。需要注意的是,当使用get_ports时,不能使用-hierarchical选项。因为ports应该位于顶层,没有层次之分。

-regexp是指本次匹配将使用正则表达式,是必须使用的。

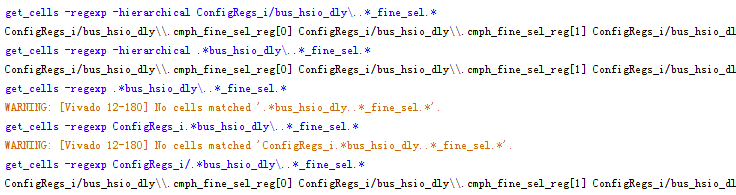

以下是一个使用-hierarchical的例子和注意事项。

首先看第一行蓝色的get_cells命令,这里用来获得ConfigRegs_i这个实例内的满足bus_hsio_dly/。.*_fine_sel.*要求的对象。可以看到运行该命令后得到了下面黑色部分的对象。第三行指令在第一行的基础上,把顶层实例ConfigRegs_i的限制去掉,也获得了想要的对象。

再来看第五行的指令。此处去掉了-hierarchical,意味着匹配过程不能穿越不同的层次结构。同时“.*”虽然可以匹配任何除换行符之外的任何数量的字符,但是却不能替代在Vivado中表示层次概念的“/”符号。所以匹配过程只在顶层进行搜索,其结果就如第六行,不能找到所需的对象。

第七行也犯了一样的错误。在没有使用-hierarchical的情况下,虽然想通过“ConfigRegs_i.*”来匹配顶层的ConfigRegs_i实例,但是“.*”是不能匹配层次符号“/”的。同样无法获取对象。

第九行虽然没有使用-hierarchical,但是通过ConfigRegs_i/指定了对象的层次结构,是可以获得想要的对象的。但是这里有一个限制,即cmph_fine_sel_reg[0]这些对象必须位于ConfigRegs_i下。如果cmph_fine_sel_reg[0]和ConfigRegs_i中间还隔了别的实例,比如ConfigRegs_i例化了CmpDef_i,CmpDef_i内部定义了cmph_fine_sel_reg[0]。这种情况下,第九行是无法找到所需对象的。

2. 常用的匹配方法

正则表达式功能强大且复杂,要完全掌握会花费很长时间。但是对于我们编写xdc而言,只需要掌握很小一部分内容就可以应对绝大多数情况了。最常用的应该就是特殊字符和限定符了。下面是比较常用的特殊字符。

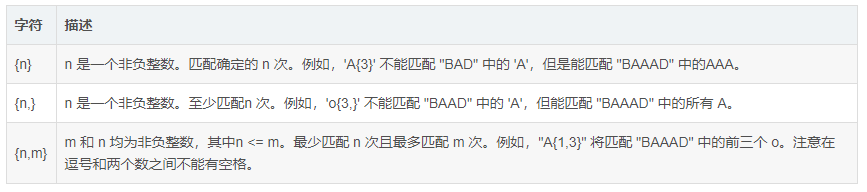

常用限定符如下。

我们在FPGA工程中使用正则表达式不是为了进行字符处理,不需要考虑太多的容错性和可能性。对于我们而言,绝大多数命名都是确定的,使用正则是为了更方便的获取对象和简化匹配过程。

3. 使用示例

3.1 获取总线类对象

看以下例子。在进行物理约束的时候,为一个总线设置信号类型,如果一个一个的写即慢又可能犯错。使用正则可以将这类信号全部提取出来。以一个从0到31共32路的总线为例。

set_property IOSTANDARD SSTL18_I_DCI [get_ports -regexp {c2c_sync/[.*]}]

以上指令可以获取所有名字为c2c_sync[]的端口,方括号内可能是任意多个数字。这种写法不够准确,在文字处理程序里面会出大问题,但是在FPGA工程中足够了。当然也可以写的稍微严格点,比如:

set_property IOSTANDARD SSTL18_I_DCI [get_ports -regexp {c2c_sync/[[0-9]{1,2}]}]

这个表达式比上一个更进一步的约束了中括号内的内容。这里的/[是为了匹配“[”本身,而里面的[0-9]则定义了一个从数字0到数字9的字符集,[0-9]后面的{1,2}则表示[0-9]中的任意数字将出现1次,或以任意两个数字的组合出现1次。对于我们的应用,做到这一步就够了。

3.2 简化匹配表达式

工程中会有一些名字很特殊的信号,比如全局复位信号,这种信号在工程中往往只会出现一次,我用更加简单粗暴的方式来获得。

set_false_path -from [get_cells -regexp -hierarchical .*rst_global_reg.*]

比如上面的例子。通过使用-hierarchical搜索所有层次,通过在rst_global_reg的前后都使用.*来匹配任何可能出现的字符。其中。表示匹配任何非换行符的字符,*表示。可以出现任意次。当然并不推荐这种写法,因为会增加编译时匹配对象的负担。可以使用更精准的匹配。

对于层次很深的信号,只要保证列出的匹配字符能够找到我们所要的对象即可。比如某工程有下图的层次结构。

比如设计者发现A_i0模块内部的D_i0内的某个关键信号的位置需要优化,且设计者知道该信号在D_i0中唯一。为了拿到这个关键信号,可以使用正则表达式,并且可以略过中间层次的所有模块。

get_cells -regexp -hierarchical {A_i0/.*/D_i0/start_reg}

3.3 特殊字符的获取

前面提到过一些特殊字符,比如?、。、/、[等等,如果需要匹配这些字符,需要用到转义符“/”。比如“/。”表示“。”这个字符本身,而不再是匹配符。。

比如在上文提到的get_ports -regexp {c2c_sync/[[0-9]{1,2}]}。这个总线的完整名称是c2c_sync[0]、c2c_sync[1]。..。..,此处的“/[”就是表示左方括号这个字符本身。而[0-9]中单独使用的[]就表示一个字符集合。这里有个需要注意的地方,作为字符使用的左方括号左侧加了转义符“/“,而右方括号则不需要加”/“。

另外一个需要注意的是上文中提到的get_cells -regexp -hierarchical ConfigRegs_i/bus_hsio_dly.*_fine_sel.*。这里面bus_hsio_dly是一个systemverilog中的interface,获取的对象是bus_hsio_dly接口中的cmph_fine_sel_reg信号,其表达方式应该是bus_hsio_dly.cmph_fine_sel_reg。此处我使用”.*“来匹配任何非换行字符,所以可以匹配”。“字符。

更合适一点的匹配表达式应该是ConfigRegs_i/bus_hsio_dly/。.*_fine_sel_reg。第一处修改是明确使用/。来匹配”。“,第二处修改时添加了_reg后缀(Vivado会给寄存器变量默认添加_reg后缀)。如果不添加该后缀,可能会获取一些不期望的对象。比如使用get_cells时,可能或获取带_fine_sel的LUT,比如_fine_sel_i_1等等。

再进一步,我们可能注意到上述匹配获得的对象打印出来是:

bus_hsio_dly//.cmph_fine_sel_reg

打印结果不是/。,而是//。。对于这种情况,我猜想是//用来表示转义符”/“。而”//“表示的转义符则作用于特殊字符”。“,用来表示普通字符”。“。

这是个人猜测,但是为什么会这样?如果哪位清楚原因,不吝赐教。

审核编辑:何安

-

shell正则表达式学习2015-07-25 2867

-

正则表达式在Vivado约束文件中的应用2021-01-26 2234

-

深入浅出boost正则表达式2010-09-08 566

-

精通正则表达式2016-05-16 823

-

关于java正则表达式的用法详解2017-09-27 653

-

快速入门IPv6和正则表达式2018-03-30 10175

-

Python正则表达式的学习指南2020-09-15 1141

-

正则表达式在Vivado约束文件(xdc)中的应用(转)2021-02-23 1769

-

Python正则表达式指南2021-03-26 1033

-

python正则表达式中的常用函数2022-03-18 2555

-

Linux入门之正则表达式2023-05-12 1992

-

shell脚本基础:正则表达式grep2023-05-29 2411

-

Python中的正则表达式2023-06-21 1867

-

什么是正则表达式?正则表达式如何工作?哪些语法规则适用正则表达式?2023-11-03 6280

-

linux正则表达式匹配字符串2023-11-23 1826

全部0条评论

快来发表一下你的评论吧 !