Vitis IDE入门helloworld程序

FPGA/ASIC技术

描述

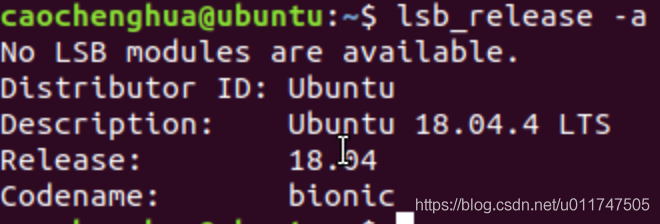

操作系统:Ubuntu 18.04.4 LTS

命令lsb_release -a

安装Vitis

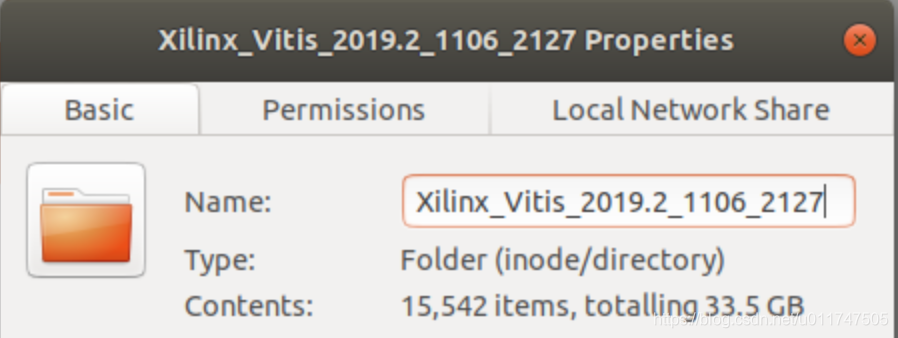

在线安装网速很慢,离线下载安装包,Xilinx_Vitis_2019.2_1106_2127.tar 30.76GB

解压缩

tar xvf Xilinx_Vitis_2019.2_1106_2127.tar

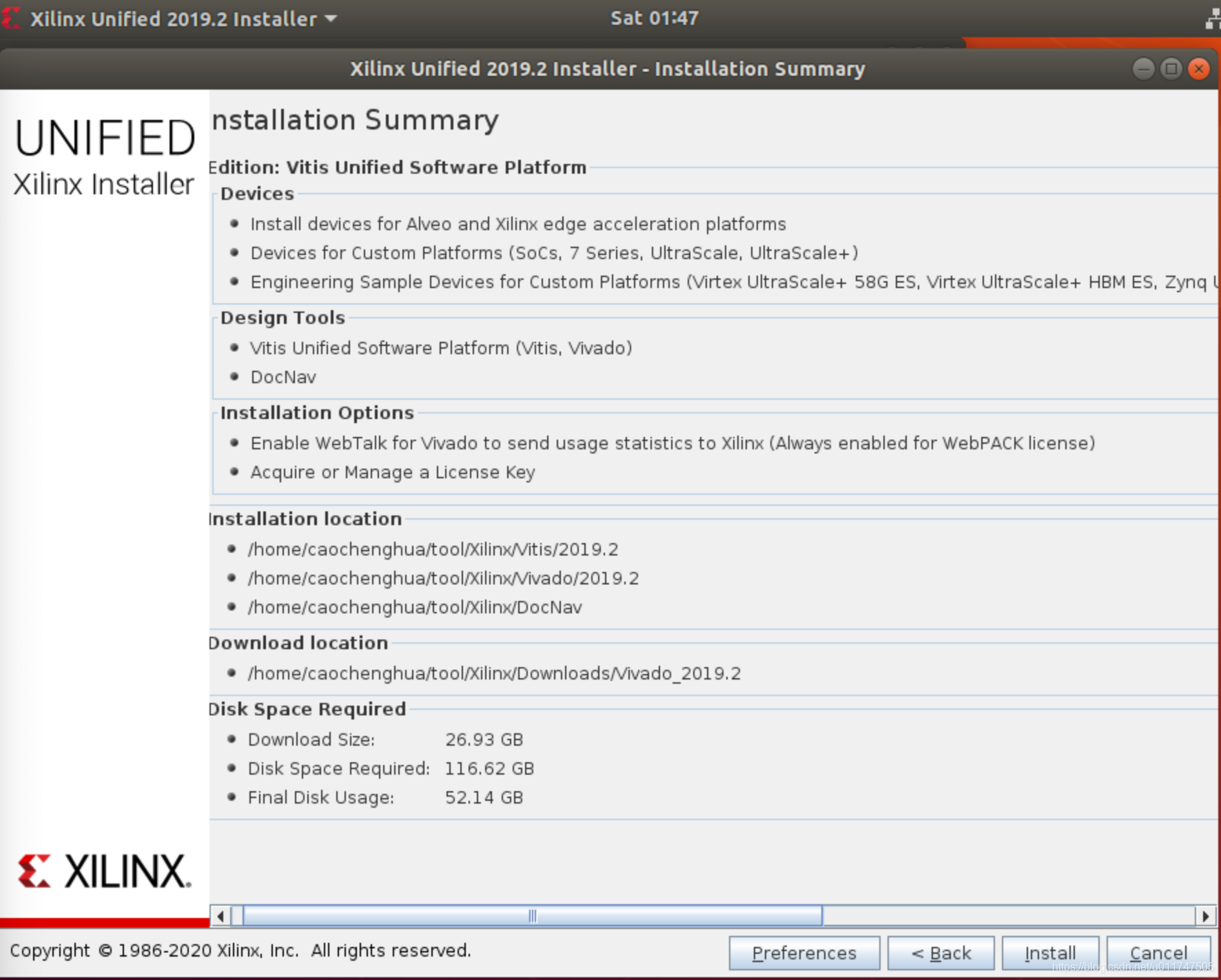

安装,需要至少120G磁盘空间,最好150G以上

cd Xilinx_Vitis_2019.2_1106_2127/

./xsetup

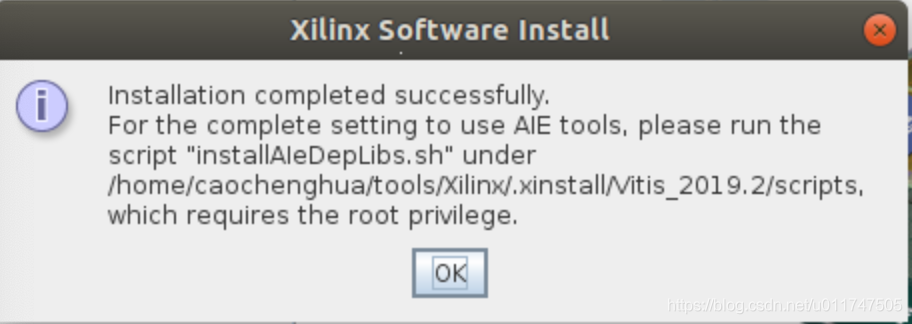

安装完成

安装petalinux

略

进入正题

首先打开Vivado 2019.2,File->New Project

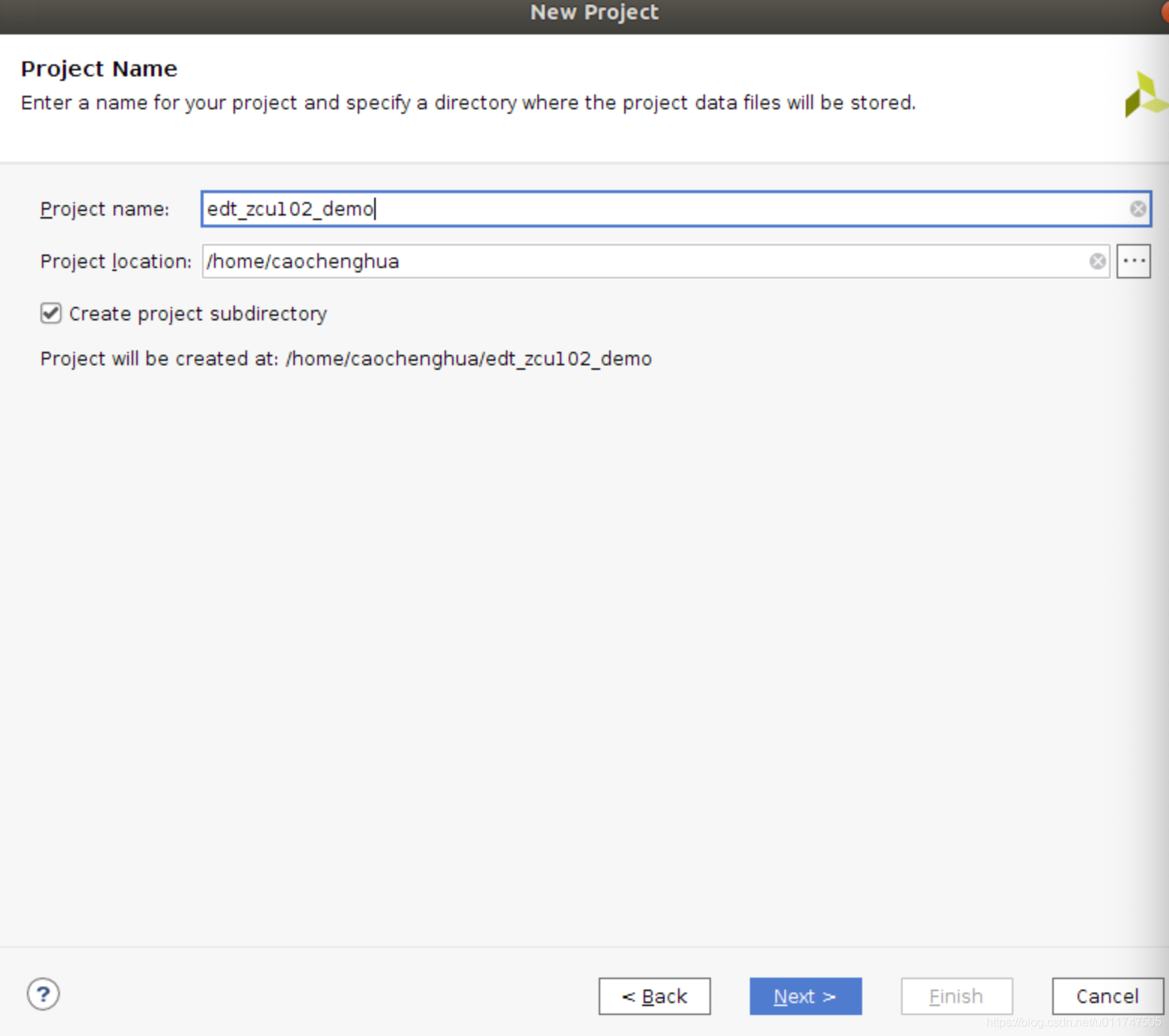

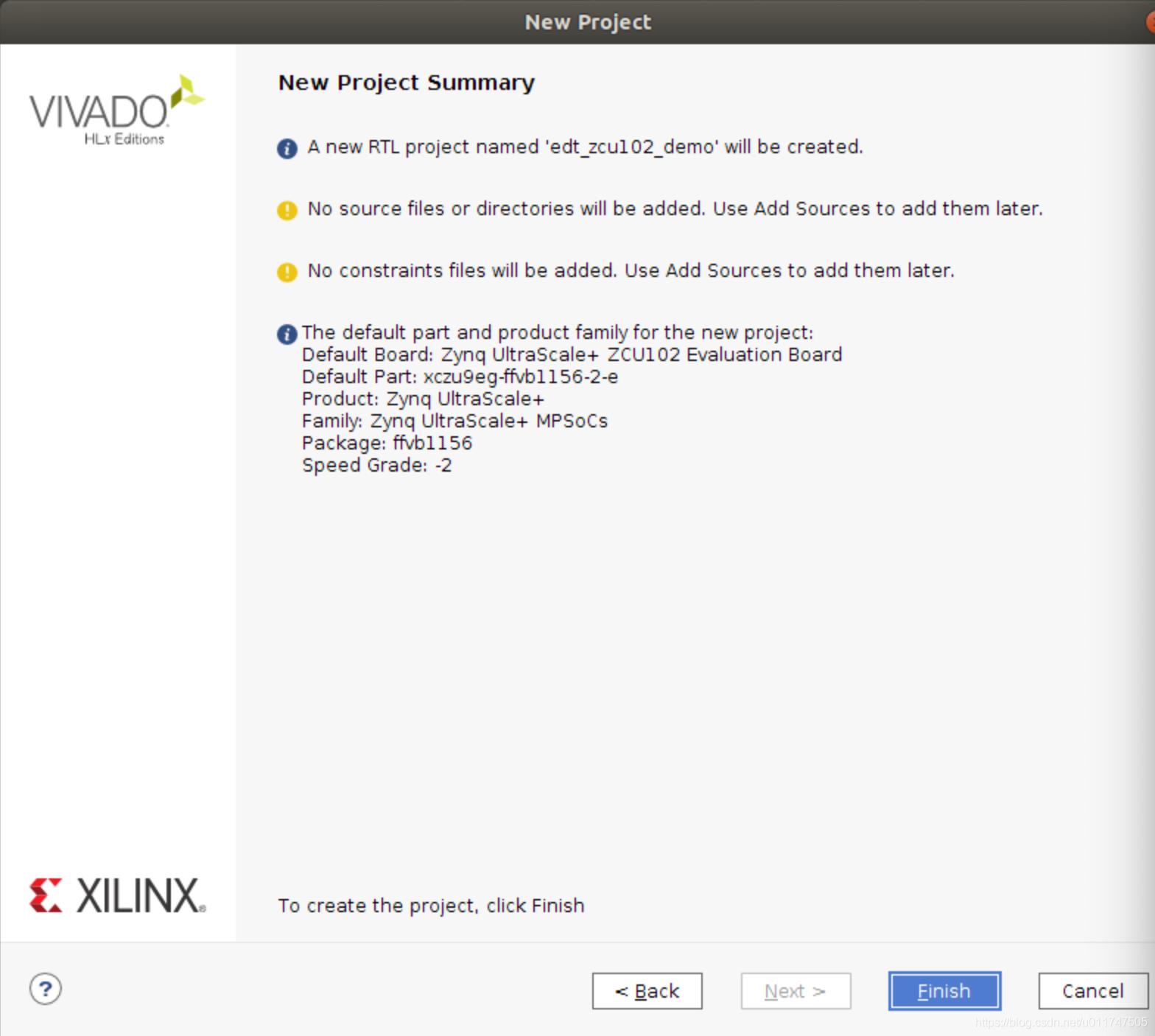

Next,项目名称edt_zcu102_demo

默认

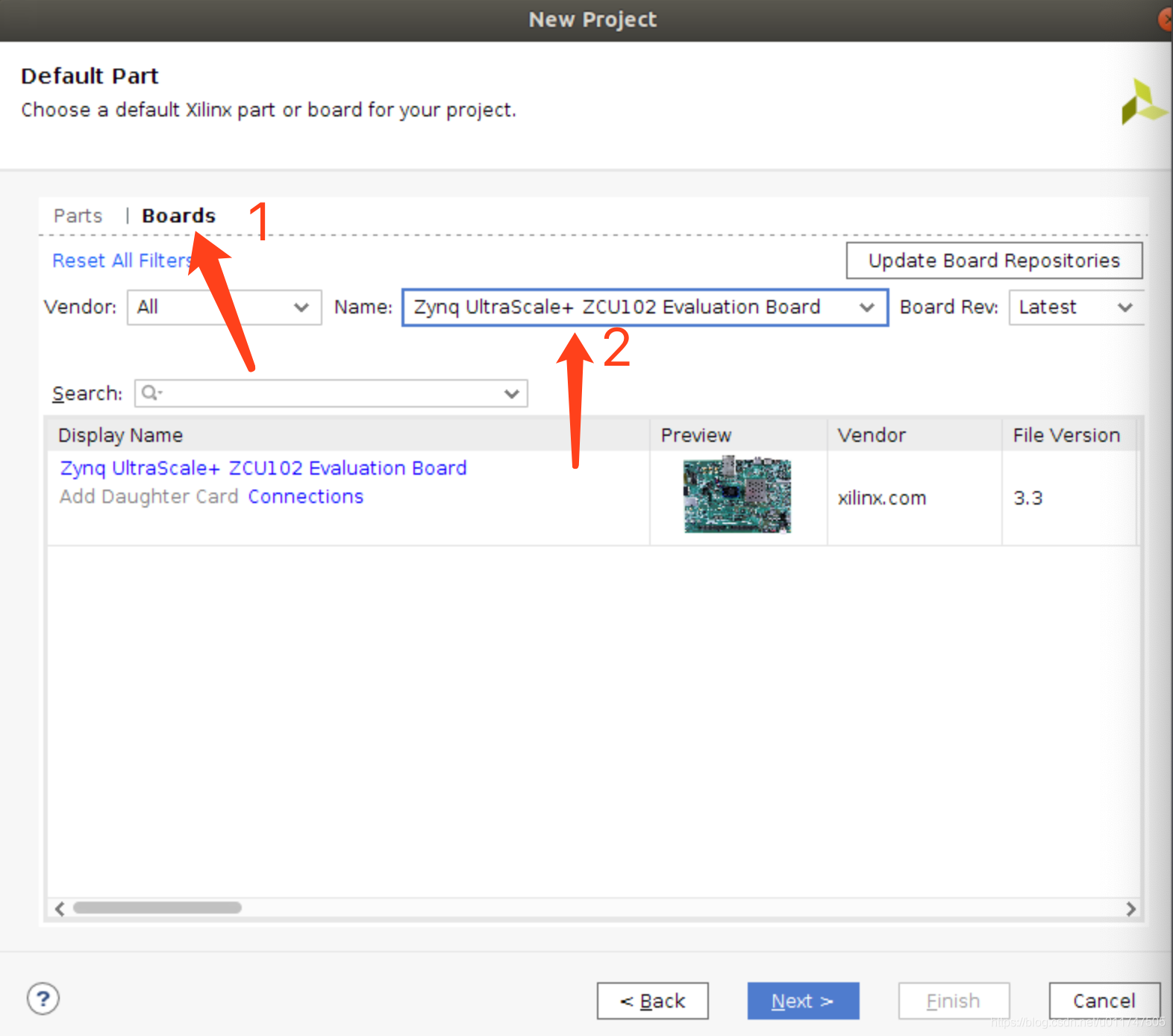

接下来的两个界面Add Sources和Add Constraints都直接Next,然后选择Boards,选择ZCU102,Next

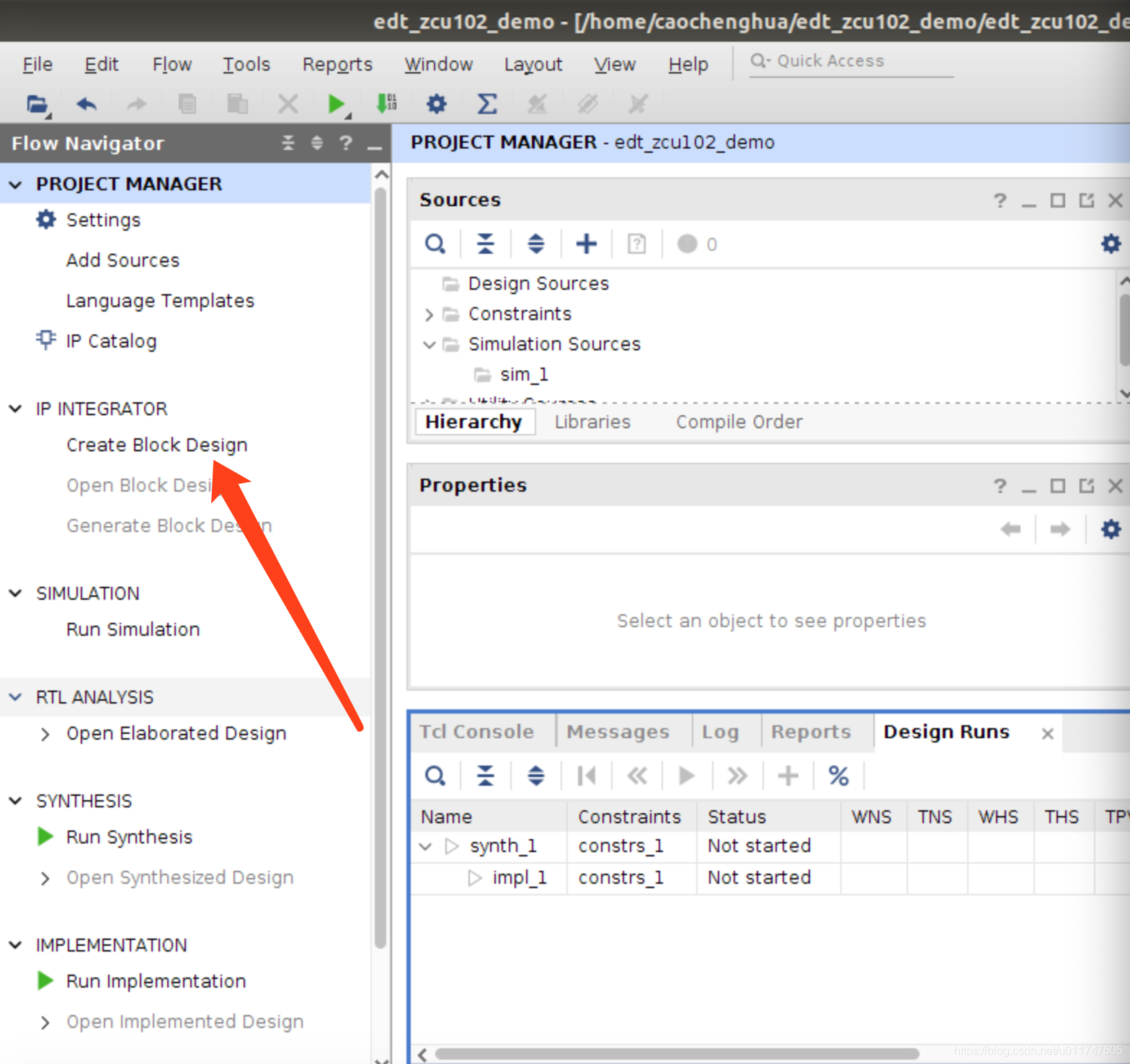

Finish,之后项目自动打开,点Create Block Design

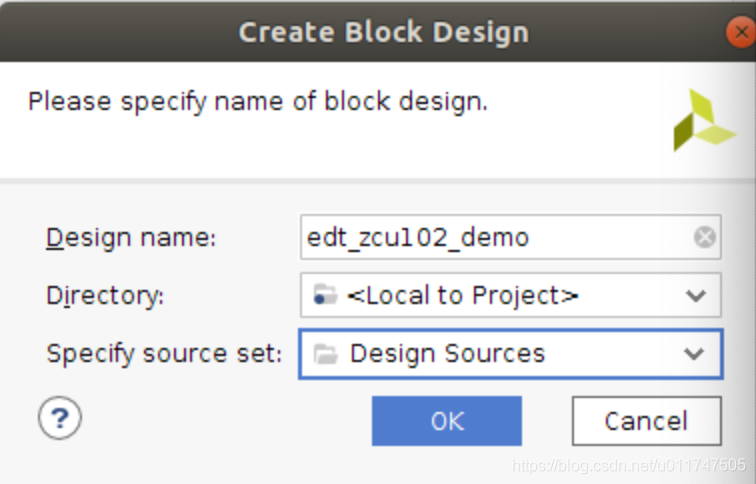

设计名称edt_zcu102_demo,然后OK

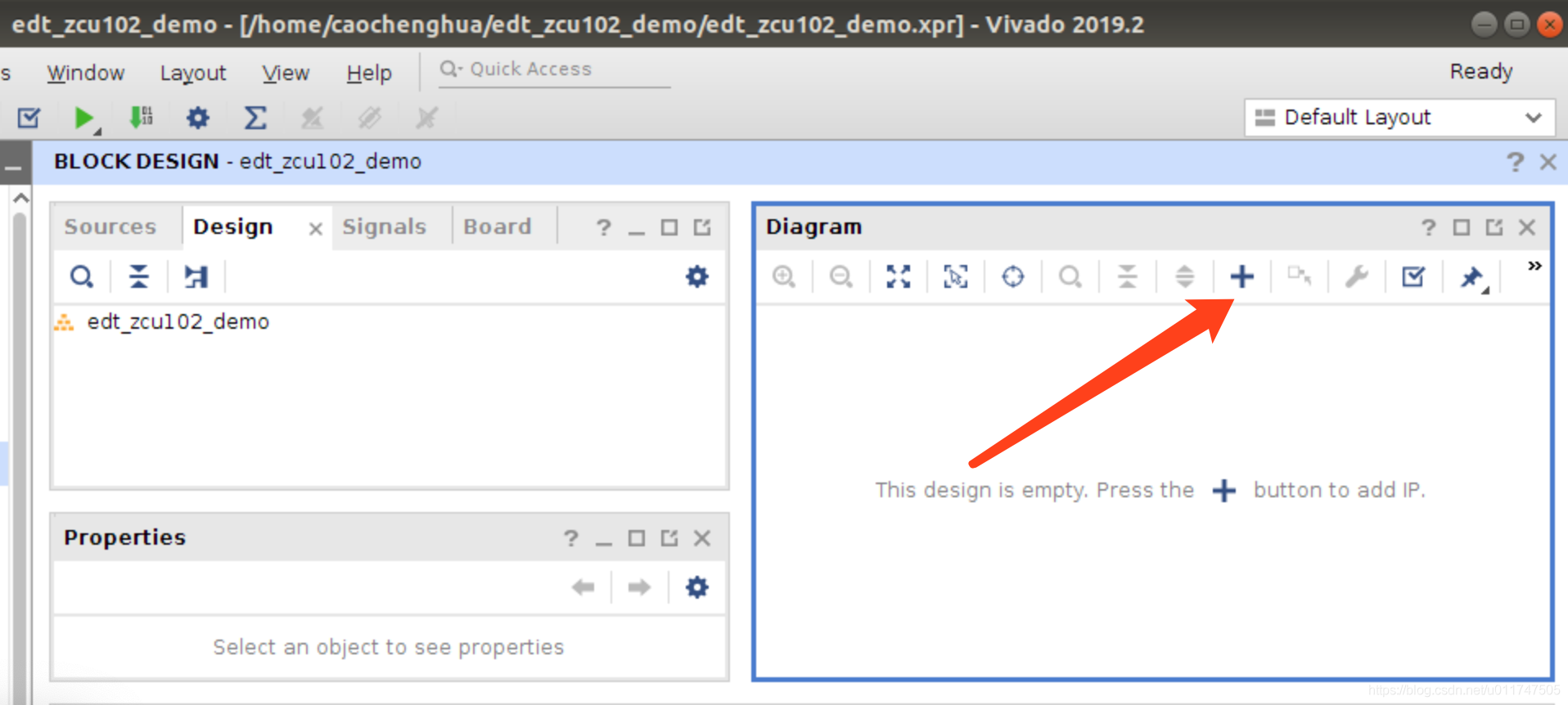

Add IP,如下图红色箭头所示

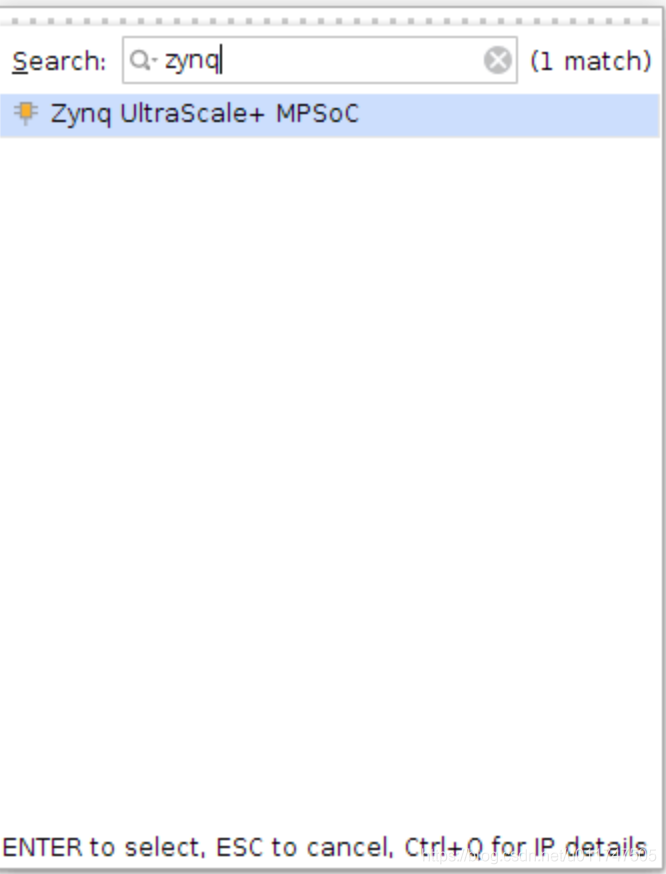

输入znyq进行过滤,并选择Zynq UltraScale+ MPSoC

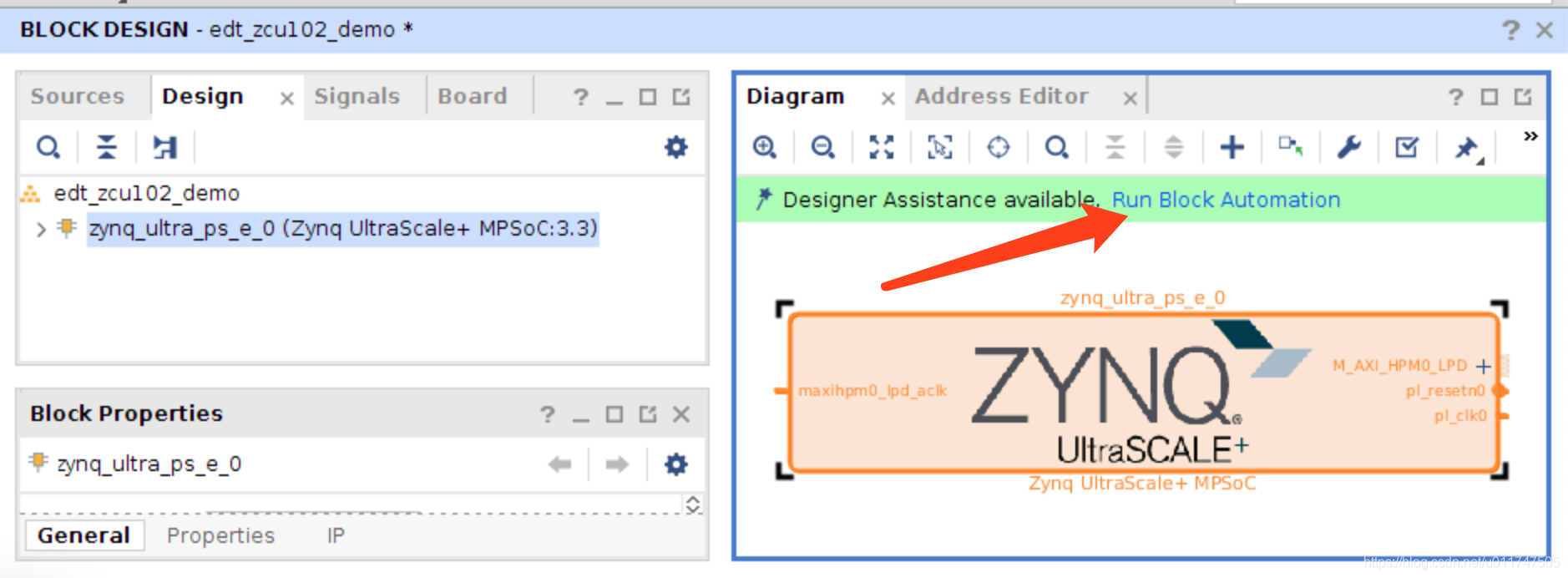

点击Run Block Automation

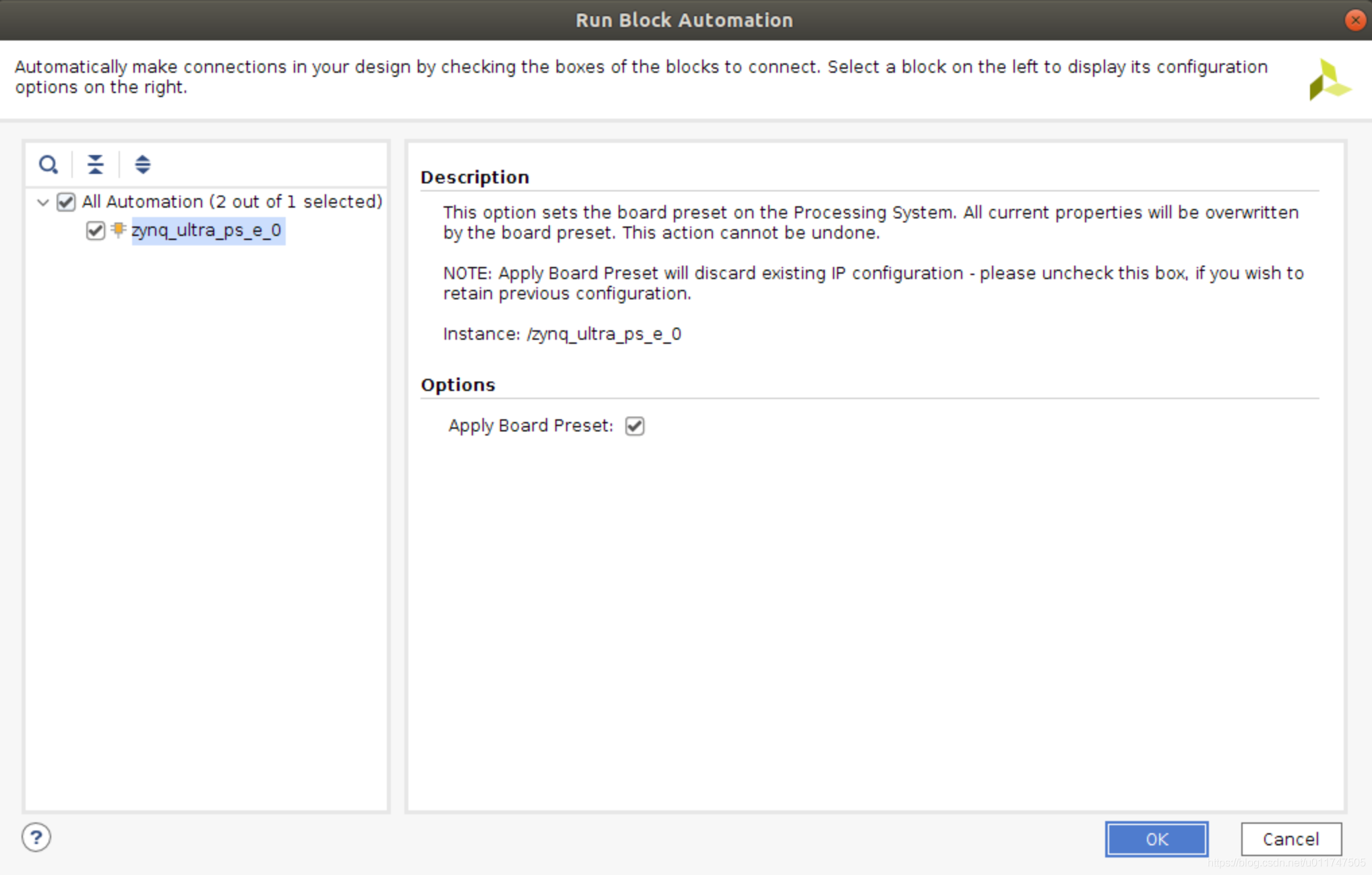

默认,点OK

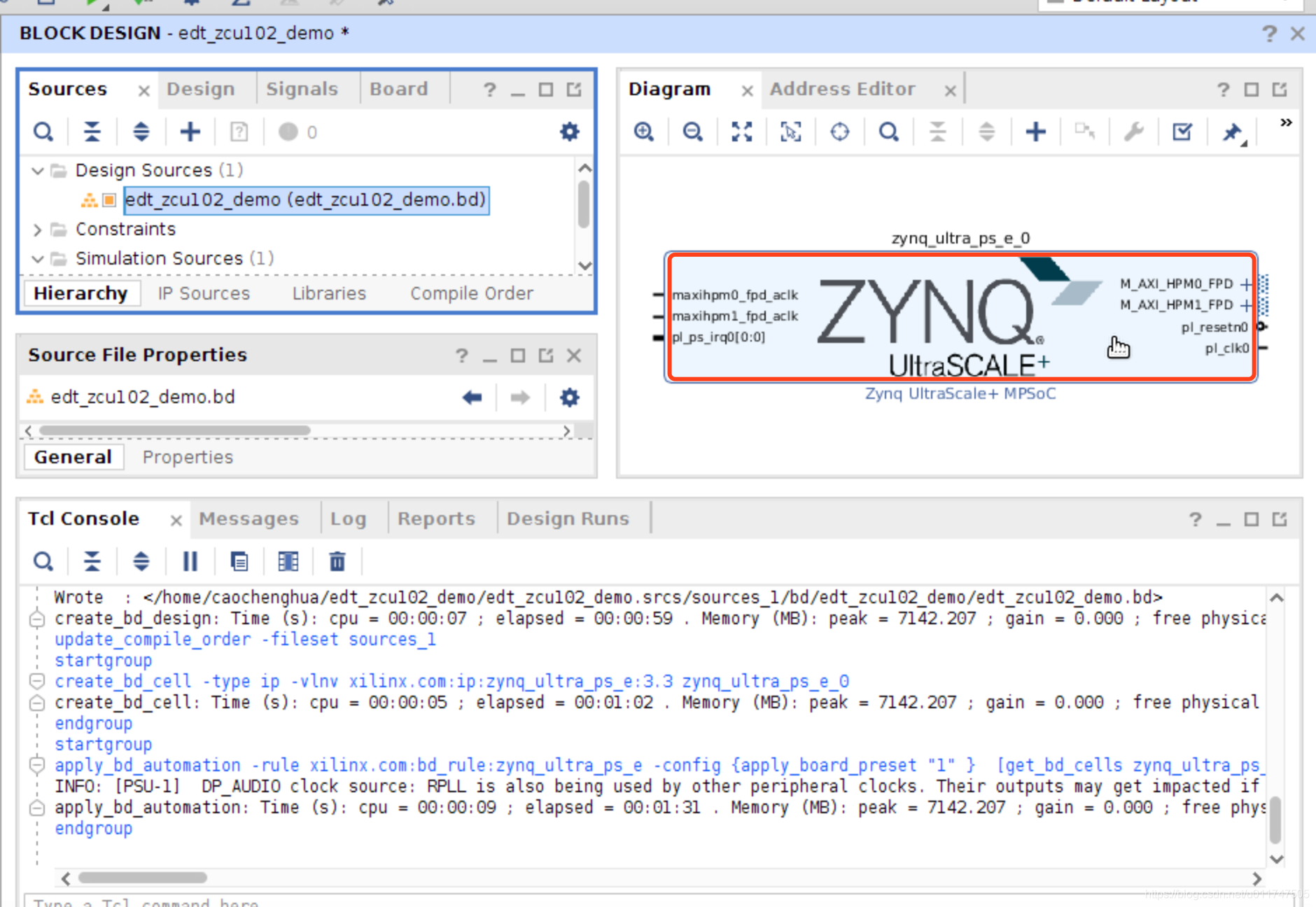

双击红框位置,查看自动化效果

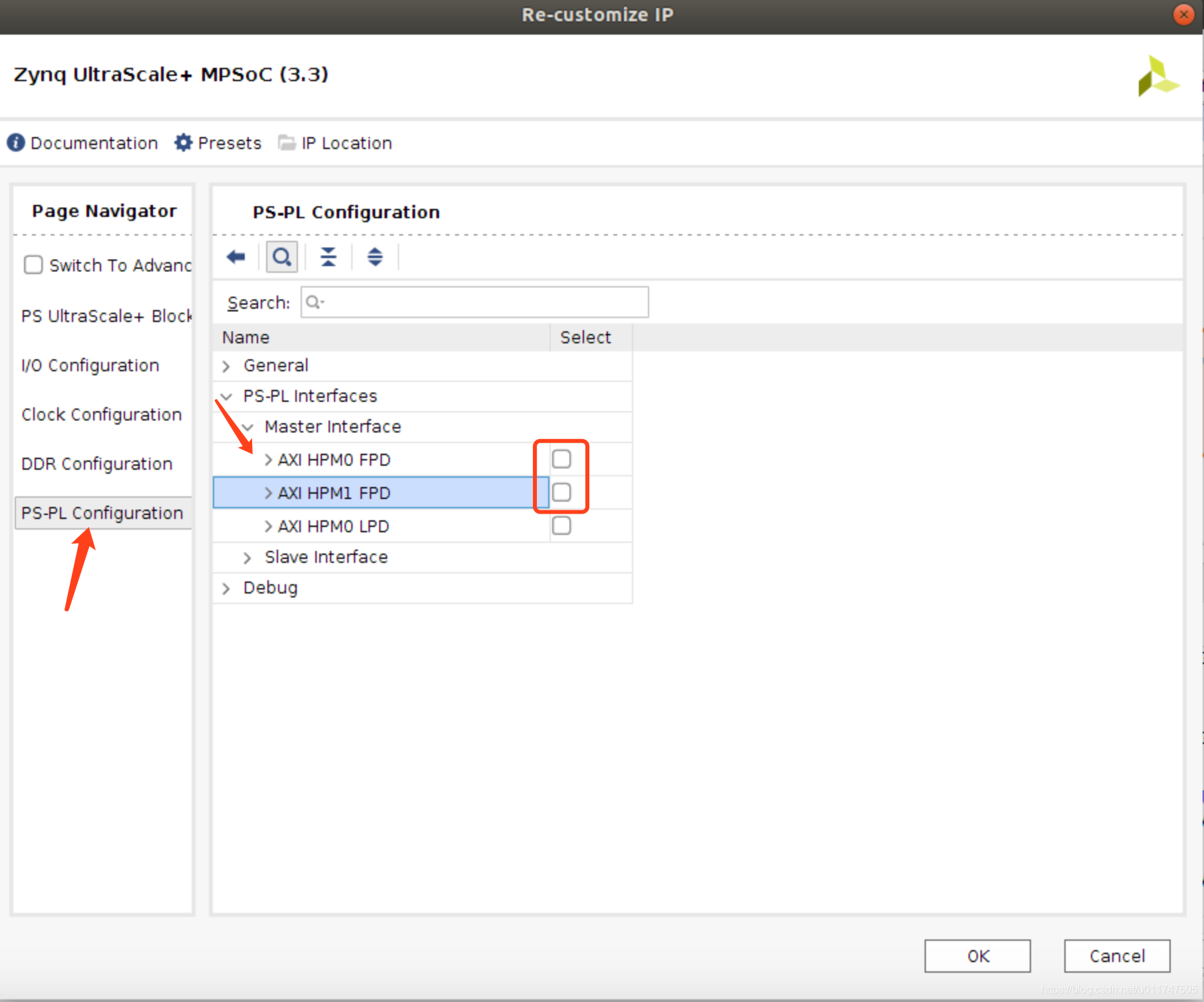

点左侧PS-PL Configuration,展开,并将红框中的勾选框取消勾选,结果如图,OK

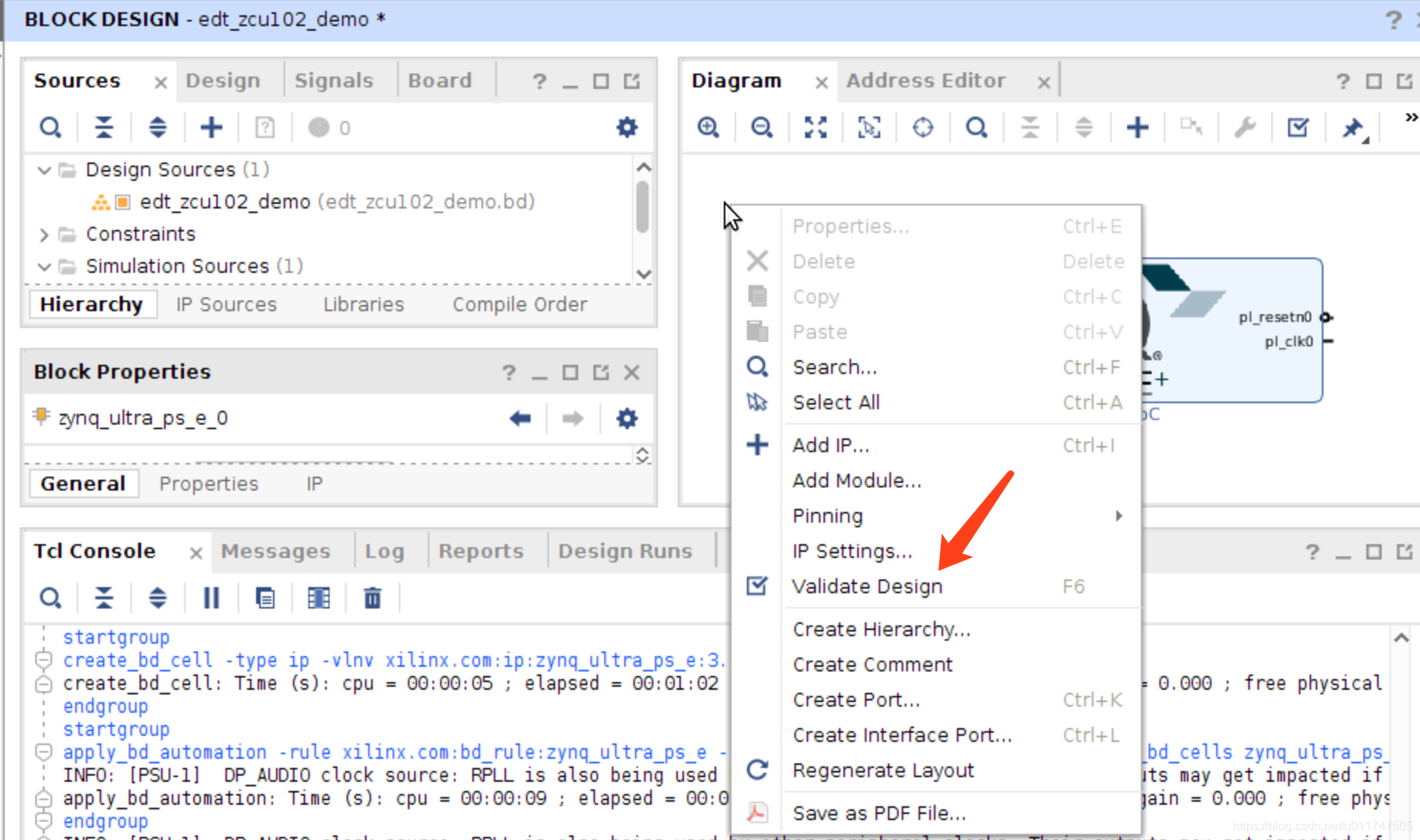

空白处右键,点击Validate Design

验证成功提示

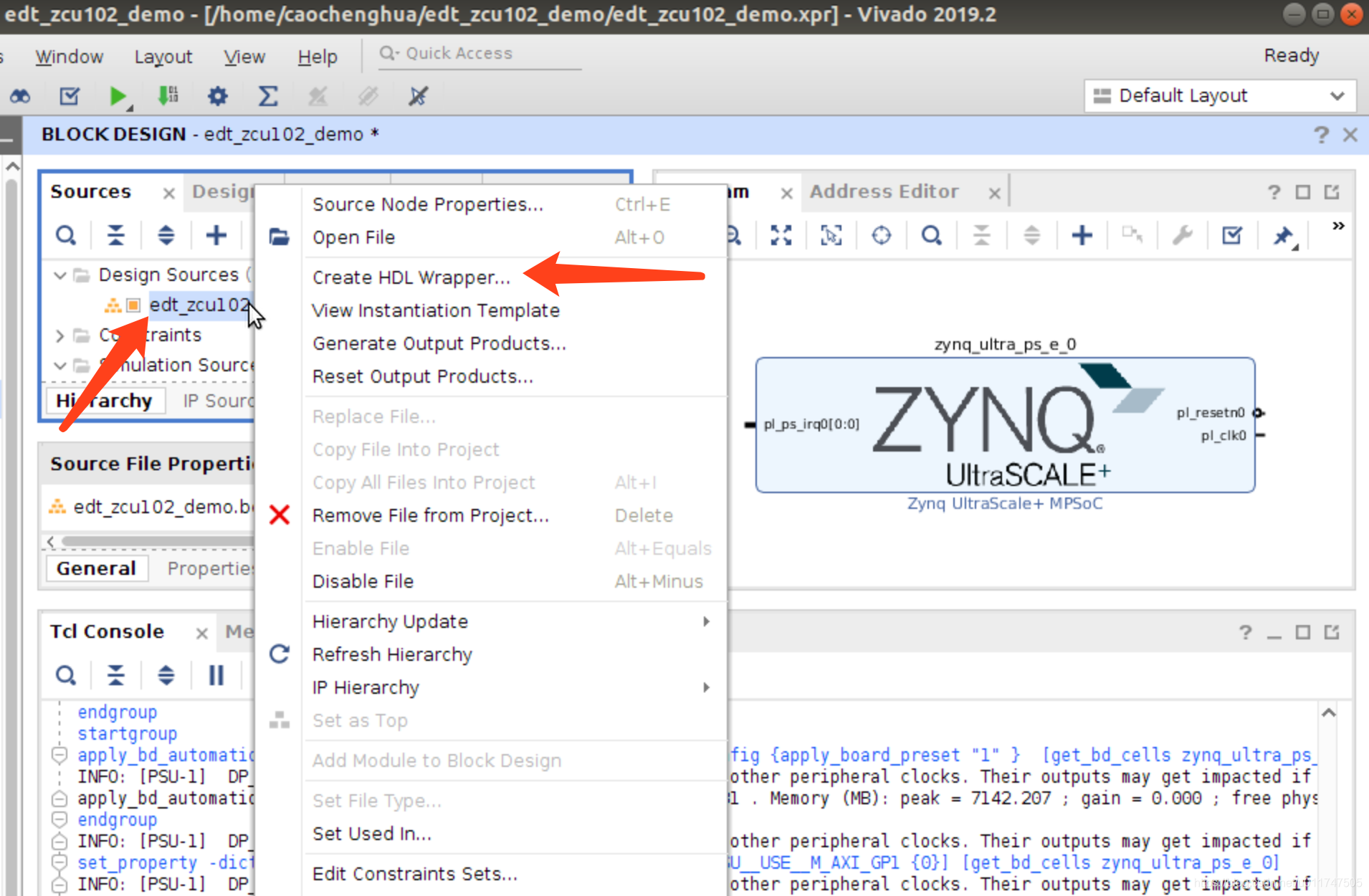

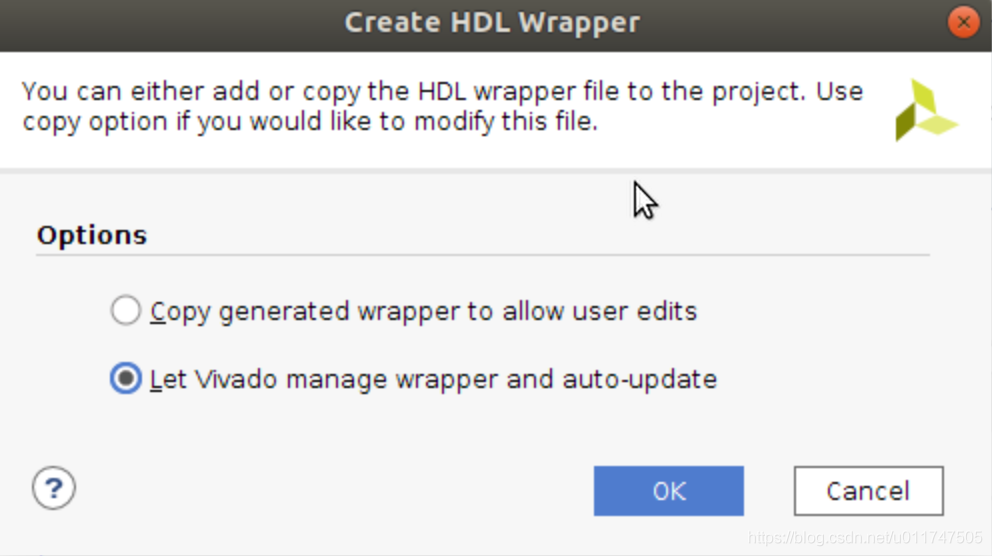

右键Design Sources下的文件,点击Create HDL Wrapper

默认,点OK

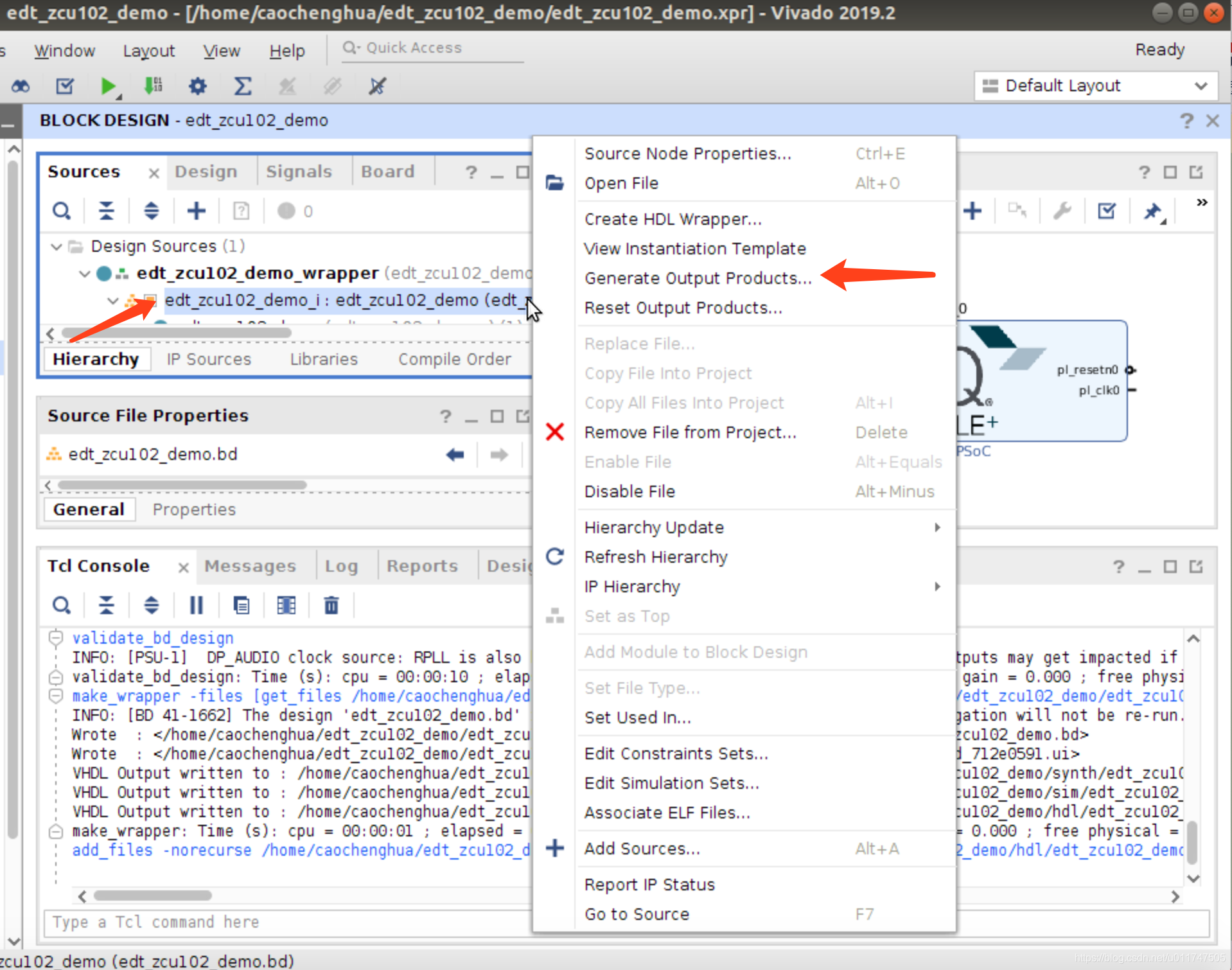

创建完成之后,展开edt_zcu102_demo_wrapper,右键左侧红箭头,然后点Generate Output Products…

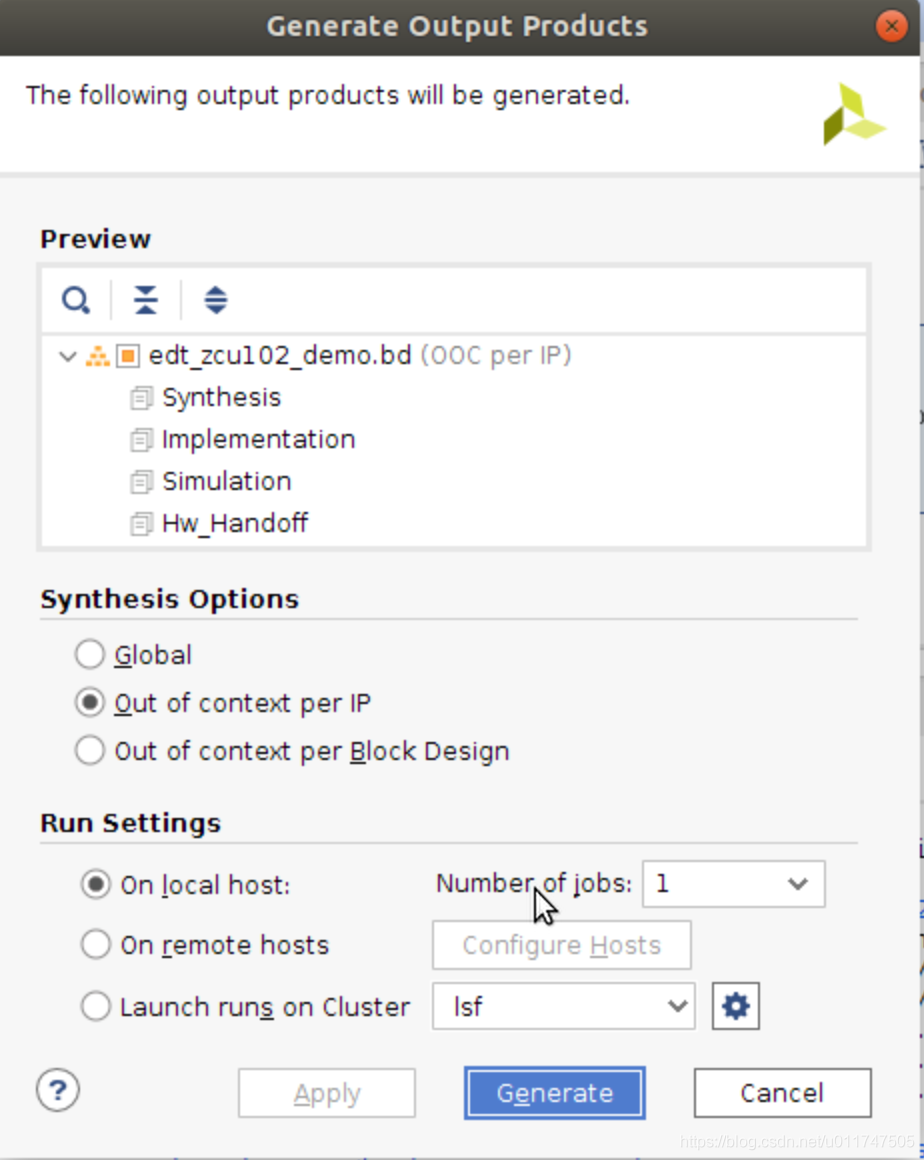

默认,点Generate

并生成最终的edt_zcu102_wrapper.xsa文件【TODO:此过程参考另一个教程】

使用petalinux生成linux镜像

petalinux和bsp(Board Support Packages)文件这里下载https://www.xilinx.com/support/download/index.html/content/xilinx/en/dow...

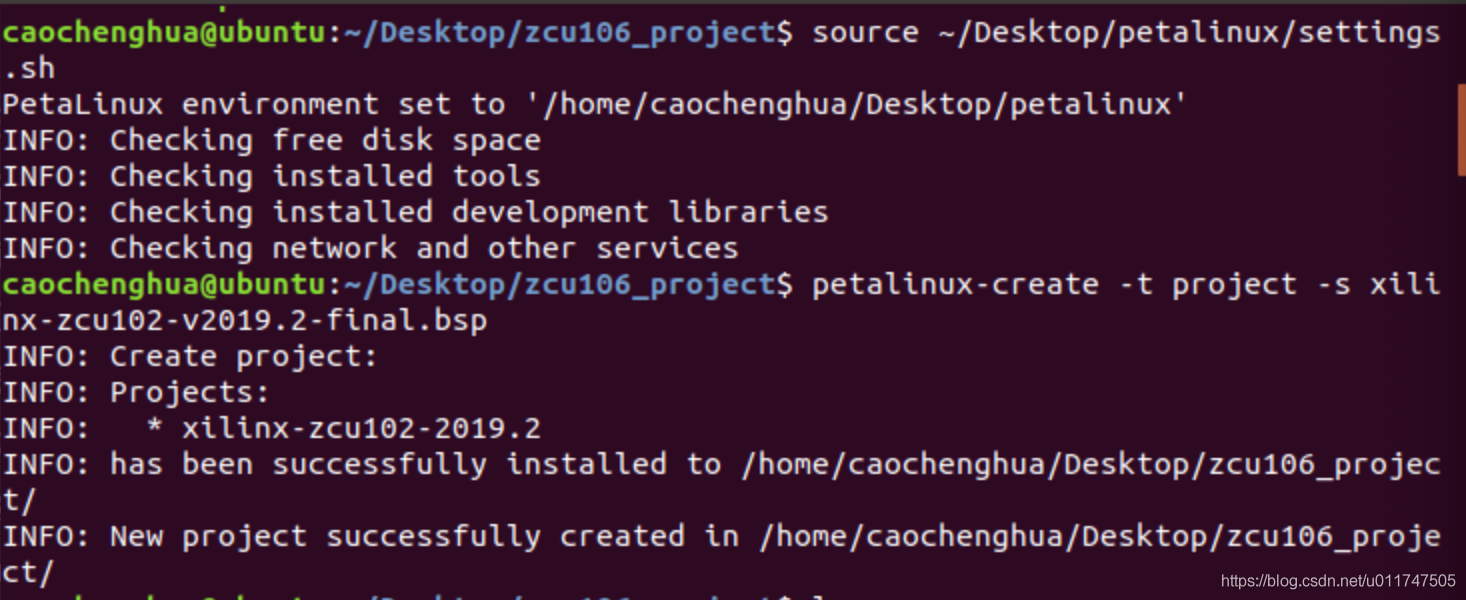

我的petalinux安装在~/Desktop/petalinux/下

执行命令source ~/Desktop/petalinux/settings.sh

进入bsp文件所在目录

创建工程命令petalinux-create -t project -s xilinx-zcu102-v2019.2-final.bsp

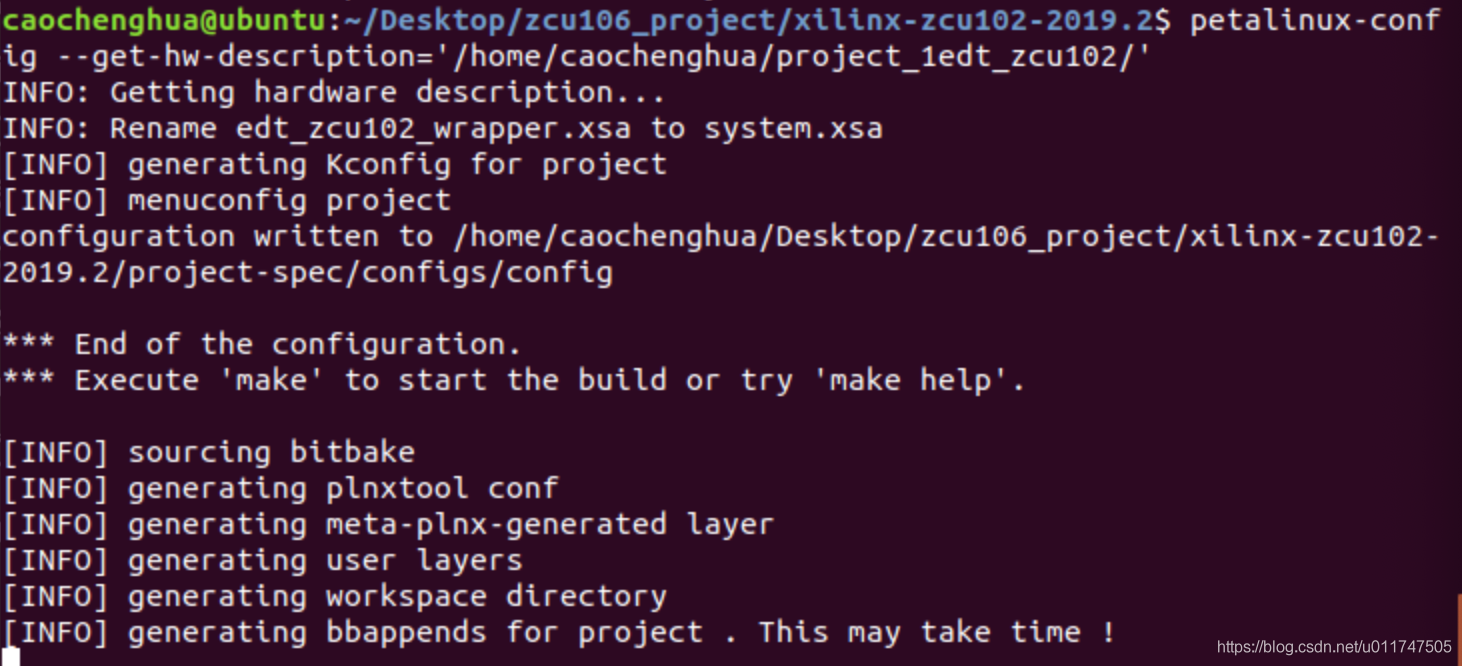

根据edt_zcu102_wrapper.xsa文件所在目录(注意不是文件,也不要拷贝.xsa至当前目录下)重新配置petalinux-config --get-hw-description='/home/caochenghua/project_1edt_zcu102/'

审核编辑 黄昊宇

-

如何在AMD Vitis Unified IDE中使用系统设备树2025-11-18 3342

-

如何在Unified IDE中创建视觉库HLS组件2025-07-02 1696

-

使用AMD Vitis Unified IDE创建HLS组件2025-06-20 2587

-

Vitis2023.2使用之—— classic Vitis IDE2024-03-24 4204

-

Vitis 统一软件平台文档2023-12-20 1716

-

Vitis Unified IDE 和通用命令行参考手册2023-09-13 2132

-

Vitis IDE Git集成快速入门2023-05-12 2220

-

Vitis程序怎么编写?2021-02-25 5846

-

第一个Xilinx Vitis IDE入门helloworld程序2021-01-23 2188

-

使用Arduino实现IDE HelloWorld实验的程序免费下载2020-12-01 1089

-

MPLAB® X IDE 入门(上)2018-06-07 6230

-

MPLAB® X IDE 入门(下)2018-06-06 3733

-

MPLAB IDE用户指南2012-03-13 2542

全部0条评论

快来发表一下你的评论吧 !