DC-DC降压电路输入和输出是否需要压差呢?

电子说

描述

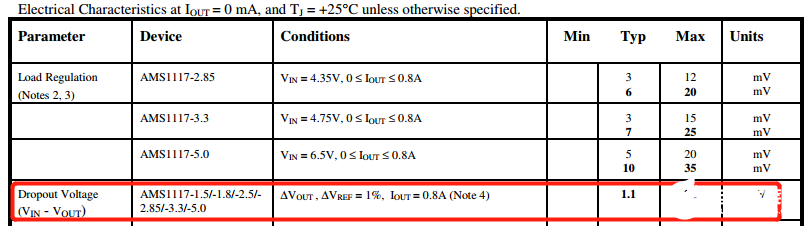

在LDO应用中,会有一个输入输出压差范围的概念,如AMS1117,压差Dropout Voltage的典型值为1.1V,即:输入至少比输出高1.1V的压降才能支持所需要的输出。

在之前写过的一篇文章《LDO与DC-DC 的入门理解》中,我们可以了解到LDO是靠内部电路分压达到降压输出,而DC-DC则是通过“断续的供给”达到降压输出。那么,DC-DC降压电路输入和输出是否需要压差呢?思考一个场景:某款Buck芯片自身工作电压范围为2.7-5.5V,现需要该芯片输出3.3V/2A。当正常输入5V时,该芯片可满载输出3.3V,当输入电压只有3.5V时,该芯片是否还能正常输出3.3V/2A呢?

该问题本质其实是DC-DC降压电路中,在输入输出规格内,芯片占空比是否受限、导通损耗的问题。理论上,但芯片的开关周期达到100%时,DC-DC其实是一个“直通”状态,即输出电压等于输入电压,当然,真实的应用中,芯片的占空比不会达到完整的100%,而且由于芯片里集成或外置的MOSFET的导通内阻以及输出电感上Rdc,实际输出电压与输入电压之间会有一个压差。

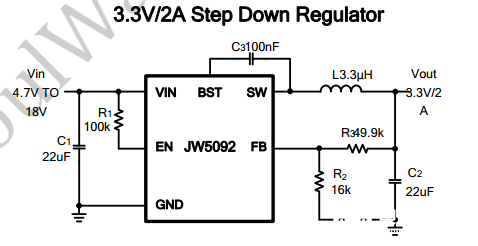

以JW5092为例,输入4.7V时,可输出3.3V/2A,但当输入为4.0V的时候,是否还能满载输出?

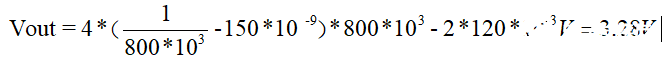

首先,根据能量守恒,我们可知(Vin-Vout)*ton=Vout*toff,由此

Vout = Vin * D,D为开关周期中,“开”的占空比。

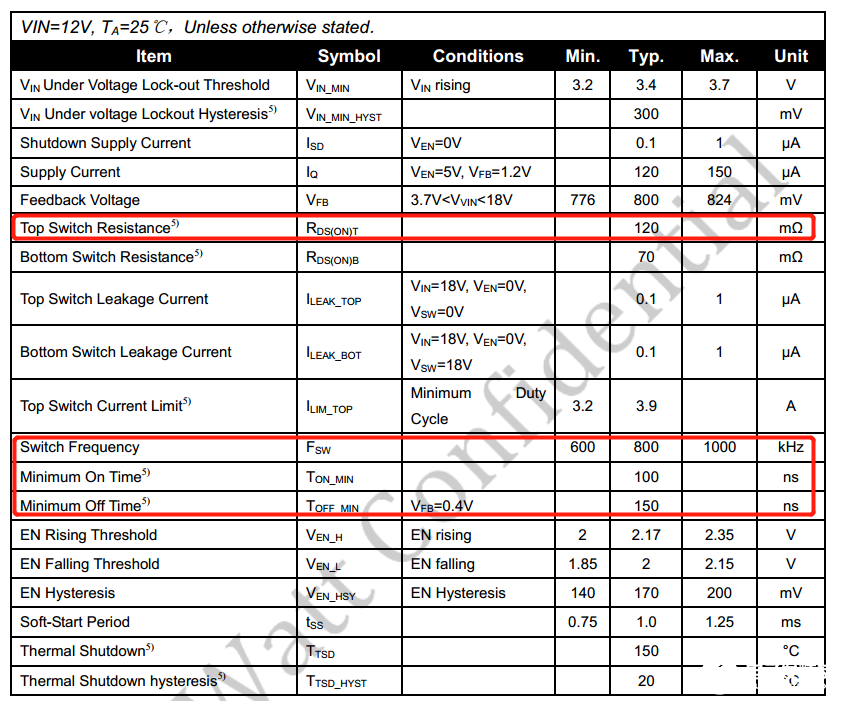

考虑,MOS管导通内阻Rds、电感内阻RL,可得:

Vout = Vin * D- Iout x (Rds(ON) + RL)

查看规格书——

当Vin = 4V时,若输出2A,暂时忽略电感选型上的内阻差异,则:

由此可知,此时该当输入为4.0V的时候,JW5092无法满载输出3.3V/2A

所以DC-DC降压电路中,实际输出电压要等于输入电压减去Buck芯片里集成或外置的MOSFET的Rds(on)以及输出电感的Rdc上产生的压降,包括由于占空比受限导致的无法满载输出。带载越重,输出电压越低。当你的输入输出压差范围很小,但仍然需要满载输出时,请考虑号称可达100%占空比的芯片!

责任编辑:PSY

- 相关推荐

- 热点推荐

- 电路

- 压差

- DC-DC芯片34063

-

电压环路:电池 → 升压电路 → 降压电路 → 电池2025-06-13 5544

-

dc-dc降压电路30v降到15v功耗多少2023-09-28 4815

-

使用MC34063芯片的DC-DC降压电路设计2023-04-20 14244

-

DC-DC降压芯片有输入输出压差范围吗2022-01-11 1672

-

DC-DC降压电路的相关资料推荐2021-11-17 2394

-

给予MP2456的DC-DC降压电源设计2021-11-06 1266

-

如何对DC-DC buck降压电路进行matlab仿真2021-09-30 2376

-

基于升降压电路的双向DC-DC变换电路2021-09-15 2319

-

使用MC34063芯片来设计一个DC-DC降压电路2021-07-29 2310

-

DC-DC升压和降压电路电感参数选择详解2016-12-17 2923

-

DC-DC升压和降压电路中电感的参数选择详解2015-05-17 3951

-

美大学开发出无需外置降压电路的集成型DC-DC转换电路2013-02-25 1250

全部0条评论

快来发表一下你的评论吧 !