通过点灯逻辑体验FPGA的编程流程

描述

“点灯”是我们板农们拿到一块板子后第一个要实现的目标,正如软件工程师尝试新的语言必然会先写出“hello world”一样。

学习FPGA也不例外,不要小瞧这只小小的LED,它能在你学习的路上带给你光明,引导一个门外汉跨进可编程逻辑世界的大门!

作为“寒假在家一起练”的第二次直播讲座,我们今天就基于1个LED做了1个多小时的分享,从创建第一个FPGA项目、写下第一句Verilog代码,到调用FPGA的IP Cores,体验了FPGA的设计流程以及Verilog的基本语法规范。

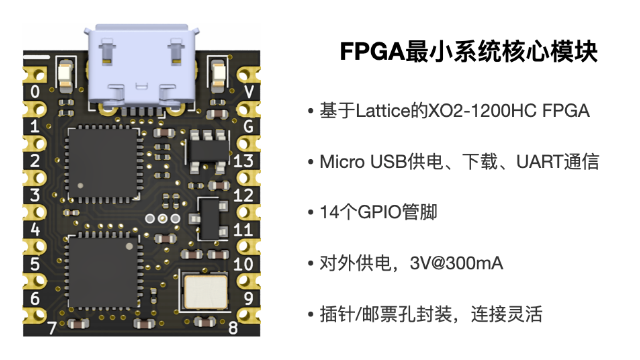

用的平台是这款:

模块MIcroUSB右侧白色的小东东就是一只用FPGA的IO连接的LED,左侧的一只是电源指示灯,只要板上电源工作正常它就能亮。而FPGA连接的LED则可以通过编程FPGA内部的逻辑实现不同的状态。

BTW,苏老师所有的FPGA项目中最前面的几行代码肯定是一个每秒跳动一次的“心跳灯”,看着它跳动,心安。

先简单说一下点灯的要素 - LED点灯的工作原理:

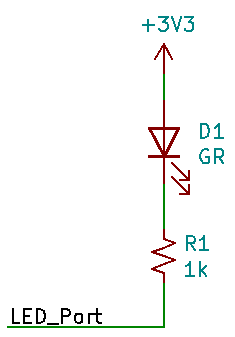

LED的典型连接方式

灯亮以及灯亮时的亮度取决于下面的因素:

供电电源和控制管脚之间的压差一定要大于LED的正向偏压Vbias灯才能亮,否则是灭的。不同的器件,不同颜色的LED其偏压也是不同的,要看数据手册;

改变电阻值R1(我们一般称之为限流电阻), I = (3.3V-Vbias)/R1也就发生了变化,LED的亮度也跟着变;

已经设计好的板子,限流电阻的值已经可能动态地改变,如果要调整LED的亮度,就要调节流经LED和限流电阻上的平均电流;

项目1 - 让LED灯亮起来:

创建项目一个新项目 - LED

创建Verilog代码 module(led),体会Verilog的语法结构;

module LED (led); output led; assign led = 1'b0; endmodule

编译

分配管脚(查找管脚映射表,通过电路图或项目中的表格)

生成jed文件

查看资源占用情况

下载到16管脚的FPGA模块上

项目2 - 让LED灯跳动起来

在module的端口中添加clk的输入信号

在verilog逻辑中通过计数分频产生12M/2 23 (~1.5Hz) 的周期信号,体会wire、reg的区别以及计数分频的实现方法

module LED (clk_in,led);input clk_in;output led; reg [23:0] counter; always @(posedge clk_in) counter = counter + 1'b1; assign led = counter[23]; endmodule

编译

分配管脚中补充新的clk管脚

生成jed文件

查看资源占用情况

下载到16管脚的FPGA模块上

项目3 - 让LED灯每秒刚好跳动1次

修改Verilog逻辑,能够产生精准的1Hz的周期信号,体会偶数分频乃至奇数分频的实现方法

module LED (clk_in,led);input clk_in;output led; parameter T1S = 12_000_000;parameter T05S = T1S/2; reg [23:0] counter; always @(posedge clk_in) begin if(counter < T1S-1) counter <= counter + 1'b1; else counter <= 1'b0; end assign led = (counter < T05S); endmodule

生成jed文件

查看资源占用情况

下载到16管脚的fpga模块上,对比结果

项目4 - 心跳加速会如何?- 50Hz的心跳灯

修改verilog逻辑,产生50Hz的周期信号

生成jed文件

下载到16管脚的fpga模块上,LED亮度变化,视觉暂留的效果,可以通过调节占空比控制LED的亮度(PWM),亮度与占空比(平均电流)非线性

单色的LED - 通过调节驱动信号的占空比调节LED的亮度

3色的LED - 通过调节每种颜色的LED的亮度实现不同的颜色组合

项目5 - 体验内部锁相环的使用以及内部IP Core的调用方式

添加PLL的IP

修改Verilog逻辑,通过PLL输出的时钟,产生1Hz的周期信号

生成jed文件

查看资源占用情况

下载到16管脚的fpga模块上

其实还有更多可玩的,时间关系就让同学们自己去琢磨和体验去了,比如:

“呼吸”灯 - 通过PWM来实现呼吸的效果

“流水”灯 - 多只LED组合,通过逻辑编程可以实现炫酷的效果(1维)

“交通”灯 - R、G、B三色组合,通过状态机的编程模拟道路交通灯的工作状态

数码管 - 其实也是几根LED组合在一起的显示器件

点阵LED屏 - 体会图形化显示的基本原理

一颗LED才几分钱,但可以玩出很多花样,可以锻炼很多技能,是不是?

原文标题:通过点灯的逻辑体验FPGA的编程流程以及Verilog语法基础

文章出处:【微信公众号:FPGA入门到精通】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA实战演练逻辑篇8:FPGA开发流程2015-03-31 4345

-

FPGA开发流程及编程思想2016-01-18 664

-

FPGA设计指南:器件、工具和流程_部分22016-04-26 631

-

可编程逻辑器件FPGA/CPLD结构与应用2016-12-11 931

-

基于FPGA进行可编程逻辑设计2017-09-12 1067

-

现场可编程逻辑门阵列器件 FPGA原理及应用设计2017-09-19 1058

-

FPGA的设计流程是怎么样的?FPGA设计流程指南详细资料免费下载2018-10-17 1852

-

FPGA通过开发软件和编程工具来对芯片进行开发2019-10-15 4039

-

关于FPGA它的开发流程是怎样的2019-11-06 2992

-

FPGA的开发流程以及它的适用场景2019-11-20 2439

-

FPGA面向汽车电子的可编程逻辑解决方案2021-01-20 1245

-

可编程逻辑阵列fpga和cpld说明2021-03-30 1253

-

FPGA CPLD可编程逻辑器件的在系统配置方法2021-09-18 1132

-

FPGA设计的基本流程2023-05-22 8207

-

fpga是什么 fpga用什么编程语言2024-02-04 3509

全部0条评论

快来发表一下你的评论吧 !