RISC-V开源、免版税、可扩展ISA获得产业发展动力

嵌入式技术

描述

作者:贸泽电子Mark Patrick

摘要:全新的指令集体系架构(ISA)在半导体处理器行业并不经常出现。业界最后一次重大变化是Arm开发了内核,并将其作为IP许可证出售,从而迅速改变了那个时代领先供应商设计处理器的方式。目前,在贸易战和新冠大流行时期,市场提供的开放源代码、免版税、可扩展ISA被证明是一种变革和颠覆性力量。

简介:指令集体系架构在过去40年中变化不大,但是开源,免版税,可扩展的RISC-V正在撼动整个行业。

SEO关键词:x86,MIPS,ISA,指令集体系架构,RISC,CISC,RISC-V,Microchip,AVR,Atmel,Atmel AVR,Arm,Intel,SoC,FPGA,SparkFun,SEEED

40年以来几乎未变的处理器ISA

几十年来,英特尔和Arm一直主导着处理器架构。英特尔及其x86架构一直在统治着计算机工作站、台式机和服务器市场。同时,Arm在物联网设备、消费电子产品和工业自动化系统等领域拓展了更广阔的市场空间。市场中也有其他嵌入式处理器和微控制器架构,例如Atmel的AVR和Microchip的PIC / MIPS,它们都有自己的利基市场,但并未达到主导地位。在嵌入式系统环境中,大多数MCU和MPU供应商已广泛采用Arm的IP授权模式。但是,颠覆性,变革性变化正在迅速获得强大发展势头,并开始挑战处理器市场现有体系。随着客户越来越多地接受开源技术带来的商业和技术利益,领先供应商正在迅速转向开源RISC-V指令集体系架构。在本文中,我们将介绍RISC-V的诞生,并重点讨论使其具有更大吸引力的一些因素。我们也将提供一些产品示例,重点关注评估板、开发资源以及不断发展的软件工具链生态系统。

ISA:处理器硬件和软件之间的真正连结

指令集体系架构能够提供软件世界和处理器硬件之间的界面,它定义了一个程序如何与可用硬件之间交互的各个层面,包括算术逻辑单元(ALU)、寄存器、存储器和控制逻辑。它还能够确定字长、支持的数据类型以及寄存器和存储器的寻址方式。简而言之,ISA是处理器的抽象。

ISA有许多不同类型,但是出于大多数实用目的,两个最重要类型是复杂指令集计算机(CISC)和精简指令集计算机(RISC)。顾名思义,CISC包含许多针对各种应用的复杂且专门的指令,其中一些功能可能很少出现。 CISC处理器可以具有许多不同的寻址方式,并使用可变长度指令。基于CISC的处理器设计成本高昂,需要更复杂的软件和编程工具,并且设计时间也更长。 CISC ISA的一个示例是Intel x86。

相比之下,基于RISC的处理器要简单得多,并且具有一组有限的常用指令,几种不同的寻址方式以及一个固定的指令大小。使用指令流水线技术能够支持更快的执行吞吐量。与CISC处理器将操作数(数据值)移出内存来执行计算不同,RISC处理器使用内部寄存器。基于RISC的ISA应用示例包括Arm、AVR、PIC和MIPS。

图1:Microchip AVR微控制器RISC架构示例。

ISA – 成功的关键要素是什么?

在本文余下部分,我们将只讨论基于RISC的处理器。在提到处理器时,本文上下文中是指任何处理设备,例如微控制器和微处理器。市场中流行的RISC ISA具有8位、16位和32位字长,还有64位和128位ISA通常用于要求更高的专业应用。字长对硬件设计、处理器可运行的速度以及可用的内存大小有重要影响。从最基本层面考虑,ISA至少需要包括算术逻辑单元、存储器和控制逻辑。算术逻辑单元执行基本的算术计算功能,例如使用寄存器或自身内部的“立即”方式进行加法、比较和减法等运算。内存寻址可以是绝对或索引方式。控制逻辑则执行有条件和无条件分支以及其他寻址任务。

ISA指令集由操作码(机器码)组成,这些操作码通常在一个操作数上指定要执行的任务。例如,在Atmel / Microchip AVR ISA中,模数转换器(ADC)定义将两个寄存器中保存的操作数与进位标志加在一起,并将结果存入目标寄存器中。 ISA文档将确定每条指令执行多少个时钟周期或程序计数器迭代。在RISC处理器中,大多数指令将是单周期。

对于微控制器(MCU)和微处理器(MPU)供应商,开发ISA是设计其产品的核心组成部分。通过这种方式,ISA已成为用于一系列特定设备的专有技术,例如Atmel / Microchip的AVR(8、16、32位)、Microchip的PIC(8、16、32位)和MIPS(32和64位)。

Arm在1990年代初从Acorn剥离出来时就打破了传统MCU/MPU商业模式。Arm方式采用了IP许可路线,从特许权使用费中创造了收入来源,而不是依靠制造和销售器件。 Arm商业模式得以迅速取得成功,使半导体供应商摆脱了开发和移植ISA的任务。如今,大多数半导体供应商都提供基于Arm ISA的处理器,有些还提供基于其自身ISA的设备。出售的每个设备都要向Arm支付版税。Arm实际上在控制着ISA的生命周期和持续发展。

尽管各个ISA都有其优缺点,但是任何特定处理器体系架构的成功不仅取决于其技术优势,还取决于市场中其软件开发工具生态系统的完善。工具链、集成开发环境、编译器、调试器和专用中间件(application-specific middleware)在促进处理器及其ISA的普及程度方面起着至关重要作用。

开源指令集架构

由于Arm可提供标准ISA,对于半导体供应商而言,他们可以在标准ISA基础上来适应和增强设备的外围接口选项,以满足特定应用需求。与使用Arm IP的其他竞争半导体厂商相比,这种方法还可以在一定程度上促进产品的差异化。对于AVR、PIC等已有ISA,Arm的广泛采用已降低了它们在市场中的总体份额。

但是,对于处理器客户来说,由于存在多个处理器供应商,因此在架构上做出决定来采用Arm ISA时非常明智,由此可以方便地选择购买选项和再次采购相似部件。采用特定工具链进行标准化开发也具有很大的商业意义。

在一个包含许多开放源代码概念的行业中,处理器指令集体系架构领域看起来专有性很强,直到RISC-V ISA于2010年问世,一直是这种情况。RISC-V ISA最初是在加利福尼亚大学伯克利分校开发,是出于学术目的而开发的ISA,其发展理念使ISA开源迅速立足生根。之所以将其开源是因为ISA设计在过去40年中变化不大。使其开源将鼓励更多的相互交流和软件重用,并由此希望得到工具链供应商的长期支持。作为一种开源ISA,厂商无需支付任何特许权使用费,并且可以做出新的指令集和扩展指令。

基本RISC-V ISA及其相关扩展指令是由于学术研究团体和行业之间的共同努力而开发和管理。RISC-V ISA支持32位,64位和128位字长。

2015年,在半导体公司合作建立RISC-V基金会(RISC-V Foundation)后,RISC-V的发展迈出了重要一步。不支付特许权使用费和可扩展性的优势吸引了广大厂商注意。Arm授权许可用户虽不能调整指令集以适合如低功耗等特定应用要求,但RISC-V被授权方则完全可以。RISC-V基金会现有750多个行业成员。

随着许多主要的处理器供应商开始对RISC-V表现出兴趣,软件工具社区也不甘心落后,开始在集成开发环境和工具链中扩展对RISC-V的支持。

用RISC-V启动设计

SiFive 的Freedom E31 SoC是最早可用的基于RISC-V的32位处理器之一。SiFive由RISC-V ISA创始人创立,之后迅速寻求将其专业技术推向市场。为了鼓励原型开发,SiFive众筹了一个低成本Arduino尺寸开发板HiFive1。SiFive的 HiFive1 B包含有Wi-Fi连接和32Mb闪存。

图2:SiFive 的HiFive1 B开发板。。

SEEED也可以提供一个Feather/MKR格式开发板Sipeed Longan Nano,它配备有0.96英寸LCD,采用GigaDevice 32位RISC-V内核。

SparkFun同样提供类似于HiFive1 B的开发板。SparkFun的RED-V RedBoard还使用Arduino UNO-R3尺寸规格和SiFive E310 RISC-V SoC。

针对专业工程师的更全面RISC-V平台是Microchip的PolarFire SoC FPGA Icicle开发板。

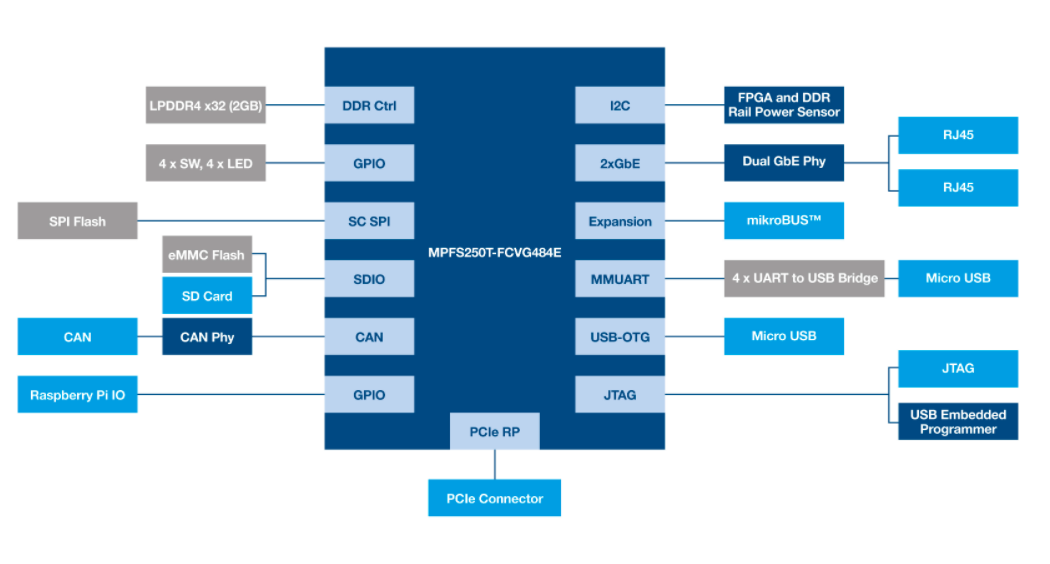

PolarFire SoC旨在为具有Linux功能的五核RISC-V RV64内核提供评估平台,还配备有256k逻辑单元和784单元的数学模块。 Icicle套件包括HDMI、PCIe、USB、CAN、SPI和I2C等在内的全面外围接口连接,是从物联网传感器到机器学习等应用所需实时、低功耗设计原型的理想选择,其外部扩展接口选项包括一个mikroBUS插槽和一个Raspberry Pi 40引脚连接器。

图3:Microchip RISC-V PolarFire SoC评估套件功能框图。

RISC-V未来前景

在相对较短的时间内,RISC-V指令集架构就已经获得了巨大产业动力。RISC-V基金会在2020年7月庆祝了RISC-V最初开发的十周年纪念。根据基金会网站的数据,现在已经有12款基于RISC-V的SoC开始商用,并且有86个内核。

与其它ISA相比,RISC-V凭借具有竞争力的可扩展且免版税替代方案,已迅速在市场中确立自己的强有力地位。

-

《RISC-V能否复制Linux 的成功?》2024-11-26 941

-

RISC-V在中国的发展机遇有哪些场景?2024-07-29 989

-

RISC-V产业论坛召开,专利联盟正式成立2023-08-30 1167

-

为什么IAR编译器对开源ISA:RISC-V业务至关重要?2023-07-14 614

-

RISC-V架构2023-04-03 2043

-

risc-v是什么意思2023-03-30 2241

-

我了解的RISC-V2023-03-19 1235

-

布局 RISC-V 领域,中国联通加入中国 RISC-V 产业联盟2023-03-16 1504

-

RISC-V简介2023-02-27 1379

-

RISC-V基础知识:模块化开放式的ISA CISC和RISC代码区别2022-12-23 2261

-

RISC-V ISA是怎样进行命名的2021-12-09 1705

-

为什么选择RISC-V?2020-07-27 5037

全部0条评论

快来发表一下你的评论吧 !