基于TLl6C550C实现数字信号处理器与PC机串行通信的应用设计

处理器/DSP

描述

作者:王鹏,谭争光,褚凌越,陈晓明

高速数字信号处理器(DSP)在图像处理中,特别是视频处理中的应用非常广泛。通常DSP都具有很强的运算能力,但是其外设的接口相对有限。在应用系统中,往往需要DSP与下位机通信或者接受上位机的控制信号时,一般都是采用异步串行通信协议,如RS232或RS422来实现。由于TMS320C6416器件自身只带有同步的串口,因此,为了实现正常的通信,一般都需要为其扩展异步串口。

1 TLl6C550C芯片介绍

TLl6C550C是TI公司研发的异步通信器件,其主要性能特点如下:

◇供电电压为5 V或3.3 V;

◇时钟频率达到16 MHz。通信时波特率最高可达1 M,并可编程设定波特率发生器;

◇具有标准的异步通信位,可选择5、6、7或8位串行数据位,可设置奇偶校验或无校验模式,停止位长度为1、1.5、2;

◇可独立控制发送、接收、线状态以及中断设置,可软件设定FIFO,减少CPU中断。

TLl6C550C器件内部共有10个寄存器,可分别用于实现通信参数的设置、对线路及MODEM状态的访问、数据的发送和接收以及中断管理等功能。TLl6C550C的地址可分别通过A0-A2地址线和某些寄存器的特定位置来确定,由于有些寄存器的地址是重叠的,所以还需同时通过读/写信号加以区分。

TLl6C550C片内寄存器及其映射地址如表1所列,其中高位和低位寄存器为二次寻址寄存器,因此,在访问这两个寄存器之前,必须将LCR的第7位置为1。

2 TLl6C550C与PC的数据通信电路

2.1 TLl6C550C的选通

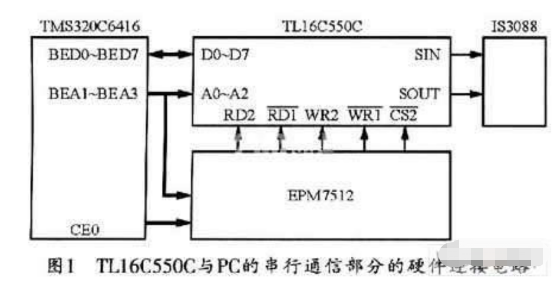

TLl6C550C与PC的串行通信部分的硬件连接电路如图1所示。由ISO3088实现电平转换,即通过ISO3088将输出电平配置为RS485信号。

2.2 TLl6C2550C的读写

TLl6C550C的读信号为,RD2,当为低电平或RD2为高电平,且TLl6C550C被选中时,可进行读操作;写信号为,WR2,当为低电平或WR2为高电平,且TLl6C550C被选中时,可进行写操作。将、RD2、、WR2都与CPLD的I/0相连,便可通过CPLD来控制TLl6C550C的读写。

3 TLl6C550C和PC通信的软件编程

该套系统的软件设计部分主要包括PC机程序、DSP初始化、TLl6C550C初始化和数据发送/接收以及双方的通信协议等。本文着重介绍TLl6C550C的初始化程序。主要由以下几部分组成:

◇波特率的设定;波特率除数寄存器由高8位(DLM)和低8位(DLL)组成。除数的值可由UART的工作时钟和波特率共同确定,其计算公式为:

除数=时钟频率/(期望的波特率×16)

例如本系统中时钟频率12 MHz,波特率设置为9600,则除数的值为12,应在初始化程序中设置DLM=OOH,DLL=4eH;

◇增强功能的使能及设置EFR的相关位;

◇完成有关收/发FIF0的设定,主要是MCR/TCR/TLR三个寄存器的设置;

◇传输数据格式设定,包括8位数据位、1位停止位以及无校验;

◇设置FIFO控制以及中断控制寄存器。

此外,在完成设置前,还应注意:设定DLL和DLH前,LCR的第7位应为1;地址相重叠的寄存器不能同时使能;读写RHR和THR时,DSP的读写速度很快,故最好不要连续读写,而是在每读、写一次后延时一段时间。然后再进行下一次读写。

由于TLl6C550C映射在DSP的CEO区间,所以在DSP访问其寄存器时只需将基地址加上偏移量即可。其初始化源程序如下:

4 结束语

本文介绍了通过TLl6C550C扩展串口完成TMS320C6416与PC机串行通信的设计方案,给出了硬件设计框图及软件实现代码。该电路及软件经实验证明能够可靠地实现TMS320C416与PC机之间的通信,并且此方法已在实际的项目中得到应用。

责任编辑:gt

-

TMS320C6745浮点数字信号处理器技术简介2024-10-09 486

-

TMS320C6457通信基础设施数字信号处理器数据表2024-08-07 427

-

SM320C6457-HIREL通信基础设施数字信号处理器数据表2024-08-06 488

-

SMJ320C80数字信号处理器数据表2024-08-02 539

-

数字信号处理器概论2023-08-07 13799

-

数字信号处理器的常见故障2023-05-31 5489

-

数字信号处理器的特点2020-12-09 2133

-

TMS320C6474数字信号处理器硅修订2.1, 1.2, 1.1, 1.0 勘误表2018-04-16 1210

-

PC 机与单片机串行通信实现2017-09-03 1063

-

TMS320C54x数字信号处理器硬件结构2016-05-06 1216

-

数字信号处理器(DSP)2010-01-04 3767

-

TMS320C3x DSP和PC机的异步串行通信设计2009-05-21 1375

全部0条评论

快来发表一下你的评论吧 !