全加器真值表解释

电子常识

2685人已加入

描述

全加器真值表解释

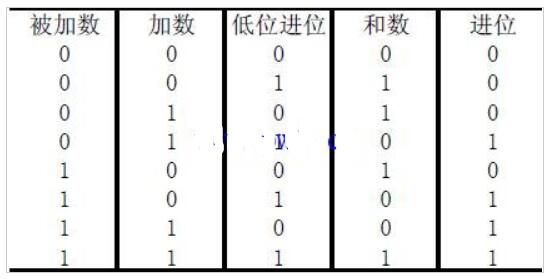

全加器能进行加数、被加数和低位来的进位信号相加,并依据求和作用给出该位的进位信号。依据它的功用,能够列出它的真值表,如表1.2所示。

表1.2 一位全加法真值表

全加器结构化描述方式

module FA_struct (A, B, Cin, Sum, Count);

input A;

input B;

input Cin;

output Sum;

output Count;

wire S1, T1, T2, T3;

// -- statements -- //

xor x1 (S1, A, B);

xor x2 (Sum, S1, Cin);

and A1 (T3, A, B );

and A2 (T2, B, Cin);

and A3 (T1, A, Cin);

or O1 (Count, T1, T2, T3 );

endmodule

该实例显示了一个全加器由两个异或门、三个与门、一个或门构成 (或者可以理解为两个半加器与一个或门的组合)。S1、T1、T2、T3则是门与门之间的连线。代码显示了用纯结构的建模方式,其中xor 、and、or 是Verilog HDL 内置的门器件。以 xor x1 (S1, A, B) 该例化语句为例:xor 表明调用一个内置的异或门,器件名称xor ,代码实例化名x1(类似原理图输入方式)。括号内的S1,A,B 表明该器件管脚的实际连接线(信号)的名称,其中 A、B是输入,S1是输出。

责任编辑:YYX

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

怎么利用QuartuesII查元件真值表2012-11-15 3439

-

74LS00芯片资料及真值表2012-12-07 22211

-

怎么利用QuartusII查元件真值表2012-12-20 7496

-

求常用单片机的功能表、引脚图、真值表2013-04-25 3306

-

关于多位输入真值表的问题2013-07-11 2622

-

帮忙看下,我仿真出来的怎么和真值表不一样啊,是不是.....2013-10-08 3879

-

输入真值表相同 输出结果不同 74HC1382014-10-26 8783

-

LUT真值表在实施期间发生了变化2018-11-01 2805

-

LUT与真值表有何关系2021-11-02 3707

-

全加器2009-04-07 10330

-

真值表,真值表是什么意思2010-03-08 30015

-

与门真值表2011-03-20 27732

-

与门真值表和与非门真值表的区别2018-01-30 124214

-

全加器真值表和半加器真值表详细分析2018-07-25 146616

-

全加器的真值表2021-06-29 63542

全部0条评论

快来发表一下你的评论吧 !