加法器工作原理_加法器逻辑电路图

电子常识

描述

加法器工作原理

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。在电子学中,加法器是一种数位电路,其可进行数字的加法计算。三码,主要的加法器是以二进制作运算。由于负数可用二的补数来表示,所以加减器也就不那么必要。

设一个n位的加法器的第i位输入为ai、bi、ci,输出si和ci+1,其中ci是低位来的进位,ci+1(i=n-1,n-2,…,1,0)是向高位的进位,c0是整个加法器的进位输入,而cn是整个加法器的进位输出。则和

si=aiii+ibii+iici+aibici ,(1)进位ci+1=aibi+aici+bici ,(2)

令 gi=aibi, (3)

pi=ai+bi, (4)

则 ci+1= gi+pici, (5)

只要aibi=1,就会产生向i+1位的进位,称g为进位产生函数;同样,只要ai+bi=1,就会把ci传递到i+1位,所以称p为进位传递函数。把式(5)展开,得到:ci+1= gi+ pigi-1+pipi-1gi-2+…+ pipi-1…p1g0+ pipi-1…p0c0(6) 。

随着位数的增加式(6)会加长,但总保持三个逻辑级的深度,因此形成进位的延迟是与位数无关的常数。一旦进位(c1~cn-1)算出以后,和也就可由式(1)得出。

使用上述公式来并行产生所有进位的加法器就是超前进位加法器。产生gi和pi需要一级门延迟,ci 需要两级,si需要两级,总共需要五级门延迟。与串联加法器(一般要2n级门延迟)相比,(特别是n比较大的时候)超前进位加法器的延迟时间大大缩短了。

加法器逻辑电路图

计算机内部两个二进制之间的加、减、乘、除算术运算都将转化成若干步的加法运算进行。因此,在数字系统中,尤其在计算机的数字系统中,二进制加法器是其基本部件。

实现1位二进制数之间加法运算的电路称为1位加法器。根据加数的不同,1位加法器又分为半加器和全加器两种电路类型。

如果不考虑来自低位的进位而是只将两个1位二进制数相加,即只有加数和被加数相加,这种加法运算称为半加运算。实现半加运算的电路叫做半加器。

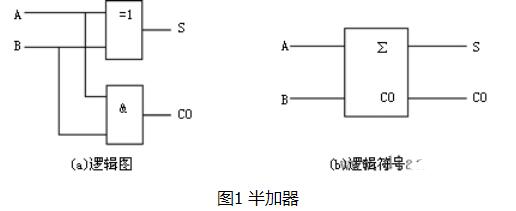

按照二进制加法运算的规则,列出半加器的逻辑真值表如表1所示。其中A、B是加数和被加数,S是相加的和(本位和)输出,CO是向相邻高位的进位输出。

根据真值表写出逻辑函数式并化简:

画出半加器的逻辑图如图1(a)所示。图5-4-1(b)所示为半加器的逻辑图形符号。

责任编辑:YYX

-

支彤垚

2021-09-25

0 回复 举报进制转换 收起回复

支彤垚

2021-09-25

0 回复 举报进制转换 收起回复

-

加法器是时序逻辑电路吗2024-08-28 2426

-

同相加法器和反相加法器的区别是什么2024-05-23 5705

-

镜像加法器的电路结构及仿真设计2023-07-07 5497

-

半加法器的工作原理及电路解析2023-06-29 14819

-

加法器的原理及采用加法器的原因2023-06-09 6815

-

超前进位加法器是如何实现记忆的呢2022-08-05 2637

-

什么是加法器?加法器的原理是什么 ?2021-03-11 5211

-

反相加法器原理图与电路图2018-03-16 22516

-

同相加法器电路图_反相加法器电路图_运放加法器电路图解析2017-08-16 150607

-

同相加法器电路原理与同相加法器计算2016-09-13 59014

-

十进制加法器,十进制加法器工作原理是什么?2010-04-13 14576

-

加法器,加法器是什么意思2010-03-08 5950

全部0条评论

快来发表一下你的评论吧 !