基于12位D/A转换器实现数控直流电流源的设计

描述

1 引言

电流源是一种能向负载提供恒定电流的电路,它既可以为各种放大电路提供偏流以稳定其静态工作点,又可以作为其有源负载以提高放大倍数,在差动放大电路,脉冲产生电路中得到了广泛应用。2005年全国大学生电子设计竞赛的F题就是数控直流电流源设计。

设计题目要求设计并制作数控直流电流源,输入交流为200V-240V,50Hz,输出电流电压≤10V,具体技术指标如下:

输出电流范围:20mA-2000mA,步进1mA;

可设置并显示输出电流给定值,要求输出电流与给定值偏差的绝对值≤给定值的0.1%+1mA,可显示电流的实测值,要求测量误差的绝对值≤测量值的0.1%+3个字。

改变负载电阻,输出电压在10V以内变化时,要求输出电流变化的绝对值≤输出电流值的0.1%+1mA;

纹波电流≤0.2mA。

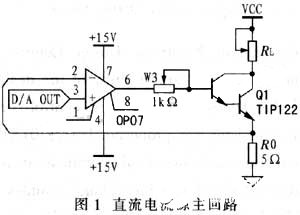

根据上述设计要求,实现电流调节范围20mA-2000mA(输出电流电压≤10V),并顾及器件极限功耗的局限,电流源采用TIP122型普通功率放大器和OP07型达林顿管相结合的方案,间接控制电流大小,其主回路电路如图1所示。

图1中负载端的最高电压值(10V)决定了负载的最大电阻值(5Ω),它又决定了电流源工作电源的最低电压值及所用功率器件的极限电压参数。后级R0为采样电阻器,选用大功率的康铜电阻丝自行绕制而成,阻值为5.00Ω,RL为负载电阻器(0Ω-5Ω),选用大功率滑线变阻器,由此可知负载电流IL≈VIN/R0,与RL无关,当VIN恒定不变时,改变采样电阻R0的阻值大小,可改变IL的恒定值,OP07输出端接TIP122的基极,由于基极的电流很小,电流极限和功耗极限都满足,同时TIP122能满足5A大电流的要求,电流调整率小且稳定。

由于输出电流调整采用步进方式,其电流调整率≤1‰,即1mA(输出电流电压≤10V)的指标,经计算,12位D/A转换器的转换精度达0.0024V,满足系统要求的精度,笔者采用DAC1201KP-V型12位D/A转换器作为电流输出控制的转换核心。

2 DAC1201KP-V

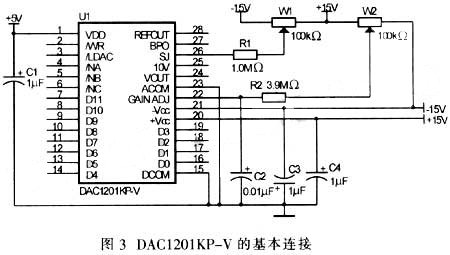

DAC1201KP-V是美国TI公司推出的12位D/A转换器,其引脚排列如图3所示。

DAC1201KP-V采用28引脚DIP封装,逻辑部分采用5V单电源供电,内部含有内部参考,±10V输出运算放大器等电路,具有适合4位、8位、12位和16位总线的微处理器接口逻辑, 外围电路少,接口方便,最大稳定时间只有7μs,对缩短系统开发周期,增强系统可靠性极为有利。

DAC1201KP-V由稳定的壳体表面的参考齐纳二极管、激光调整薄膜梯形电阻和高速电流开关组成的转换器在0℃-70℃范围内可提供极佳的转换性能。模拟输出范围是0V-+10V、±5V和±10V。

当输出电压VOUT1=0-+10V时,数字输入量D为无符号二进制码,计算公式为:

VOUT=(VFSD/4096) (1)

上式中,VOUT是输出模拟量,VFS是满量程,D是待转换的数字量,其中1LSB=VFS/4096=2.44mV。

当输出电压在双极性VOUT=-5V-+5V或VOUT=-10V-+10V之间时,其输入数字量D与输出模拟电压VOUT之间的关系如下:

(VFSD/2048-VFS)/2=VOUT (2)

上式中的定义与单极性输入公式相同。

如果单极性输出从0.0000V变到+9.9976V,数字量的变化为4095,分辨率为9.9976V/4095=2.44mV,若双极性输出从-5.0000V变到+4.9976V,分辨率为9.9976V/4095=2.44mV;双极性输出从-10.0000V变到+9.9976V,分辨率为19.9951V/4095=4.88mV。

DAC1201KP-V的引脚可分为3类。

电源类:逻辑电源VDD接5V电源;数字地DCOM和模拟地ACOM通常共地;+VCC为模拟电源输入+15V或+12V,-VCC为模拟电源输入-15V或-12V,REF OUT 6.3V为参考源输出。

模/数信号类:VOUT为模拟信号输出端,D0-D11为数字并行口。

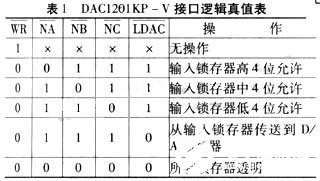

控制信号类:WR写,加载锁存命令信号(与对应锁存信号配合使用);NA半字节A,与WR配合允许加载输入锁存器A(最高有效半字节);NB半字节B,与WR配合允许加载输入锁存器B。NC半字节C,与WR配合允许加载输入锁存器C(最低有效半字节)。上述4个控制信号组成D/A转换器的第一级缓冲即输入锁存。将12位数据暂存在A、B、C3个4位寄存器中,且这3个寄存器采用单独寻址方式,保证不产生虚假的模拟输出值。LDAC加载D/A锁存器,与WR配合允许加载D/A锁存器。WR和LDAC信号组成D/A转换器的第二级缓冲,当12位数据加载入D/A锁存器后即启动D/A转换,所有锁存器真值如表1所示。

GAIN ADJ接外部增益调整,SJ是输出放大器求和端。10V RANGA 10V输出时接VOUT。BPO是双极性偏置(双极性工作时接VOUT)。

3 启动D/A转换的时序分析

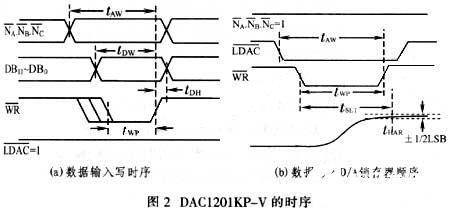

DAC1201KP-V启动转换分2次写入时序,如图2所示。

tWP:WR脉冲宽度,50ns(min);

tAW1:NX和LDAC有效到WR结束;50ns(min);

tDW:数据有效到结束,80ns(min);

tDH:数据有效保持时间,0ns(min);

由时序可见,DAC1201KP-V的双缓冲方式决定了其与微处理器的时序操作非常灵活。

4 接口电路

DAC1201的基本连接如图3所示。

退耦处理:为了得到最佳的性能和噪声抑制,可按图3所示增加电源退耦电容器(1μf-10μF钽电容器),应紧靠DAC1201KP-V。

模拟地与数字地处理,为了实现允许低噪声和高速性能的最佳连接,DAC1201KP-V的ACOM和DCOM应连接在一个点上,若连接正确,这种连接将会使低电平信号通路中的电流减到最小,ACOM和DCOM之间的高频噪声可以通过模拟输出被耦合,因此,在应用这些公共连接点时,需要格外小心。

外部失调和增益调整:腾3中的W1是失调调整;W2是增益调整。

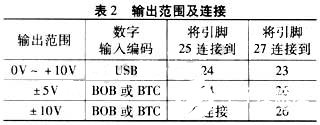

输出范围及连接如表2所示。

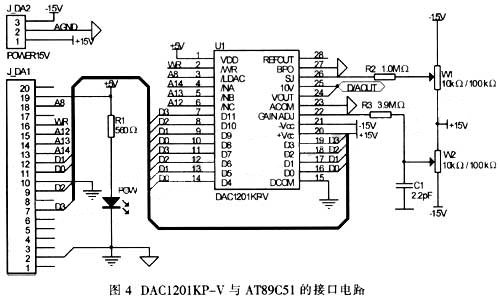

在上述竞赛题目“数控直流电流源”的设计和制作过程中,被控电流源要求0V-+10V的控制信号,DAC1201的信号输出范围选择0V-+10V连接方式,经OP07型运算放大器控制TIP122形成宽带压控电流源。

DAC1201与AT89C51的接口电路如图4所示,图中,DAC1201的第一级缓冲通过3条高位地址线A14(NA)、A13(NB)、A12(NC)配合WR信号控制高、中、低3个半字节加载输入锁存;第二级缓冲通过A8(LDAC)配合WR信号控制加载DAC寄存器后启动转换。

5 程序设计

下面根据图4所示的硬件结构介绍DAC1201KP-V转换软件的实现方法,单片机晶体振荡器的 频率为6.000MHz,入口条件是待转换的数据高8位存于DAH中,低4位在DAL中的高4位,NA地址是BF00H,NB地址是DF00H,NC地址是FF00H,LDAC地址是FE00H。占用资源是A、R0、DAH和DAL、DAOUT连续的3个单元。

汇编语言程序如下:

6 结束语

DAC1201KP-V的分辨率高、转换速度快、接口方便、电路简单、应用灵活,因而具有广泛的应用前景,在指导2005年全国大学生电子设计竞赛的F题“数控直流电流源设计”中利用该电路按图4所示的接线方式取得了很好的控制效果,满足了设计指标的要求。

责任编辑:gt

-

AT89S52单片机实现数控直流电流源论文2022-05-11 964

-

一种闭环智能数控直流电流源的设计原理和实施方案2021-09-27 1098

-

数控直流电流2021-09-15 1008

-

数控直流电流源Protel工程电路原理图及PCB文件2021-08-04 1420

-

使用AT89S51单片机设计数控直流电流源的详细论文资料免费下载2019-08-21 1695

-

基于单片机和TLC549的数控直流电流源的设计2018-02-19 4109

-

程控直流电流源(电子设计大赛论文)2016-07-26 1268

-

数控直流电流源的设计与实现2016-03-29 1192

-

基于AT89C52的数控直流电流源设计方案2011-08-16 12510

-

基于双12位DAC的高精度直流电压/电流源设计2010-01-04 2853

-

语音播报数控直流电流源的设计2009-08-02 490

-

数控直流电流源设计2009-06-19 1914

-

数控直流电流源的设计2009-01-02 2039

全部0条评论

快来发表一下你的评论吧 !