基于DC-DC降压变换器结构电流实现PFM限流比较器的设计

描述

1 引言

近年来,LDO(Low Dropout)线性稳压器和DC/DC 变换器等电源管理芯片已广泛应用于便携式电子系统中 。但是,开关稳压器相对线性稳压器降低了平均输入电流,提高了效率。Step-Down 电源属于DC/DC 变换器中的降压变换器,它的主要缺点是,在轻载时比如手机待机时,静态电流较高,显著降低了电池的使用寿命,所以在低负载条件下,我们通过PFM 限流比较器来控制芯片使之进入Idle 模式,这样就大大延长了电池寿命,提高了芯片的效率。

2 本文采用的DC-DC降压变换器电路结构

本文采用的DC-DC 降压变换器结构采用同步校正器代替传统的二极管,极大地提高了DC-DC 降压变换器的效率,可达到95%左右。芯片的输入电压位于2.7V 至5V 之间,可工作在以下四种模式:固定频率的强制PWM 模式,同步PWM 模式,idle 模式,关断模式。

3 PFM限流比较器的设计

3.1 比较器输入级的设计

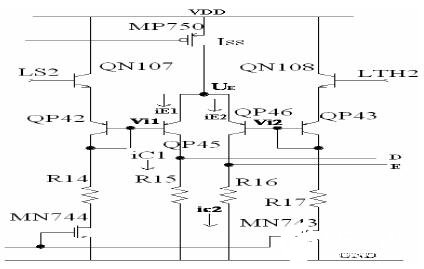

比较器输入级为射级耦合的差分输入级。

图1 比较器的输入级

由上图可知,

(1)

(1)

(2)

(2)

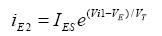

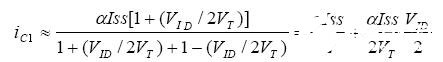

则iC1可以近似为

(3)

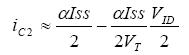

同理

(4)

(4)

可求得差分跨导为:

(5)

(5)

在室温下, T V =26mV , 所以运放跨导等于

(6)

(6)

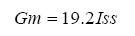

此外,电阻R15,R16作为运放负载,可得出放大器输入级增益表达式如下:

(7)

(7)

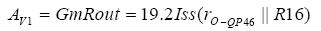

3.2 比较器中间级

比较器中间级由D,E 输入,A 输出。MP724,MP725 的作用是减小A 点电压的变化幅度,使得比较器具有较短的瞬态响应时间和较快的速度。

现在计算折叠共源共栅运放的小信号电压增益,因为|Av|= GmRout ,我们必须计算Gm 和Rout ,而

(8)

(9)

所以, V 2 A 表达式如下:

(10)

图2 比较器中间级

3.3 比较器输出级

比较器的输出级(Active Load inverter)由A 输入,B 输出(图3),进一步提高放大器的增益,

(11)

因此,放大器总的增益AV 表达式如下:

(12)

图3 PFM 限流比较器电路图

3.4 PFM 限流比较器电路图

综合前面比较器输入级,输出级,中间级的设计,可得出图3 所示的PFM 限流比较器电路图。当功率管导通时,对电感电流充电,使得电感电流上升,同时功率管的漏端电压下降,电流采样电路通过采样导通功率管的漏端电压,把采样得到的电压LS2,LTH2 输入到PFM 限流比较器,当功率管的漏端电压下降到一定程度,使得LS2 达到PFM 限流比较器门限LTH2 时,比较器输出高电平至控制逻辑模块,从而使芯片进入PFM 工作模式以延长电池寿命。

4 PFM 限流比较器的仿真

我们采用HSPICE 对图3 所示的电路进行了比较器功能的模拟,由图4 可见当电感电流上升时,采样得到的电压LS2 下降,当功率管的漏端电压下降到一定程度,使得LS2 达到PFM 限流比较器门限LTH2 时,比较器输出高电平至控制逻辑模块,从而使芯片进入PFM工作模式以延长电池寿命。此外,比较器延迟70nS。

图4 PFM 限流比较器的仿真

5 结束语

本文成功地设计出一款应用到DC/DC 芯片上的PFM 限流比较器,并通过HSPICE 进行了仿真。结果表明:电路结构简单,功耗低,响应速度快,完全满足新一代DC/DC 产品的要求,且预计投入市场之后将获得上百万元的效益。

本文作者创新点:本文采用的DC-DC 降压变换器结构采用同步校正器代替传统的二极管,极大地提高了DC-DC 降压变换器的效率,可达到95%左右。基于该DC-DC 降压变换器结构设计了一个新颖的基于Step-Down PWM 电源管理芯片的PFM 限流比较器电路,在轻载时使芯片进入PFM 工作模式,因此能够延长电池寿命并且大幅度的提高Step-DownPWM 电源管理芯片的效率。

责任编辑:gt

-

PL2303 PFM升压 DC-DC 变换器2024-03-26 1294

-

电池驱动系统的DC-DC变换器选择2023-03-03 2608

-

#硬声创作季 闭环降压变换器是如何工作的DC-DC变换器--动画演示Mr_haohao 2022-10-19

-

FS4056 PFM同步升压DC-DC变换器有何特性2021-12-30 1907

-

DC-DC变换器的基本电路2021-11-17 4077

-

推挽正激零电流转换DC-DC变换器的研究与实现2021-08-04 1185

-

工作频率高的 PFM 同步升压 DC-DC 变换器2021-07-08 656

-

什么是DC-DC变换器_DC-DC变换器的工作原理2019-08-01 43639

-

DC-DC变换器拓扑的选用与比较2019-04-08 5884

-

MAX830 在DC-DC变换器中增加可调的限流功能2016-08-18 1942

-

SM9261 PFM 升压 DC-DC 变换器2010-04-13 661

-

降压式DC-DC变换器资料下载2009-10-31 71936

-

在DC-DC变换器中增加可调的限流功能2009-04-30 464

全部0条评论

快来发表一下你的评论吧 !