FPGA入门系列15--SPI总线介绍

电子说

描述

本系列文章主要针对FPGA初学者编写,包括FPGA的模块书写、基础语法、状态机、RAM、UART、SPI、VGA、以及功能验证等。将每一个知识点作为一个章节进行讲解,旨在更快速的提升初学者在FPGA开发方面的能力,每一个章节中都有针对性的代码书写以及代码的讲解,可作为读者参考。

16

第十六章:SPI

SPI简介

电子系统设计中,往往被IIC/SPI/UART等总线搞的晕头转向,本文详细介绍SPI总线的接口协议和应用。

SPI总线是一种同步串行外设接口,它可以使MCU/FPGA/DSP等控制器与各种外围设备以串行方式进行通信。其具有通信速度快,同步设计以及控制协议简单等特点,是电子系统设计的常用选择之一。很多芯片的控制都提供SPI接口。

SPI 是英语 Serial Peripheral Interface 的缩写,顾名思义就是串行外围设备接口。是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,最早由Motorola提出的。由于其简单易用的特性,现在很多的芯片都集成了SPI通信协议。

SPI传输串行数据时首先传输最高位。波特率可以高达5Mbps,具体速度大小取决于SPI硬件。例如,Xicor公司的SPI串行器件传输速度能达到5MHz。

SPI flash 芯片应用十分广泛,在很多电子产品上面或多或少都有它的踪影,如手机、数码、液晶显示器、机顶盒、电脑主板等。主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器等,也是很多复杂芯片参数配置的常用接口。

SPI总线介绍

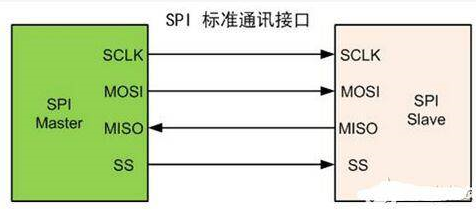

SPI 接口一般使用 4 条线通信,包括片选线(cs_n)、时钟线(sclk/sck)、输入数据线(sdi/miso) 和输出数据线(sdo/mosi):

SCLK:串行时钟线,由主设备产生;

MISO:主设备数据输入,从设备输出;

MOSI:主设备数据输出,从设备输入;

CS:从设备片选信号,由主设备控制。

其中CS是片选信号,可以预先规定其为高使能或者低使能有效时,对此芯片的操作才有效。这就允许在同一总线上连接多个SPI设备。

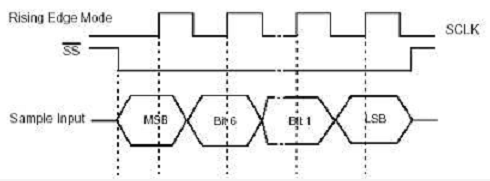

SPI接口在Master控制下产生的从器件使能信号和时钟信号,两个双向移位寄存器按位传输进行数据交换,传输数据高位在前,低位在后(MSB)。在SCK的下降沿数据改变,上升沿一位数据被存入移位寄存器,如图所示:

SPI总线通信特点

1.采用主-从模式(Master-Slave) 的控制方式

SPI 规定了两个 SPI 设备之间通信必须由主设备 (Master) 来控制从设备 (Slave). 一个 Master 设备可以通过提供 Clock 以及对 Slave 设备进行片选来控制多个 Slave 设备。

2.采用同步方式(Synchronous)传输数据

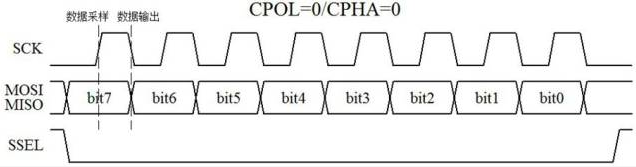

Master 设备会根据将要交换的数据来产生相应的时钟脉冲(Clock Pulse), 时钟脉冲组成了时钟信号(Clock Signal) , 时钟信号通过时钟极性 (CPOL) 和 时钟相位 (CPHA) 控制着两个 SPI 设备间何时数据交换以及何时对接收到的数据进行采样, 来保证数据在两个设备之间是同步传输的。

3.数据交换(Data Exchanges)

SPI设备间的数据传输之所以又被称为数据交换, 是因为 SPI 协议规定一个 SPI 设备不能在数据通信过程中仅仅只充当一个"发送(Transmitter)" 或者 "接收者(Receiver)". 在每个 Clock 周期内, SPI 设备都会发送并接收一个 bit 大小的数据, 相当于该设备有一个 bit 大小的数据被交换了。

SPI FLASH读写介绍

对flash芯片的操作,一般包括对flash芯片的擦除,编程和读取,各大厂商的SPI flash芯片都大同小异,操作命令基本是没什么变化的,当我们拿到一款芯片,要特别注意芯片的容量,操作分区等。

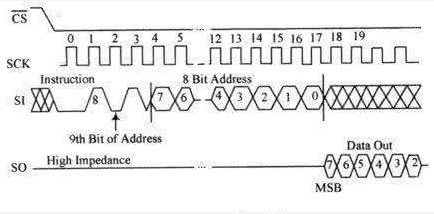

其实,无论是对芯片的擦除,编程还是读取操作,我们大致可以按照以下的套路来:写命令---写地址---写(读)数据。正如以下的时序图一样清晰明了,我们先把片选信号拉低,再依次写指令,地址和数据,就可以对FLASH芯片进行操作。

在第十七章中将通过SPI总线控制Flash为例讲解擦除的实现。

责任编辑:lq

-

STM32CubeMX系列|SPI总线2021-12-22 626

-

SPI总线协议介绍及硬件设计资料分享2021-11-10 1025

-

基于FPGA与MCU通信的SPI协议设计2021-11-05 1160

-

SPI总线介绍2021-08-13 1908

-

怎么使用FPGA实现SPI总线的通信接口?2019-08-09 4666

-

FPGA的高速总线测试和分析的方法与工具介绍2019-07-23 5998

-

SPI总线简介与参考实例2015-11-19 921

-

SPI总线协议介绍2012-08-18 19156

-

一种通用SPI接口的FPGA设计与实现2011-09-09 857

-

SPI接口总线介绍2010-11-24 5230

-

数字接口系列文章之SPI总线2010-01-08 1227

全部0条评论

快来发表一下你的评论吧 !